方案概述

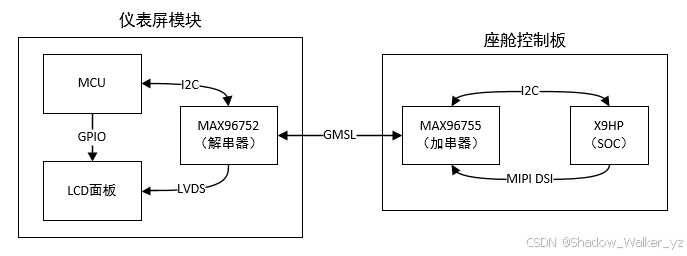

视频信号从SOC的MIPI DSI接口输出,经过MAX96755加串器转为GMSL信号从控制板输出到屏模块。控制信号从SOC的I2C接口输出,可直接与MAX96755通信,经过MAX96755透传还可与屏模块的MAX96752解串器通信,经过MAX96752透传还可与屏模块的MCU通信。MAX96752会将GMSL信号转为LVDS信号供LCD面板显示。MCU会通过一个GPIO输出PWM来控制LCD背光,SOC只需通过I2C给MCU发送背光控制指令即可。方案架构图如下图所示:

因此,智能座舱仪表屏驱动分为以下几部分:

| 驱动名称 | 注释 |

| Linux I2C主机驱动 | 芯驰已实现,只需配置设备树 |

| Linux MIPI DSI驱动 | 芯驰已实现,只需配置设备树 |

| Linux I2C设备驱动(MAX96755,MAX96752) | 需要根据供应商提供的demo移植 |

| Linux I2C设备驱动(MCU) | 需要根据供应商提供的I2C协议实现背光控制 |

MIPI DSI协议简介

关于MIPI DSI协议,可参考下面几篇文章,讲得比较清楚:

液晶接口系列——MIPI之DSI协议讲解_mipi dsi 时序图-CSDN博客

液晶接口系列——MIPI之DSI时钟的计算和常见概念区分_mipi ui是什么-CSDN博客

液晶接口系列——MIPI(三)DSI时序讲解与实际测试_dsi lanes set to lp-11-CSDN博客

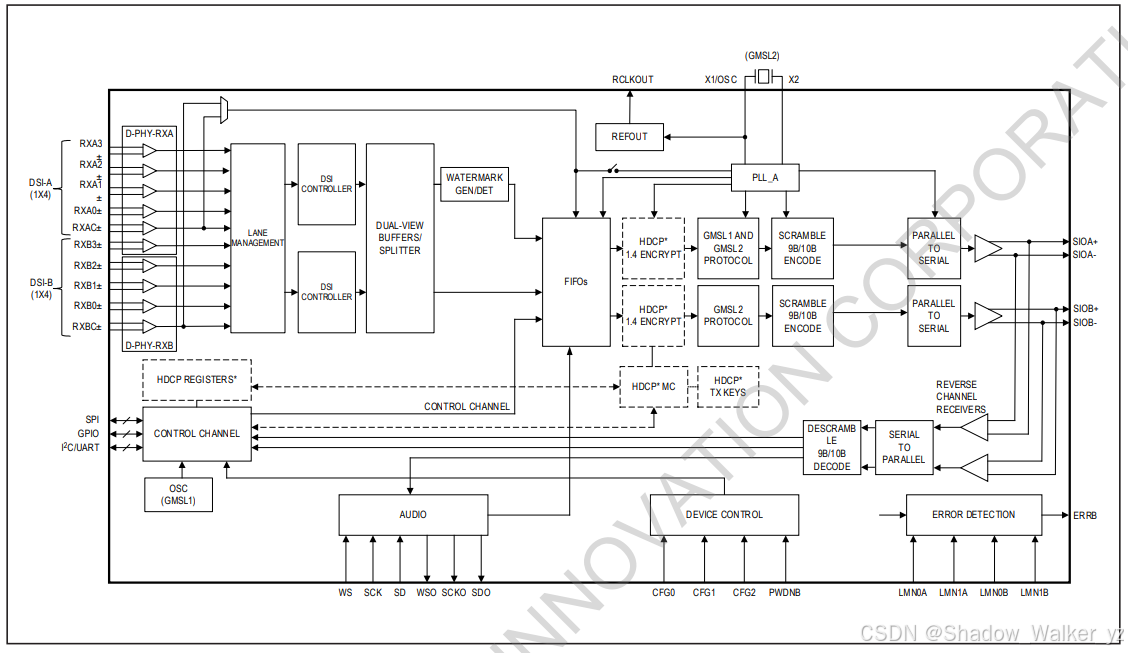

MAX96755简介

模块图如下所示:

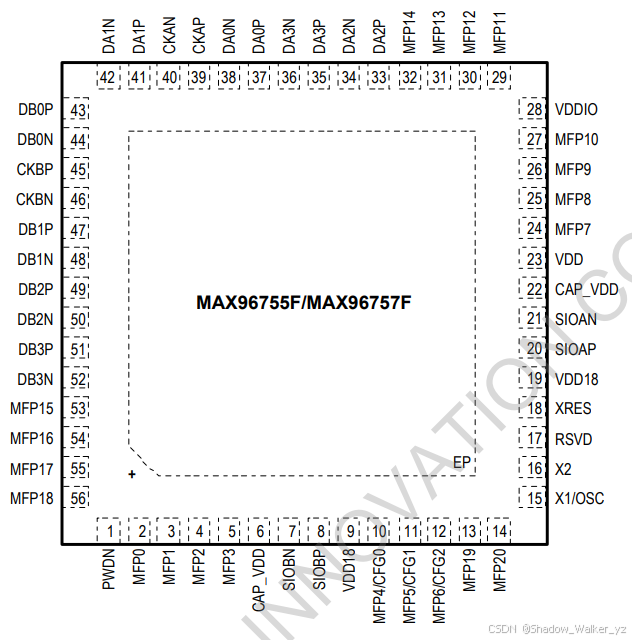

引脚图如下所示:

引脚图如下所示:

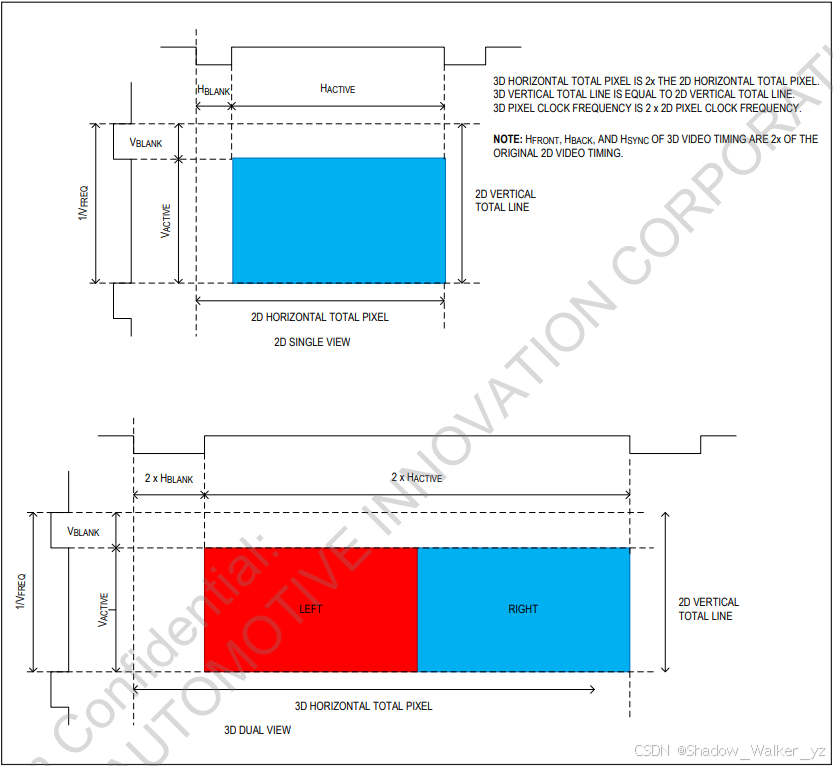

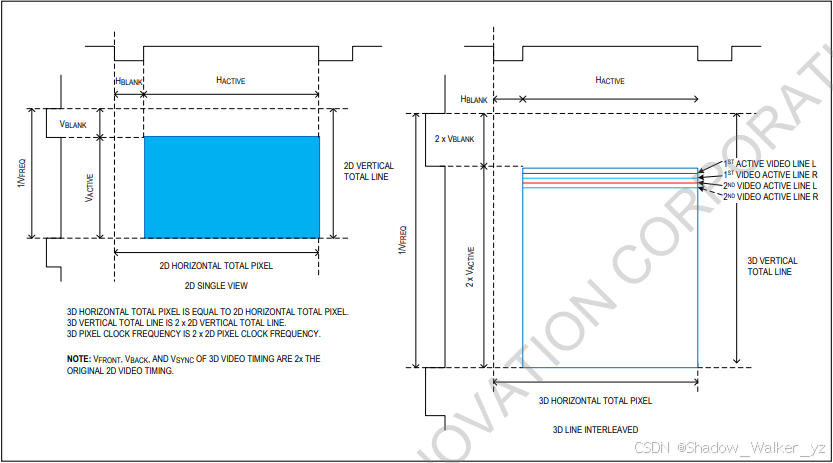

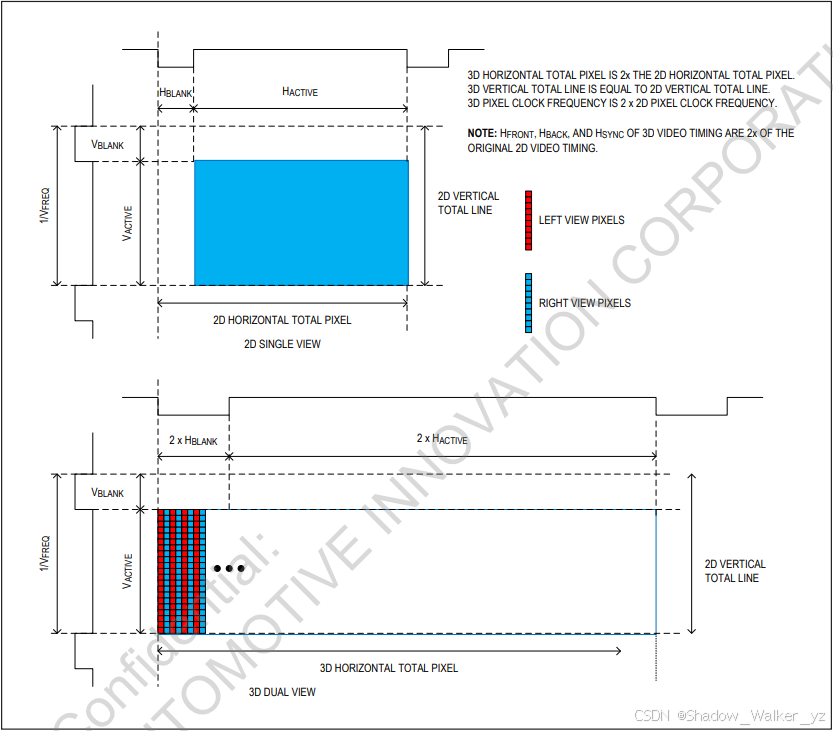

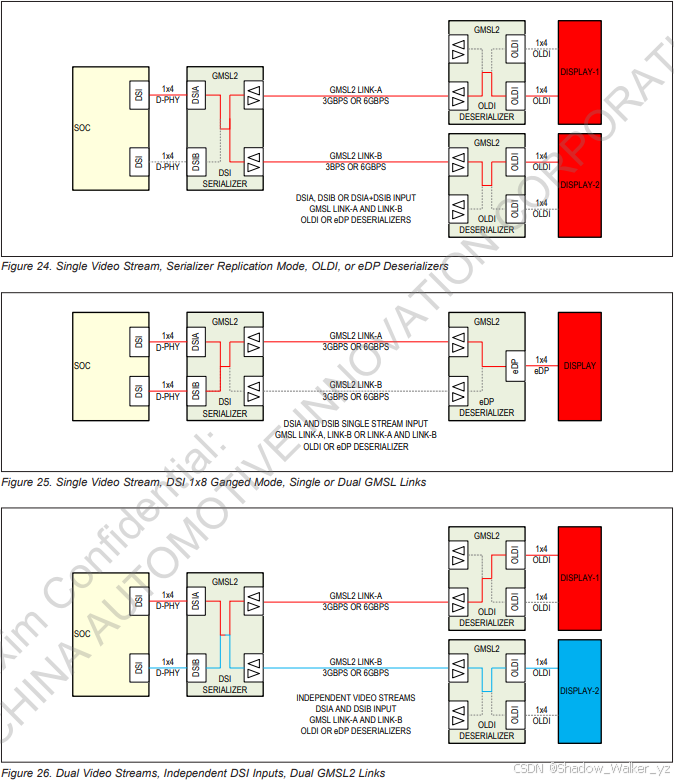

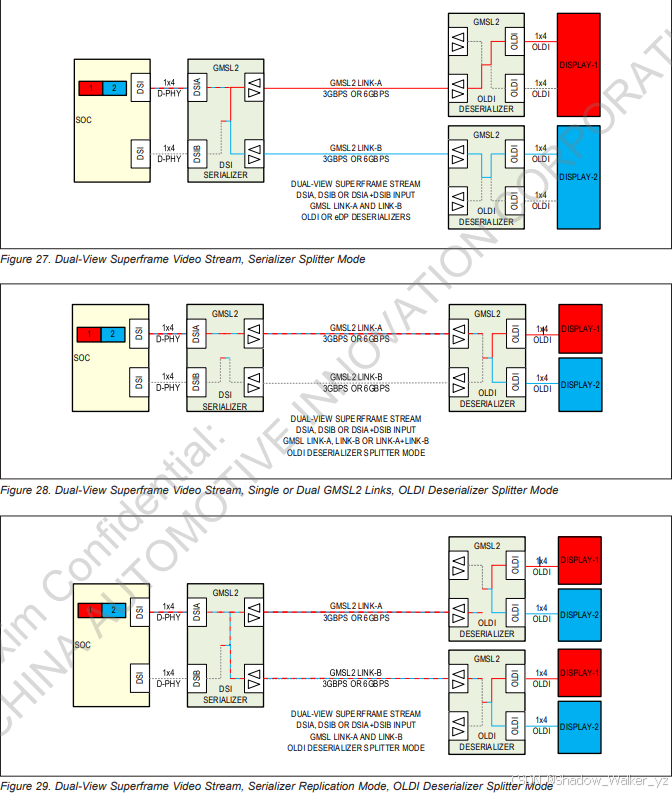

MAX96755可以接收单视频流也可以同时接收两个视频流,接收两个视频流的时候可以以不同的模式显示,如下面几张图所示:

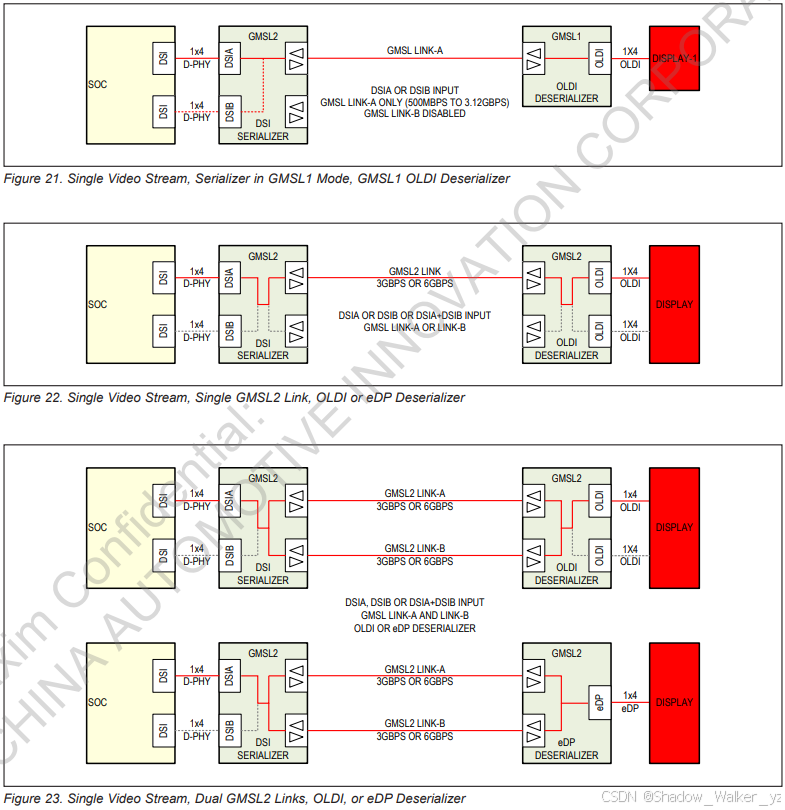

MAX96755可以工作在不同的模式以适应不同的应用场景,具体如下面几张图所示:

加串器(MAX96755)和解串器(MAX96752)的初始化

| 序号 | 芯片 | 寄存器地址 | 读/写 | 值 | 注释 |

| 1 | MAX96755 | 0xd | 读 | N.A. | ① 读取MAX96755的ID。 |

| 2 | MAX96755 | 0x1 | 写 | 0xc4 | ① 使能I2C透传功能。SOC的I2C引脚连接在MAX96755的I2C引脚上,SOC作为I2C主机,因此SOC可以和MAX96755通过I2C进行通信。那SOC如何跟屏模块中的MAX96752和MCU通信呢?这就要使能I2C透传功能,将I2C信号融合到GMSL信号中透传出去,这样MAX96752以及连接在MAX96752上的MCU就能接收到SOC发出的I2C信号了。 ② I2C引脚连接到控制模块。与MAX96755直连的I2C主机和通过GMSL通道间接连接的I2C主机都可以与其通信来操作MAX96755内部的控制模块以对芯片进行各种配置。在多主机的情况下,根据实际需求可以关闭MAX96755的I2C引脚与内部控制模块的连接来防止冲突。在本项目中,这是不需要的,保持连接开启。 ③ GMSL通道连接到控制模块。含义与②类似,只是针对的是GMSL通道。在本项目中,这是不需要的,保持连接开启。 ④ 设置发送速率为3Gbps。 |

| 3 | MAX96755 | 0x330 | 写 | 0x4 | ① 配置为两个MIPI接收port,每个port有4个lane(一组差分接收引脚为一个lane),并且只使能A port,因为本项目SOC连接到了A port。 |

| 4 | MAX96755 | 0x10 | 写 | 0x21 | ① 禁用link自动配置。 ② 选择link A,因为本项目中解串器连接到了加串器的GMSL link A上。 ③ 复位data path(保留寄存器配置)。 |

| 5 | MAX96752 | 0x1 | 写 | 0x1 | ① 设置接收速率为3Gbps。 |

| 6 | MAX96752 | 0x1ce | 写 | 0x47 | ① 将输出信号设为VESA格式。oLDI格式和VESA格式都是基于LVDS(低压差分信号)的视频信号。 |

| 7 | MAX96752 | 0xe | 读 | N.A. | ① 读取MAX96752的ID。 |

| 8 | MAX96752 | 0x10 | 写 | 0x21 | ① 禁用link自动配置。 ② 选择link A,因为本项目中加串器连接到了解串器的GMSL link A上。 ③ 复位data path(保留寄存器配置)。 |

| 9 | MAX96755 | 0x1c8 | 写 | 0x83 | ① 设置输出帧同步信号VS。 |

| 10 | MAX96755 | 0x10 | 写 | 0x21 | ① 禁用link自动配置。 ② 选择link A,因为本项目中解串器连接到了加串器的GMSL link A上。 ③ 复位data path(保留寄存器配置)。 |

| 11 | MAX96752 | 0x1cf | 写 | 0x9 | ① 使能展频。展频是硬件中的术语,用于降低电磁干扰。 |

| 12 | MAX96755 | 0x380 | 写 | 0b00xxxxxx | ① 将MIPI DSI接口的模式设置为使用同步脉冲的非突发模式。Sync pulses 是一种通过脉冲信号来同步视频数据的方式。这些脉冲信号在视频帧的开始和结束时出现,以指示数据传输的边界。Sync events 是一种基于事件触发的同步方式,与 sync pulses 不同,它不依赖于固定的脉冲信号,而是通过检测特定的事件(如帧开始、帧结束等)来同步视频数据。 |

| 13 | MAX96755 | 0x385 | 写 | (根据屏幕参数设置) | ① 设置行同步信号HS宽度的低8位。 |

| 14 | MAX96755 | 0x386 | 写 | (根据屏幕参数设置) | ① 设置帧同步信号VS宽度的低8位。 |

| 15 | MAX96755 | 0x387 | 写 | (根据屏幕参数设置) | ① 设置行同步信号HS和帧同步信号VS宽度的高4位。 |

| 16 | MAX96755 | 0x3a5 | 写 | (根据屏幕参数设置) | ① 设置与帧同步信号VS相关的VFP参数的低8位。 |

| 17 | MAX96755 | 0x3a7 | 写 | (根据屏幕参数设置) | ① 设置与帧同步信号VS相关的VBP参数的高8位。 |

| 18 | MAX96755 | 0x3a6 | 写 | (根据屏幕参数设置) | ① 设置VFP参数的高4位和VBP参数的低4位。 |

| 19 | MAX96755 | 0x3a8 | 写 | (根据屏幕参数设置) | ① 设置垂直方向像素点数的低8位。 |

| 20 | MAX96755 | 0x3a9 | 写 | (根据屏幕参数设置) | ① 设置垂直方向像素点数的高8位。 |

| 21 | MAX96755 | 0x3aa | 写 | (根据屏幕参数设置) | ① 设置与行同步信号HS相关的HFP参数的低8位。 |

| 22 | MAX96755 | 0x3ac | 写 | (根据屏幕参数设置) | ① 设置与行同步信号相关的HBP参数的高8位。 |

| 23 | MAX96755 | 0x3ab | 写 | (根据屏幕参数设置) | ① 设置HFP参数的高4位和HBP参数的低4位。 |

| 24 | MAX96755 | 0x3ad | 写 | (根据屏幕参数设置) | ① 设置水平方向像素点数的低8位。 |

| 25 | MAX96755 | 0x3ae | 写 | (根据屏幕参数设置) | ① 设置水平方向像素点数的高8位。 |

| 26 | MAX96755 | 0x389 | 写 | 0bxxx1xxxx | ① 配置控制器0不需要发送端发送EOTP包。EOTP包是MIPI DSI协议中的一种数据包,用于表示高速模式传输即将结束。 |

| 27 | MAX96755 | 0x3a4 | 写 | 0xc3 | ① Select the skewed DE and DOUT output from the DSI controller. ② 使能DPI Deskew,它被用于解决时钟 lane与数据lane间相位差问题,确保高速数据传输的准确性。 |

| 28 | MAX96755 | 0x399 | 写 | 0bxxx1xxxx | ① 配置控制器1不需要发送端发送EOTP包。EOTP包是MIPI DSI协议中的一种数据包,用于表示高速模式传输即将结束。 |

| 29 | MAX96755 | 0x330 | 写 | 0x4 | ① 配置为两个MIPI接收port,每个port有4个lane(一组差分引脚为一个lane),并且只使能A port,因为本项目SOC连接到了A port。 |

| 30 | MAX96755 | 0x331 | 写 | 0x73 | ① 为port A和port B选择4个lane。 |

| 32 | MAX96755 | 0x308 | 写 | 0x7c | ① 使能line start information frame。 ② 使能port A和port B。 ③ port A使用视频管道X和Y,port B使用视频管道U和Z。 |

| 33 | MAX96755 | 0x2 | 写 | 0x13 | ① 使能视频管道X,禁用视频管道U、Z、Y。 |

| 34 | MAX96755 | 0x311 | 写 | 0x1 | ① 开启视频管道X中来自port A的视频传输。 |

| 35 | MAX96755 | 0x53 | 写 | 0x10 | ① 设置视频管道X的视频流ID为0。 |

MIPI DSI接口的初始化

MIPI DSI接口由于在SOC内部,因此驱动代码芯驰已经写好了,我们要做的就是根据屏幕参数进行一些配置,具体如下表:

| 配置项 | 值 | 注释 | |

| dp_res | 1 | DP为display processor的简称,它可以通过自身的硬件进行一些图形运算。芯驰X9HP有3个DP,值”1“表示选择第二个DP。 | |

| dc_res | 1 | DC为display controller的简称,它可以通过自身的硬件进行一些图形运算,功能比DP要弱一些。芯驰X9HP有4个DC,值”1“表示选择第二个DC。 | |

| if_res | 2 | 选择视频接口,值”2“表示使用第二个MIPI DSI接口,这个要根据原理图确定。 | |

| pixel_bpp | 2 | 像素格式,如RGB888、RGB565等等,值”2“表示选择RGB888格式,因为本项目的液晶屏使用RGB888格式。 | |

| width_mm | 292 | 屏幕宽度为292mm。 | |

| height_mm | 109 | 屏幕高度为109mm。 | |

| fps | 60 | 帧率设为每秒60帧。 | |

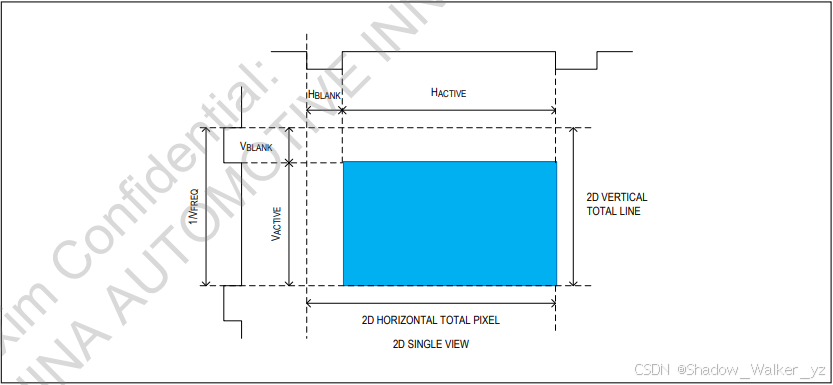

| display_timing | hactive | 1280 | 本项目使用的液晶屏水平方向有1280个像素点。 |

| hfront_porch | 56 | 本项目使用的液晶屏HFP参数(参见RGB显示接口时序)为56个时钟周期。 | |

| hback_porch | 26 | 本项目使用的液晶屏HBP参数(参见RGB显示接口时序)为26个时钟周期。 | |

| hsync_len | 6 | 本项目使用的液晶屏行同步信号的宽度为6个时钟周期。 | |

| vactive | 720 | 本项目使用的液晶屏竖直方向有720个像素点。 | |

| vfront_porch | 12 | 本项目使用的液晶屏VFP参数(参见RGB显示接口时序)为12个显示一行所需的时间。 | |

| vback_porch | 10 | 本项目使用的液晶屏VBP参数(参见RGB显示接口时序)为10个显示一行所需的时间。 | |

| vsync_len | 10 | 本项目使用的液晶屏帧同步信号宽度为10个时钟周期。 | |

| pll_clk | 413000000 | 此值是使用芯驰提供的工具根据hactive、hfront_porch、hback_porch、hsync_len、vactive、vfront_porch、vback_porch、vsync_len、fps计算出来的,具体什么意思不用纠结,如果是别的微处理器没有这个参数。这里重点是掌握像素时钟和MIPI DSI位时钟的计算方法,参考《液晶接口系列——MIPI之DSI时钟的计算和常见概念区分_mipi ui是什么-CSDN博客》。 | |

| mipi | burst_mode | 2 | 设置MIPI DSI传输模式为burst模式,三种传输模式参考《液晶接口系列——MIPI之DSI协议讲解_mipi dsi 时序图-CSDN博客》。 |

| video_bus_width | 24 | 表示一个像素使用的位数,由于本项目使用的液晶屏是RGB888格式的,所以表示一个像素就要用24位。 | |

| lane_number | 4 | 使用4个lane(一组差分引脚为一个lane)传输图像数据。 | |

关于显存

存储一帧或者多帧图像像素数据的RAM就是显存,它可以放在微处理器的外部RAM中,也可以放在内部RAM中。显示控制器会从显存中读取像素数据,并通过MIPI DSI接口发出,这样一帧帧的图像就在液晶屏上显示出来了。需要配置显示控制器的相关寄存器来告诉它显存的基地址在哪。在Linux中,芯片厂商已经将显示控制器的驱动写好了,我们只需在设备树中配置显存的物理地址和大小即可。驱动会生成一个帧缓冲设备(命名类似于/dev/fb0之类的),在应用程序中操作这个设备文件即可访问显存。

436

436

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?