CP2102N-A02-GQFN28学习笔记

一、概述

1.芯片介绍

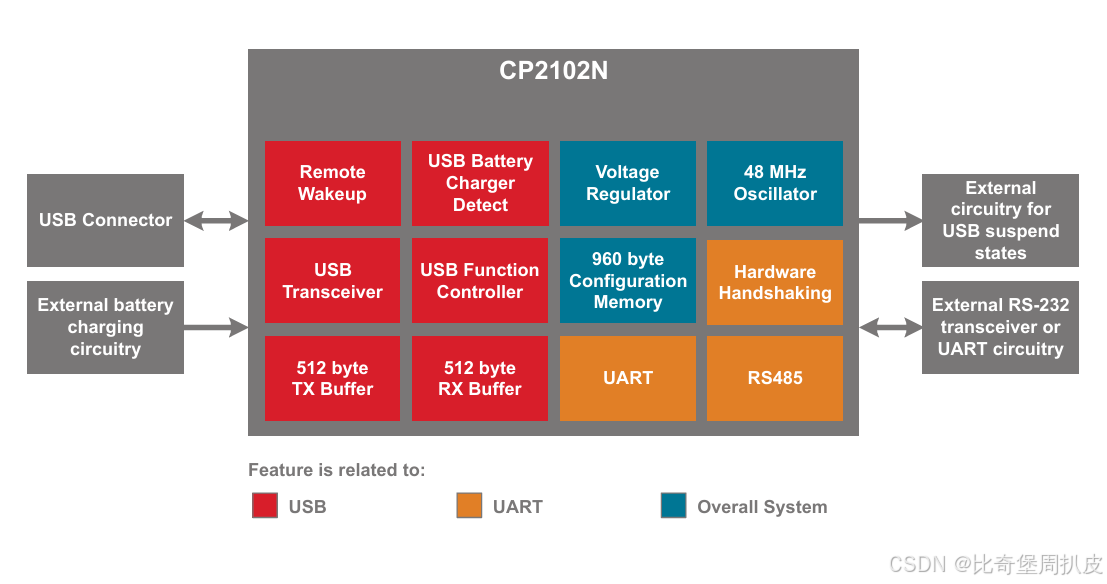

CP2102是高度集成的USB至UART桥接控制器。

CP2102 / 9包括一个USB 2.0全速功能控制器,USB收发器,振荡器,EEPROM或EPROM,以及具有完整调制解调器控制信号的异步串行数据总线(UART),采用紧凑的5 x 5 mm QFN-28封装。

注意:全速的USB控制器支持速率最高到12Mbps,高速的才会支持到480Mbps。

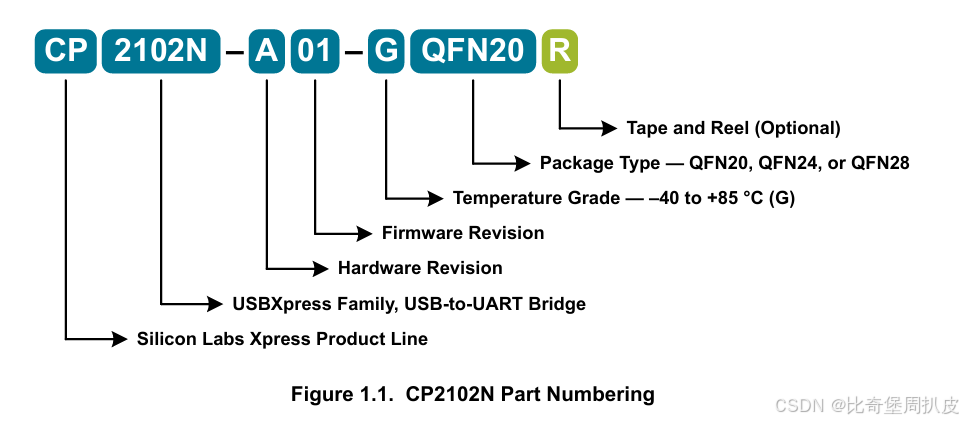

2.芯片命名规则

主要研究 CP2102N- A02-GQFN28

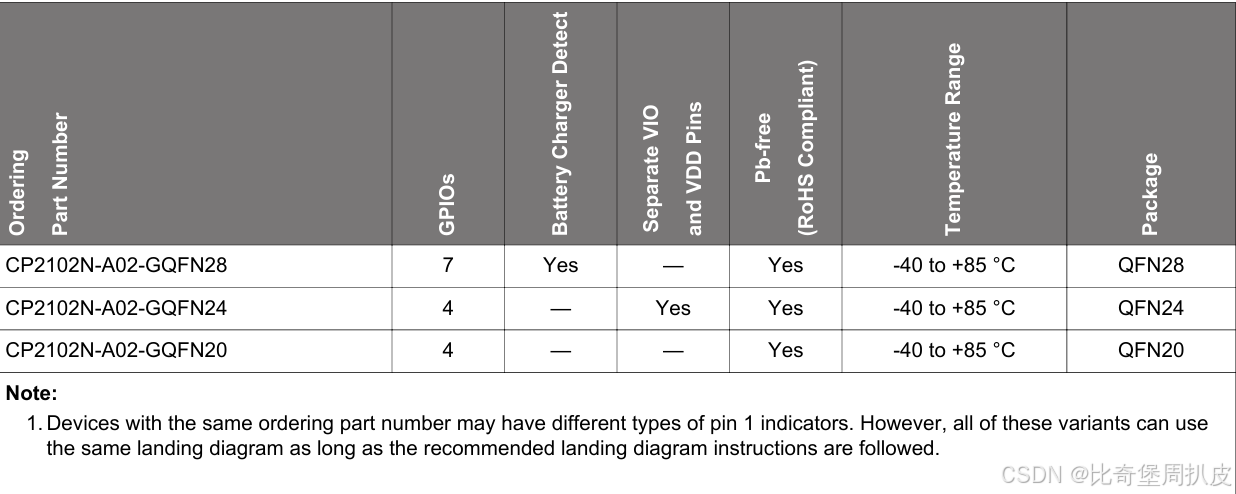

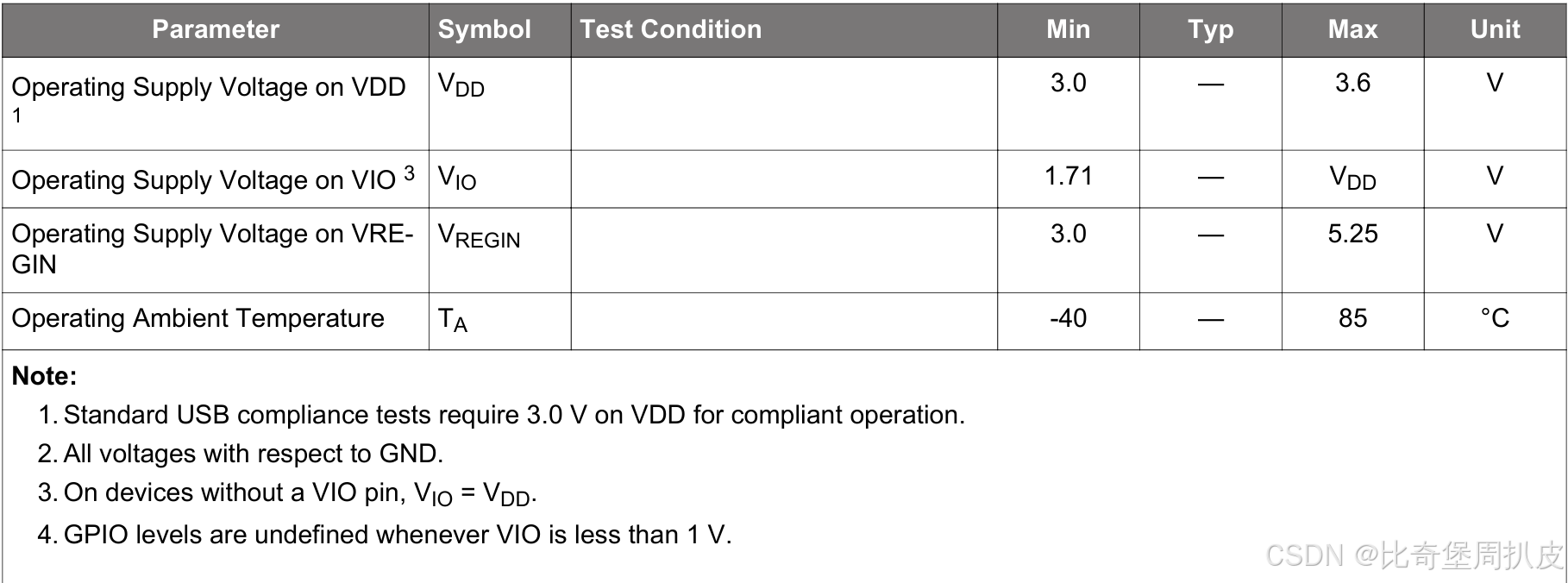

3.电气特性以及操作条件

(1)推荐运行条件

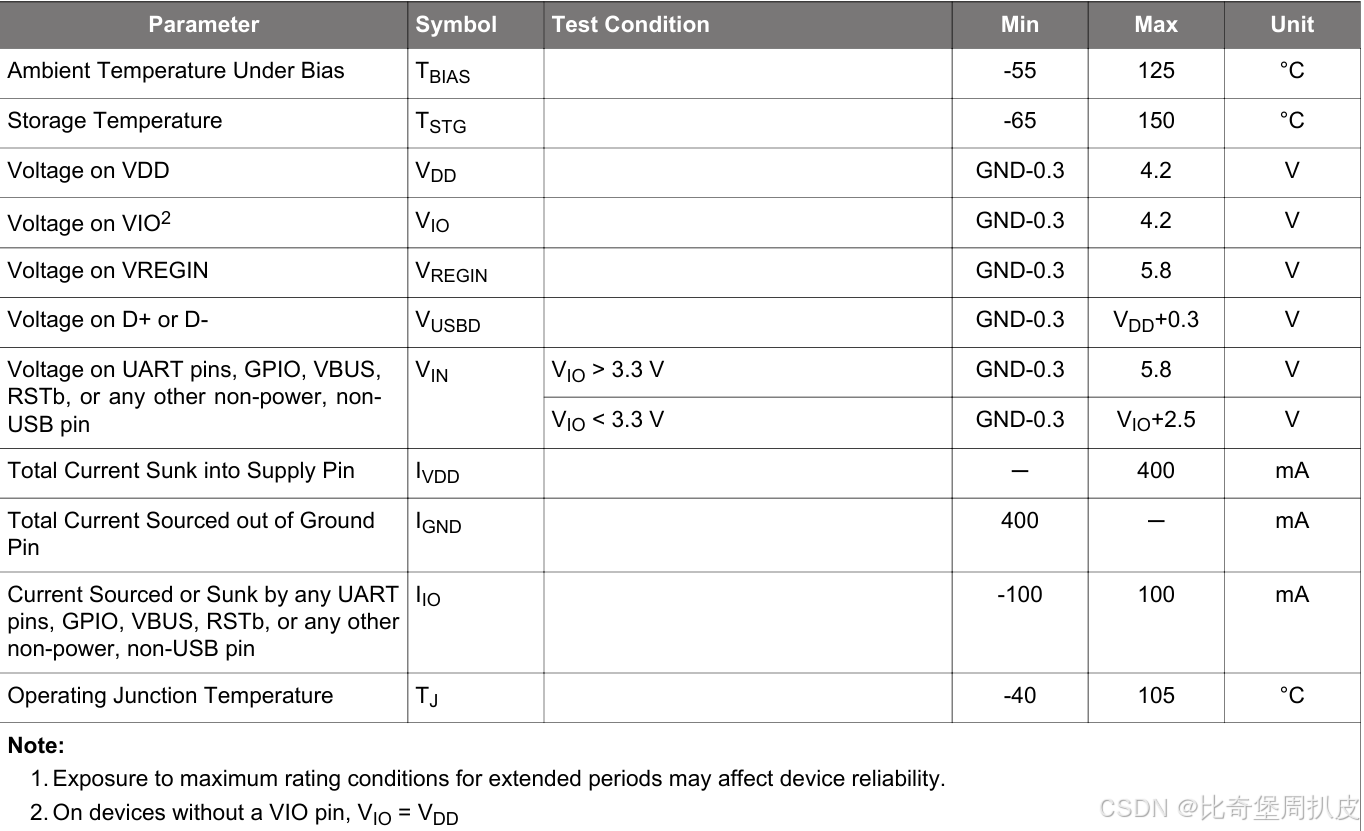

(2)极限最大条件

VDD引脚最大电压4.2V,Vbus引脚最大5.8V,一旦超过将会损坏芯片。这一点在设计供电电压尤其需要注意。

二、功能描述

USB的 挂起功能

当检测到suspend信号时,USB进入挂起状态。

出现以下四种情况后,可以退出挂起模式:

1)恢复信号被检测到或者生成。

2)检测到USB Reset信号。

3)设备重置发生。

4)USB远程唤醒功能启用,Wakeup引脚接地。

在CP2102复位期间,suspend和suspendb两个引脚都会暂时浮在高位,可以用一个10千欧的强下拉电阻,使suspendb保持低电平。

三、引脚描述

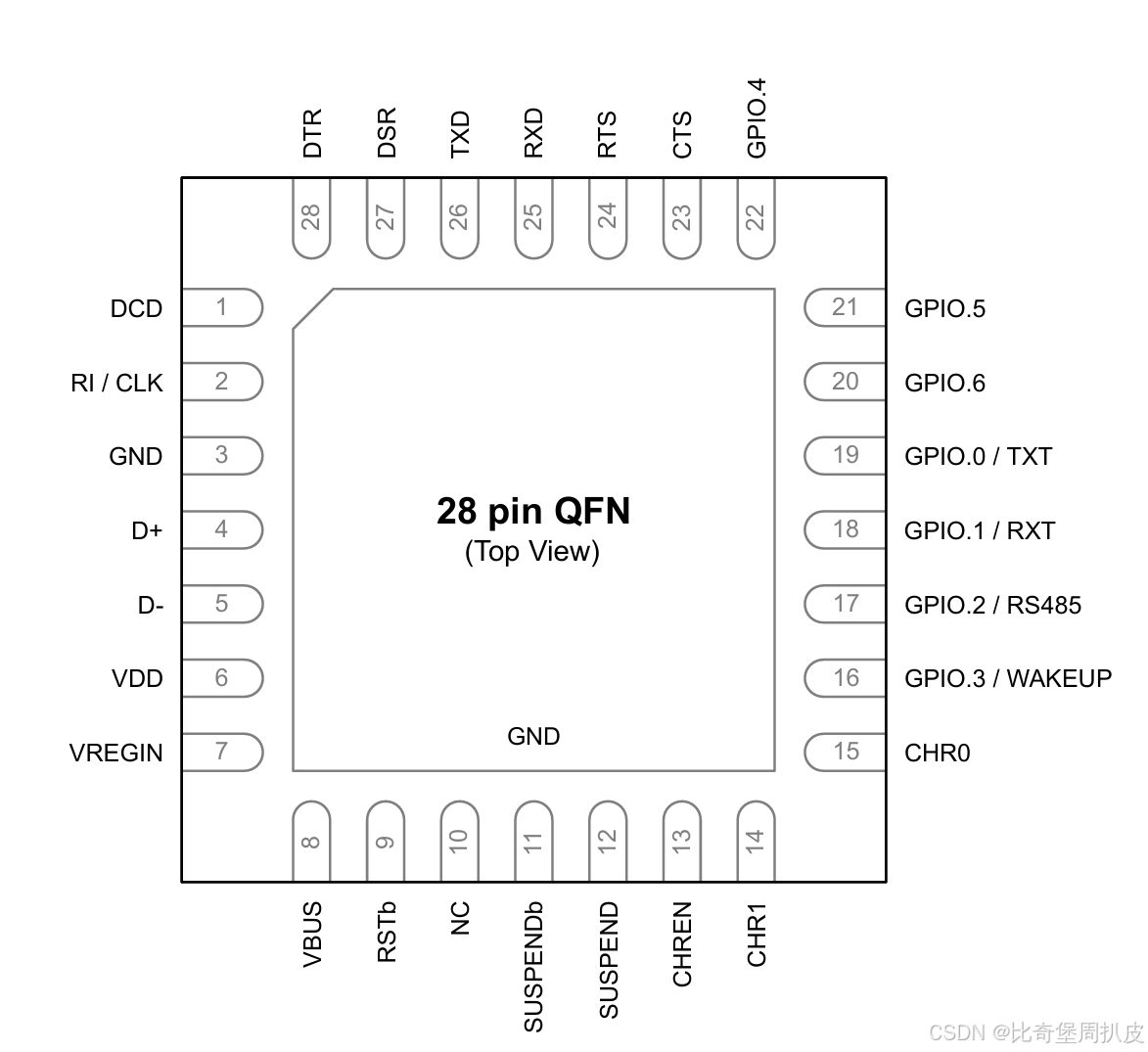

CP2102N QFN28封装 引脚定义图

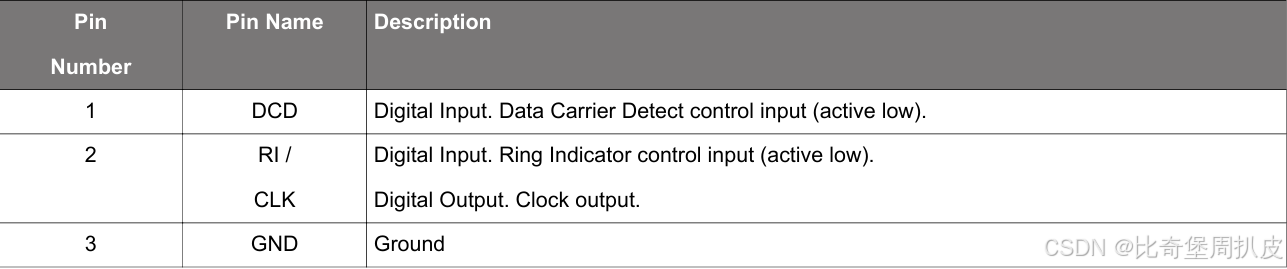

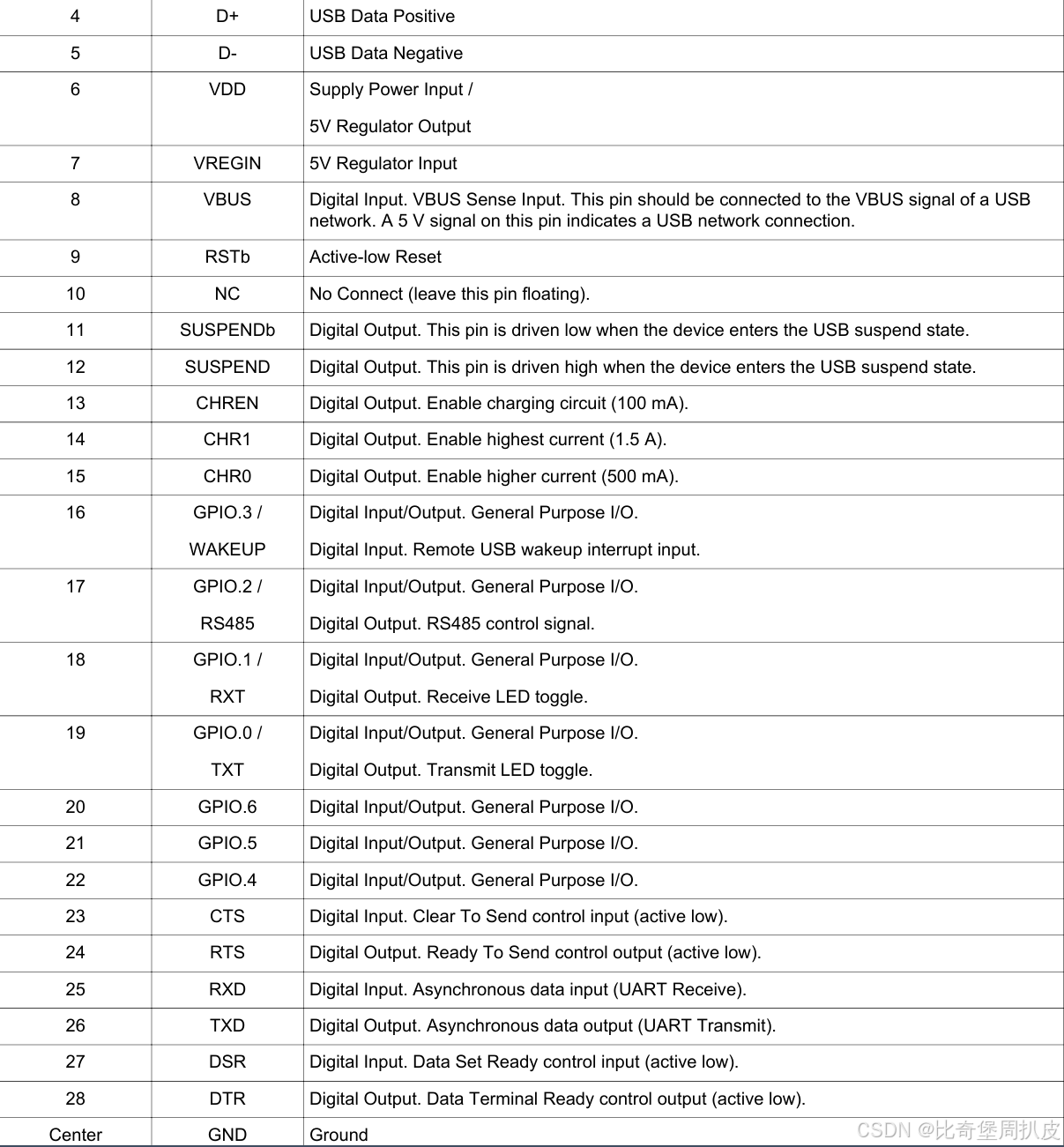

引脚定义表格

引脚4-5 D+ D-

D+与D-为USB接口引脚。与USB连接器上的D+和D-相连接 。

D+也写作DP(positive)。D-也写作DN(negative)。

引脚6 VDD

VDD外接3.3V电即可

引脚 7 Vregin

不使用5V稳压器,Vregin直接接到VDD上。

引脚 8 Vbus

应该与USB网络上的Vbus相连,能检测到5V信号,则证明连接成功。

引脚 9 RSTb

复位引脚,需要上拉1kohm电阻。

引脚11 Suspendb

USB工作状态检测引脚,当设备处于挂起状态时,此引脚将被置为低电平。

但在CP2102复位期间,suspend和suspendb两个引脚都会暂时浮在高位,

可以用一个10千欧的强下拉电阻,使suspendb保持低电平。

引脚25-26 TXD RXD

UART的接收与发送,与主控设备上的串口TXD RXD相连接。

引脚 23-24 RTS CTS

RTS和CTS引脚:RTS和CTS是与硬件流控相关的引脚。

什么是硬件流控:硬件流控(Hardware Flow Control)是串口通信中一种控制数据传输的机制,

主要通过控制信号(如RTS和CTS)来管理数据的发送与接收。

RTS(Request to Send):发送方(如计算机或设备)请求发送数据。

如果RTS信号为低电平,表示发送方准备好数据传输。

如果RTS信号为高电平,则表示发送方不准备发送数据,直到接收方准备好接收数据。

CTS(Clear to Send):接收方(如ESP32)表示是否可以接收数据。

如果CTS信号为低电平,表示接收方准备好接收数据。

如果CTS信号为高电平,表示接收方不能接收数据,发送方需要等待。

连接方式:RTS (CP2102) -> CTS (主控)

CTS (CP2102) -> RTS (主控)

RTS和CTS引脚只有在高速通信、长距离通信、长期通信等特殊环境下才用到,普通的程序烧录一般不会用到。

引脚27-28 DTR DSR

尚未可知 等待补充

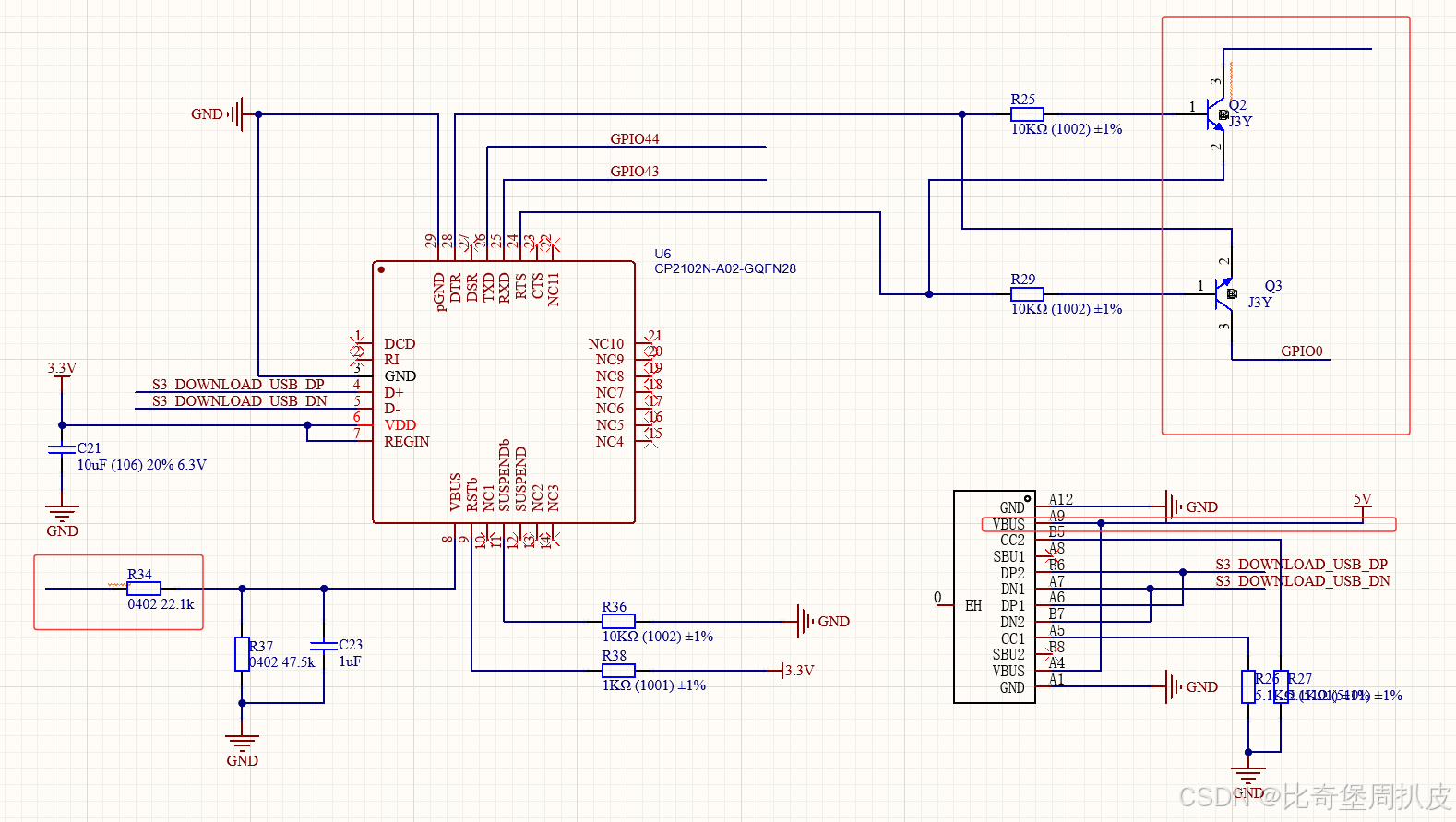

四、原理图绘制

还有部分纰漏 会修补

3100

3100

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?