Ref.

1. CMOS VLSI Design: A Circuits and Systems Perspective

目录

0 基础

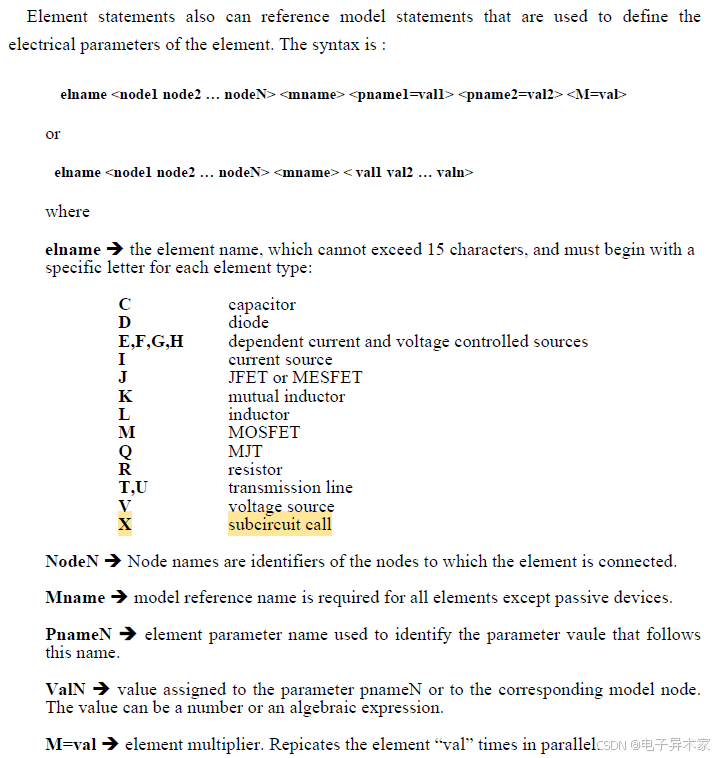

- .SUBCKT 电路语句格式

- 为了维护方便,采用子电路模式定义门电路所使用的MOS管,便于统一管理和更改

.subckt nch d g s b w=130e-9 l=65e-9

main d g s b nn w="w" l="l"

.modle nn.1 noms(version=4.7 level=54 lmin=1n lmax=20u wmin=1n wmax=1u)

.modle nn.2 noms(version=4.7 level=54 lmin=1n lmax=20u wmin=1n wmax=100u)

.end- 调用子电路使用x

pch的定义类似

因此后续使用时顺序均为 d g s b 的顺序

1 反相器 inverter

.subckt inv a y

x1 y a vdd vdd pch

x2 y a vss vss nch

.ends2 缓存器 buffer

两个inv连接在一起即可构成buffer

.subckt buf a y

x1 a n inv

x2 n y inv

.ends3 NAND

.subckt nand a b y

x1 y a vdd vdd pch

x2 y b vdd vdd pch

x3 y a n vss nch

x4 n b vss vss nch

.ends4 NOR

.subckt nor a b y

x1 y a n vdd pch

x2 n b vdd vdd pch

x3 y a vss vss nch

x4 y b vss vss nch

.ends5 传输门 Transmission gate

首先介绍传输管。由于单个传输管存在消弱电平的现象,因此不单独使用,往往将两个互补的传输管组成传输门使用。

· 以下是传输门电路。

.subckt Tgate a e eb y

x1 a eb y vdd pch

x2 a e y vss nch

.ends6 三态反相器 Tristate Inverter

.subckt Tinv a e eb y

x1 n1 a vdd vdd pch

x2 y eb n1 vdd pch

x3 y e n2 vss nch

x4 n2 a vss vss nch

.ends7 选择器 Multiplexers

.subckt InvMUX D0 D1 s sb y

x1 D0 sb s y Tinv

x2 D1 s sb y Tinv

.ends可以进一步组合得到4:1选择器

8 D锁存器 D Latch

.subckt DLatch d clk qb

x1 clk clkq inv

x2 D0 clk clkq q Tgate

x3 q qb inv

x4 qb n inv

x5 n clkq clk q Tgate

.ends9 D触发器 D Flip-Flop

两个锁存器组在一起就是触发器了。

.subckt DFF d clk q

x1 clk clkb inv

x2 d clkb qmb DLatch

x3 qmb clk q DLatch

.ends

332

332

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?