专栏文章目录传送门:返回专栏目录![]()

目录

Linux PCIe 简单介绍(一)

本文将开始介绍有关PCIE相关的知识,将会分成好几个章节进行从浅入深,加上实践相关进行去说说PCIE的相关知识,最终目的了解PCIE的整个流程,还有在我们遇到对PCIE设备的驱动该如何去调试,应该注意哪些问题。

本章主要讲解认识下PCIE的相关发展历史,一些概念等等;

1.初识PCIe接口

在早期计算机时代,不同厂商和不同计算机架构采用了各自的专有总线标准。这导致了设备之间的互通性问题,增加了设备开发和维护的成本。 为了解决这一问题,计算机硬件厂商意识到需要一种通用的、标准化的总线接口,以便设备能够在不同计算机系统中通用。 在1992年,Intel公司领导下的联盟(包括Compaq、DEC、IBM、Microsoft等)共同制定了PCI标准。PCI使用并行传输方式,能够提供高带宽和低延迟,从而在当时的计算机中成为一种主流总线标准。

随着计算机性能的不断提高,虽然PCI在当时非常流行,但是却逐渐发现速度限制和复杂度问题,于是后面就出现了PCIe,PCIe是在2003年出现,主要不一样采用了串行方式,取代了并行传输PCI,从而大大提高了数据传输数率和总带宽。可以简单说明下PCIe就是PCI的一次升级,PCIe英文全称Peripheral Component Interconnect Express。

2. PCIe 版本区别

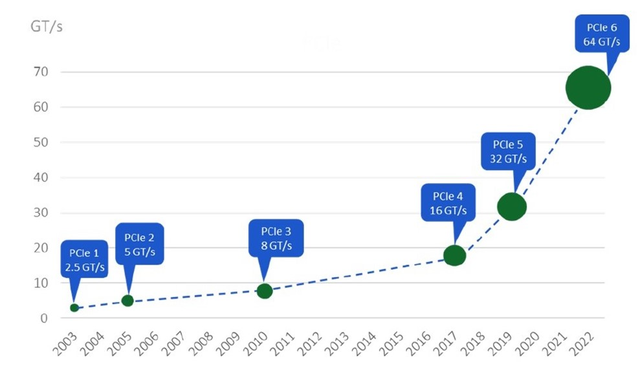

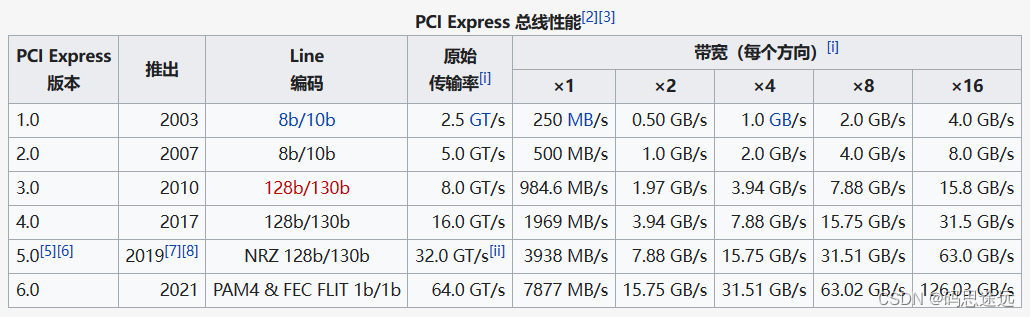

第一个PCIe的1.0版本在2003 年发布,传输速率为2.5G/s,然而到2023年目前为止,PCIe已经迭代了很多个版本,每一次的升级都是速率更加高。最近AI的智能的发展,受到自动驾驶等行业影响,PCIe将会越来越强。目前最新版本是PCIe6.0, 下一个版本在官网提到将在2025年发布,速率将会翻倍提供到128G/s速率。

2.1 PCIe物理接口

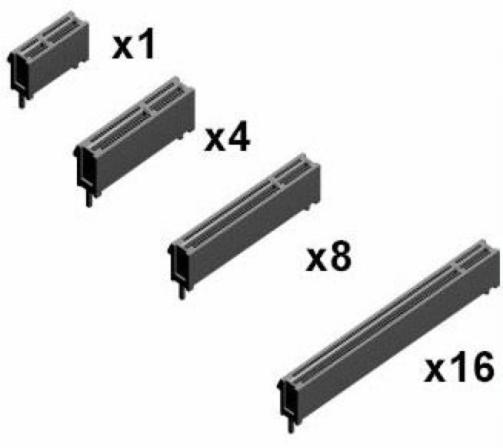

PCIe物理接口有不同尺寸,表示通过该插槽的通道数量,用于连接不同带宽的PCIe设备。常见的物理插槽尺寸包括:

-

PCIe x1:包含一个通道,通常用于连接低带宽的设备,如网卡、声卡等。

-

PCIe x4:包含四个通道,提供更大的带宽,适用于连接一些需要高速数据传输的设备。

-

PCIe x8:包含八个通道,适用于一些需要更大带宽的设备。

-

PCIe x16:包含十六个通道,提供最大的带宽,通常用于连接高性能显卡和其他需要极高数据传输速率的设备。

-

PCIe x32:包含三十二个通道,提供最大的带宽,它可能用于连接高性能网络接口卡、图形处理器、FPGA加速卡或其他需要大量数据传输的高性能设备。

从上图所看具有多种规格的插槽X1 X4 X8 X16 X32等到底怎么去理解:

PCIe的数据传输采用差分信号,X1表示1个Lane,X4表示共有4条Lane,这样Lane越多,那么传输的速度也就也快,但是成本也会更高;

X1/X2 主要用于扩展声卡,网卡等低速设备;

X4用于扩展磁盘阵列等中等速度设备;

X8/X16大多用于显卡相关设备;

另外插槽都是向下兼容的,比如X1可以介入

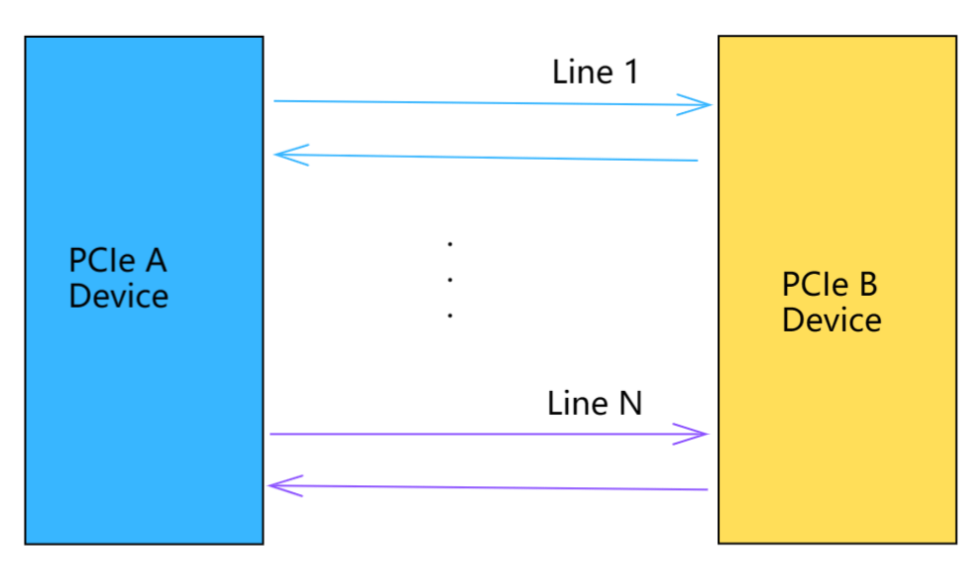

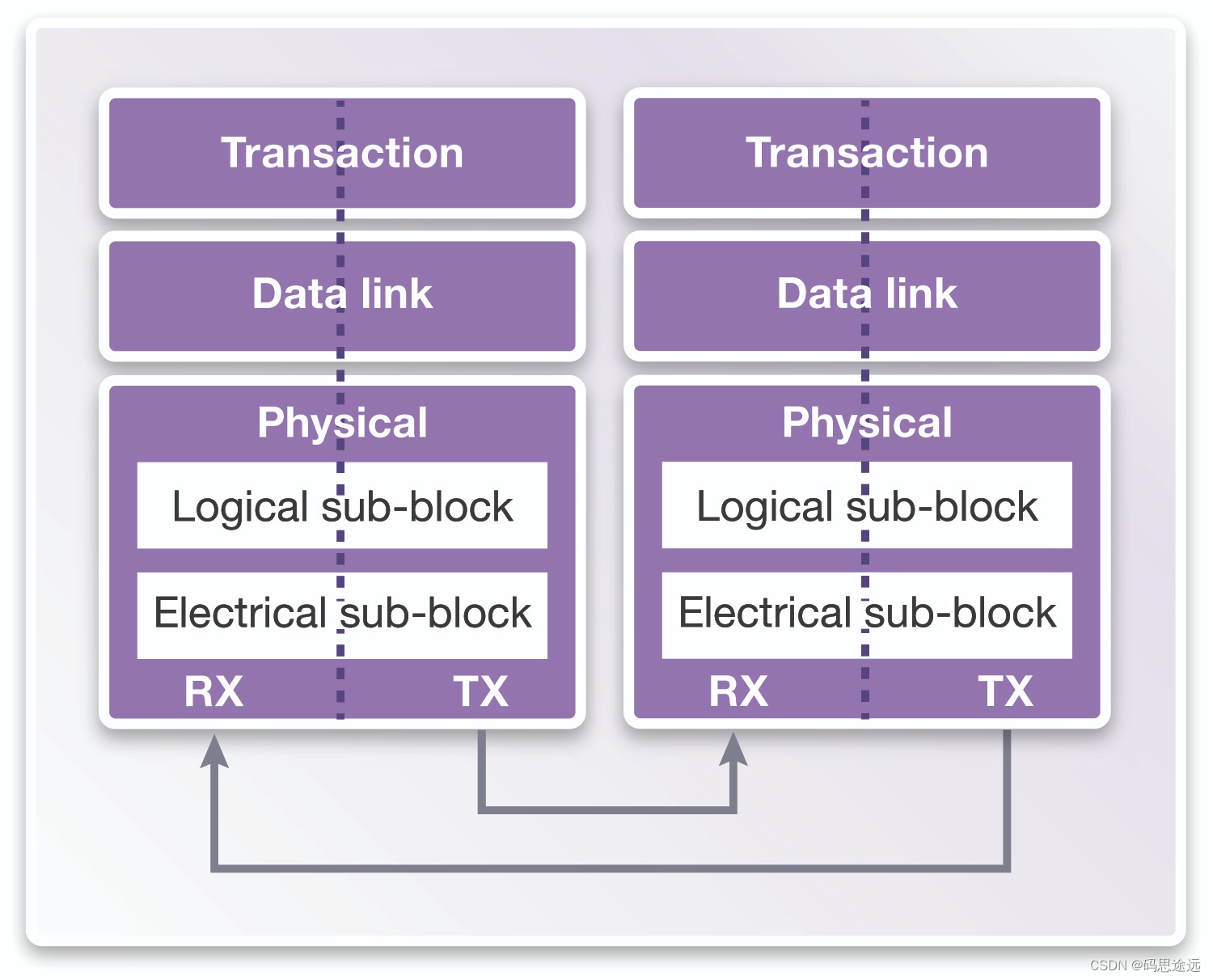

这里的Lan是什么?这里解释下:

查看图中PCIe A 与PCIe B两个设备进行全双工通信,Lan一个link TX, 另外一个link是RX,这样两个link组成一个Lane,一个PCIe的传输链路包含多个Lane,可以是1/2/4/8/16/32.

2.1 PCIe速率对比与吞吐量计算

PCIe随着版本的增加,速率也逐步提升,查看下图

2017年前发展相对比较慢,好几年才更新一个版本,然而在2017年后跟新的版本速度已经加快,速率也明显加快。2017年后速率都是以翻倍的速率呈现,是什么原因导致如此大的进步。

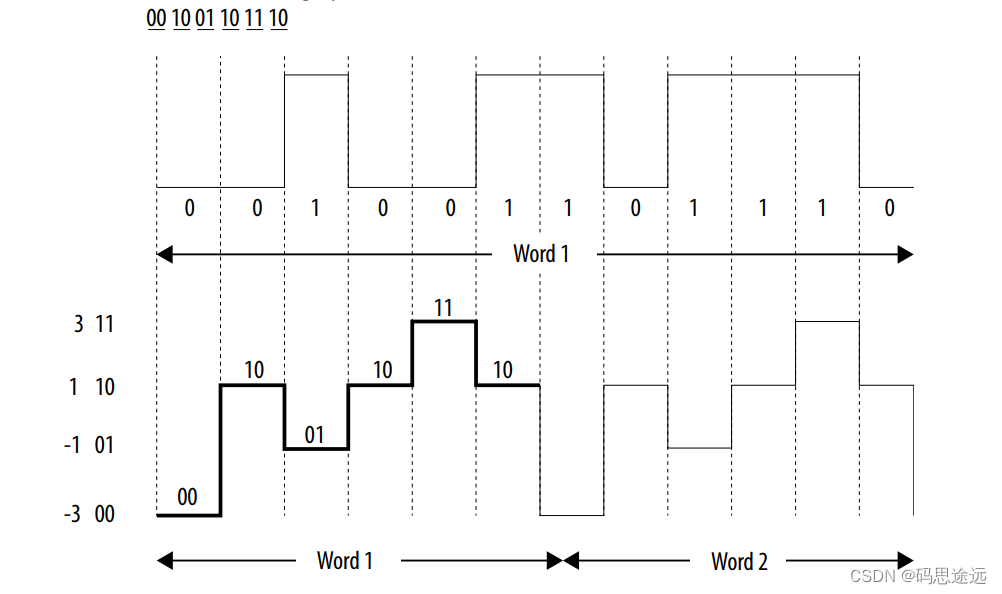

在PCIe6.0 版本引入了新的编码方式PAM4,才让PCIe6.0 的速率再次翻倍。这里我们简要说说这种编码为何可以使得速率得到翻倍如此高的性能。

PAM4不再采用NRZ这种归零码的方式0和1单一信号表示,而是采用四种编码(00/01/10/11)状态,这样就可以在同一个时间段携带NRZ信令的数据。

如图对于word1:

NRZ 传输了 0010001

PAM4传输了 001001101110

但是有人提出,为甚只用四种编码,为什么不用更多电平去考虑,主要还是受到噪声影响,电平太多出现的误码率也就越高了。

*PCIe 链路吞吐量计算方法:*

吞吐量 = 速率 * 带宽 * 2方向(全双工) * 编码方式

这里以PCIe4.0 版本为例子,4.0支持的速率是16.0GT/s,也就是说每条Line支持每秒传输16G个bit,从表中得到采用的编码是128b/130b,那么计算每一条Line的链路吞吐量:16x128/130=15.754Gbps=1969MB/s 和表中能对应上。那么假如是PCIe4.0 x4的通道是多少呢?2x4x16x128/130= 126.031 Gbps = 15.754 GB/s。

3. PCIE 总线架构

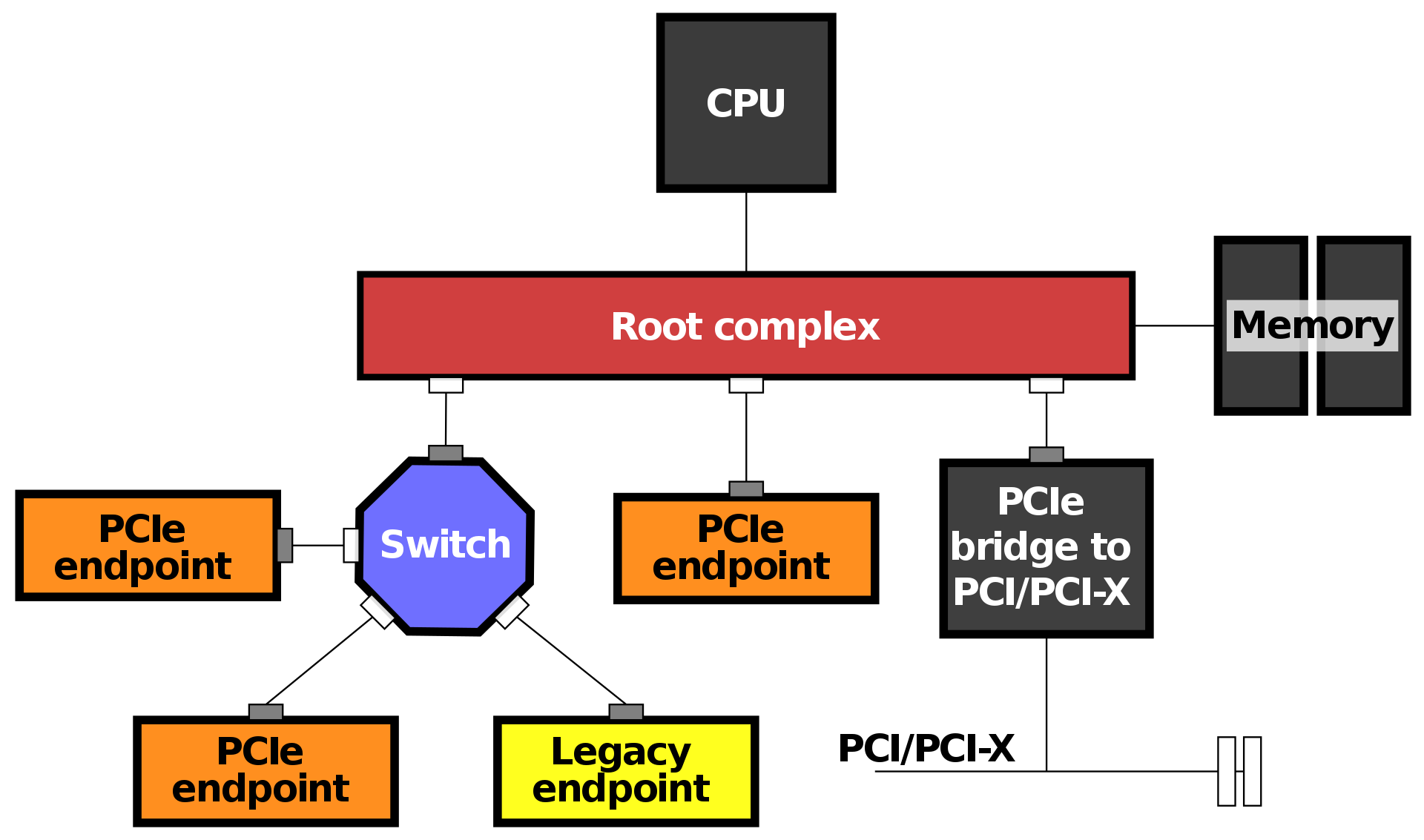

从前面提到PCIe是PCI的升级版本,PCIe采用了总线互联的架构,点对点进行传输数据,每个Device都具有自己的专属连接,不再共享总线宽带。

PCIe总线架构主要组成部分:

PCIe Root Complex: 通过CPU 总线与CPU和Memory进行交互,充当CPU,Memory,PCIe Bus之间的通信枢纽,实现各类外设的总线聚合,一个设备可以有多个Root Complex;

PCIe Switch: 用于扩展跟多的端口连接Endpoint;

PCIe -PCI: 用于连接PCI设备,也就是图中右下角灰色部分

PCIe Endpoint: PCIe的终端设备,比如我们看到的PCIe SSD,PCIe网卡等等;

- PCIe Endpoint: 访问地址空间大于4G,支持32/64bit,但无法产生I/O请求

- Legacy Endpoint: 访问地址空间小于4G,支持32bit,可以产生I/O请求

- Root Complex Integrated Endpoint:直接集成到Root Complex的这种设备,比如CPU的集成显卡【图中没有展现】;

另外还需要讲述几个概念:

Upstream Poat:靠近RC端的那个端口,我们称为上游端口(Upstream Poat)

Downstream Port:分离出来的其他端口,称为下游端口(Downstream Port)

工作原理:

PCIe的工作原理基于高速串行传输和点对点连接的概念,它通过差分对传输方式和数据包传输实现高性能、高带宽的数据传输。这使得PCIe成为现代计算机系统中主流的总线接口,用于连接各种高性能设备,如图形处理器、网络适配器、存储控制器等。

4. PCIe 逻辑分层

PCIe定义了三层结构:事务层、数据链路层、物理层。

事务层(Transaction ):创建与解析TLP数据包,流量数据控制,Qos等等

数据链路层(Data Link):创建于解析DLLP包,ACK/Nak协议(链路层检错和纠错)、流控、电源管理等。

物理层(Physical):负责将所有的数据通过物理传输,发送到各端的Line;

从PCIe的逻辑分层来看有点类似网络层次结构,设备的数据包都需要通过这三层进行打包发送出去,接收正好是相反。

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?