作者本人最近在研究双目测距算法,已经在ARM上面实现了双目测距,现在想在FPGA上面实现双目测距。用Verilog开发难度太大,现在只能用HLS进行综合,

鉴于有部分学者对英文文档的学习比较吃力,我就直接参考官方的手册ug871-vivado-high-level-synthesis-tutorial进行和实现的。

相当于把XILINX的官方文档实际操作了一遍。

鉴于国内没有很多人讨论HLS和xfopencv的,作者本人将在ZYNQ FPGA HLS旅程结束之后,创建一个QQ群给大家讨论关于HLS和xfopencv方面的问题

好了,直接开始

直接打开HLS软件软件

(1)双击打开vivado HLS 2017软件

(2)点击Create New Project 创建工程(工程名和路径如下)

(3)点击Next 之后界面如下:

之后操作如(既然都学FPGA了,这个英文也看的懂得)

官方文档这里有个说明

在本实验中,只有一个c设计文件。在需要合成多个c文件的情况下,应该在此阶段将它们全部添加到项目中。

对于存在于当前目录的头文件会自动包含在工程里面,如果头文件存在于其他位置,就使用CFLAGS按键加入标准gcc/g++ 寻找路径信息。

之后点击Next

界面如下:

在官网文档里,在这个图片上面专门有注释,

图6显示了用于指定测试工作台文件的输入窗口。除了头文件之外,测试台和测试台使用的所有文件都必须包括在内。可以一次添加文件,或者可以使用Ctrl和Shift键添加的多个文件。

加入文件之后(如下图)然后点击NEXT

然后选择开发板型号

之后点击Finish

得到之后的界面如下:

点击Test bench 文件夹,之后双击fir_test.c文件

关于test bench 有段说明

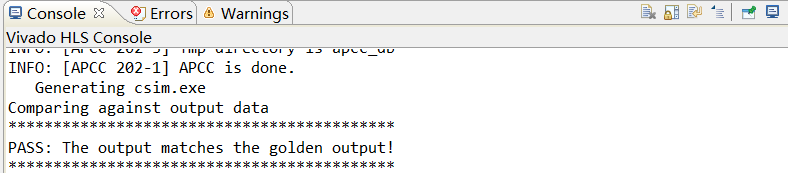

测试工作台文件fir_test.c包含顶层的c函数main(),它反过来调用要合成的函数(Fir)。这个测试平台的一个有用的特点是它是自检的。

*测试台将函数FIR的输出保存到输出文件out.dat中

*输出文件与存储在out.gold.dat文件中的准确结果进行比较

*如果输出匹配黄金结果的话,则消息结果确认正确,返回结果为0,如果不同,返回为1

之后点击 Run C Simulation按键,在C Simulation dialog box 里面选择ok

之后控制台输出如下:

接下了进行:高层次综合

如下:

2610

2610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?