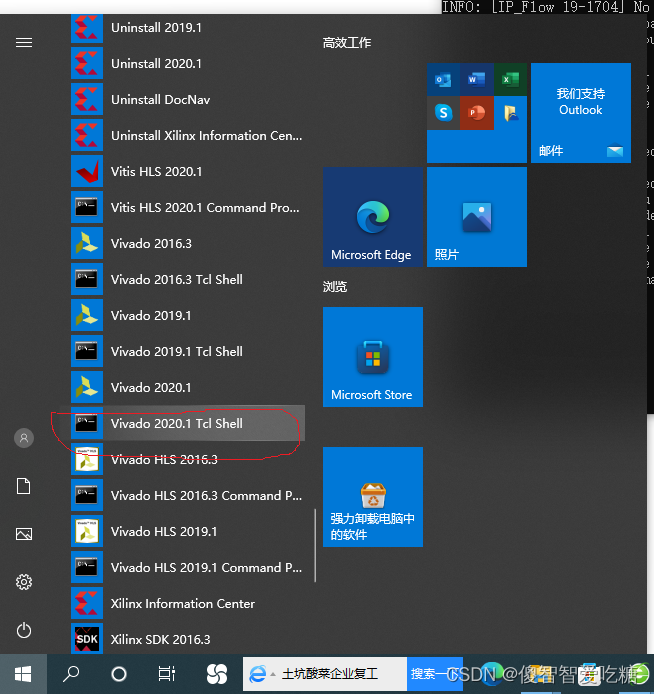

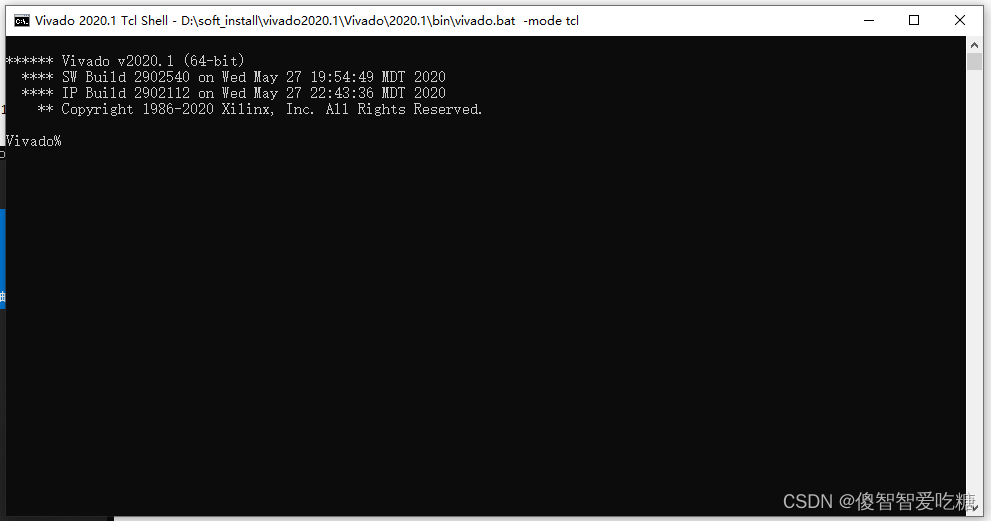

执行菜单命令【开始】—【所有程序】—【Xilinx Design Tools】—【Vivado2020.1】—【Vivado2020.1Tcl Shell】,弹出命令界面

或者cmd命令下输入call D:\soft_install\vivado2020.1\Vivado\2020.1\bin\vivado.bat -mode tcl

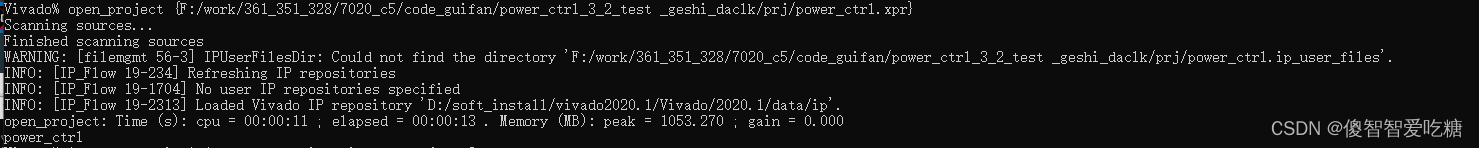

2.输入打开工程指令:

open_project {F:/work/361_351_328/7020_c5/code_guifan/power_ctrl_3_2_test _geshi_daclk/prj/power_ctrl.xpr}

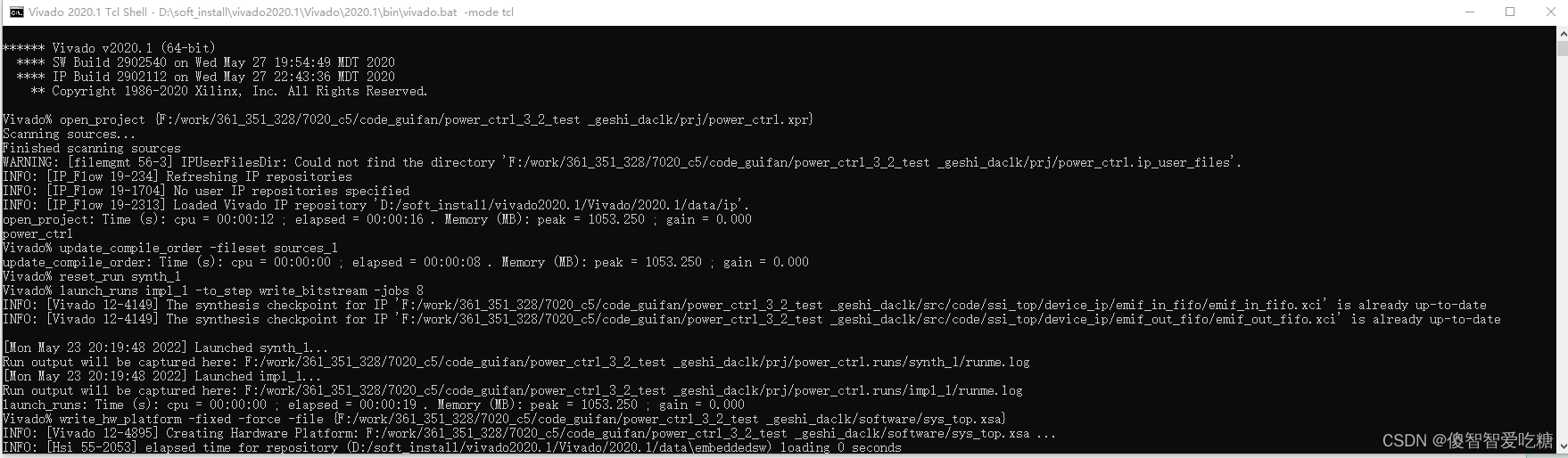

3.输入指令update_compile_order -fileset sources_1

3.输入复位synth指令:reset_run synth_1,系统编译回到最初始状态(这样工程编译的时候就从synth->impl->write_bitstream一步步进行),这个指令根据自己需要来确定是否使用

4.编译bit文件指令:launch_runs impl_1 -to_step write_bitstream -jobs 8

5.wait_on_run impl_1,编译,等待bit文件生成。

6.导出xsa文件给软件同事,指令为:write_hw_platform -fixed -include_bit -force -file {…/software/sys_top.xsa},将xsa文件导入到software目录下。

7.关闭工程:close_project

全部操作步骤、指令如下

open_project {Nan_test.xpr}

update_compile_order -fileset sources_1

reset_run synth_1

launch_runs impl_1 -to_step write_bitstream -jobs 8

wait_on_run impl_1

write_hw_platform -fixed -include_bit -force -file {../software/sys_top.xsa}

close_project

如下图所示(后续脚本有修改,没重新截图,以上面步骤为准)

1109

1109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?