Vivado 2021.1 生成Zynq7000 PS-Hello Platform工程XSA文件

问题描述

Alinx 的官方教程《course_s1 ALINX_ZYNQ (AX7z010_AX7z020)开发平台基础教程V1.03》中,提示使用VIVADO版本2017.4来测试并生成PS-Hello工程,但是实际测试,如果使用高版本时(本人测试使用VIVADO2021.1),会遇到一些问题,导致无法生成并到处硬件平台文件,此文章仅仅对初学者提供一些帮助,大神级自动滤过

与教材描述的区别

教材中,当添加了IP-》ZYNQ7之后,设置完对应PS侧所有的MIO配置,生成design_wrapper, 然后Genearte output Products, 就可以进行下一步,使用file->Export hardware导出硬件描述文件,

但是实际操作时,新版本当使用FILE导出PLATFORM平台硬件工程时,会提示没有设置成功时钟等等问题:

例:

SDSOC: PFM-CLOCK未定义,

同时,通过打开TAB “Platform Setup”, 会有两处红色感叹号提示:

解决步骤

配置Platform Setup 配置

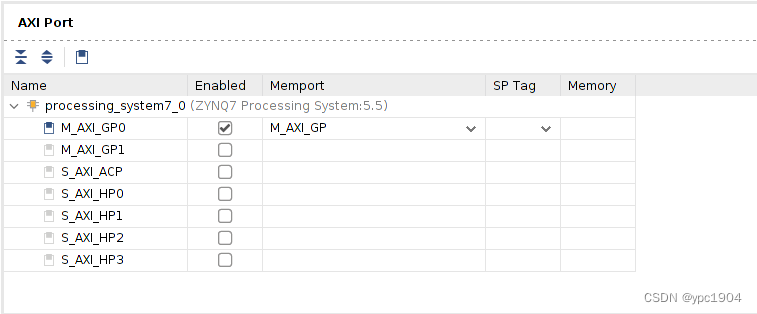

第一步:配置AXI_Port选项

点击选中AXI Port 中name栏目下的M_axi_GP0, 选中ENABLed复选框,并配置MEMPORT为M_AXI_GP,示例如下图

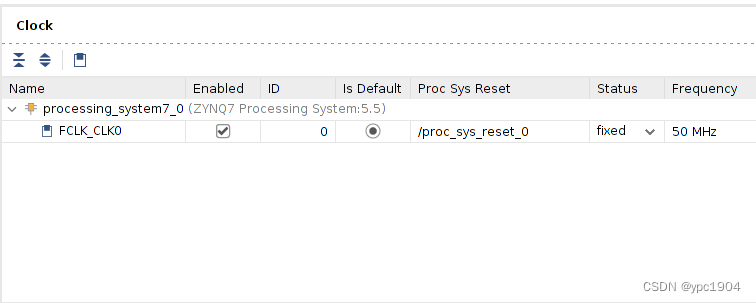

第二步:配置Clock选项

第二步:配置Clock选项

报错中,提示PS侧CLK时钟未定义,即代表此处PLATFORM平台工程的时钟未指定,需要选中FCLK_CLK0, Enabled复选框选中,Is Default副选框选中,Proc Sys Reset设置为 /proc_sys_reset_0 等等(此处一会需要添加PS侧重启管理IP)

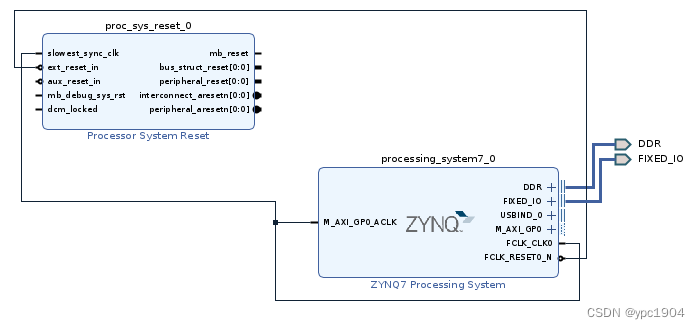

添加proc_sys_rest IP核

添加一个新的XILINXIP核,在block design 中,添加proc_sys_reset_0的IP核,并点击自动布局布线,完成连接,

此时,ZYNQ7的IP,FCLK_CLK0会与slowest_sync_clk连接,FCLK_RESET0_N将与ext_reset_in连接,而此时Platform 平台的FCLK时钟,将由Processor system reset IP核提供。

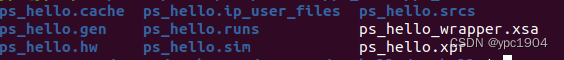

解决效果

此时,如果平台工程成功找到了对应设置PS的时钟,就可以成功编程硬件输出的描述文件XSA,结果示意图如下:

本测试中,生成的硬件平台文件为:ps_hello_wrapper.xsa

文中IP:Proc_sys_reset IP核的详细介绍

请参见其它大神文章,链接分享:

https://blog.csdn.net/weixin_42837669/article/details/116853566

5723

5723

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?