在画电路图的时候有可能会遇到这样的一个问题:某个元件的引脚间距很小,如果用统一的间距规则去画图,那么这个元件就会显示错误,这个错误还有影响。AD画图有一个弊端就是当出现错误的时候这条线就不会再按照规则继续了,也就造成了这条线后面即使有线的交叉ad软件也不会管的,因此要解决这个问题。

今天我同样也遇到了这个问题,下面来讲讲如何对某个元件单独设计规则。

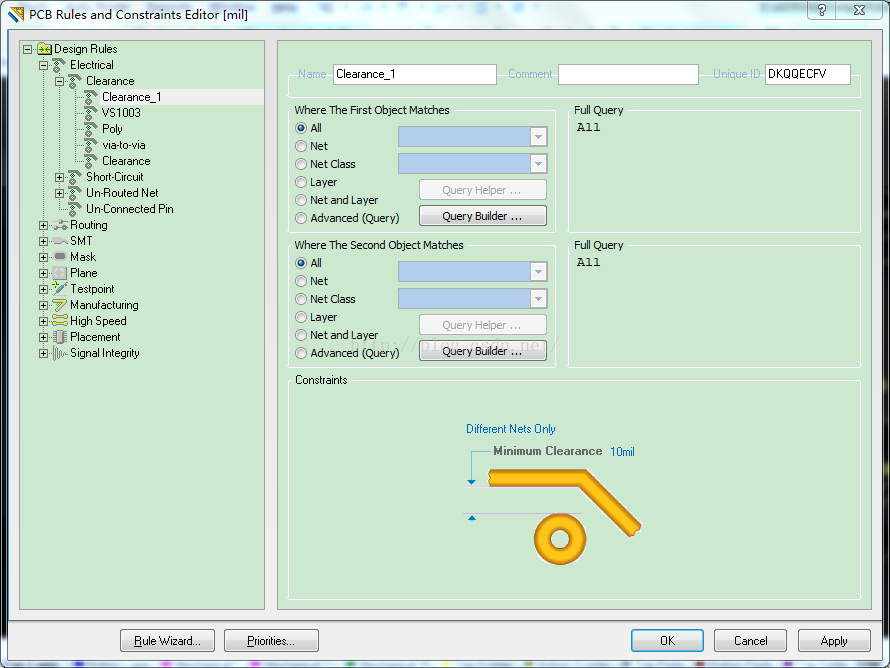

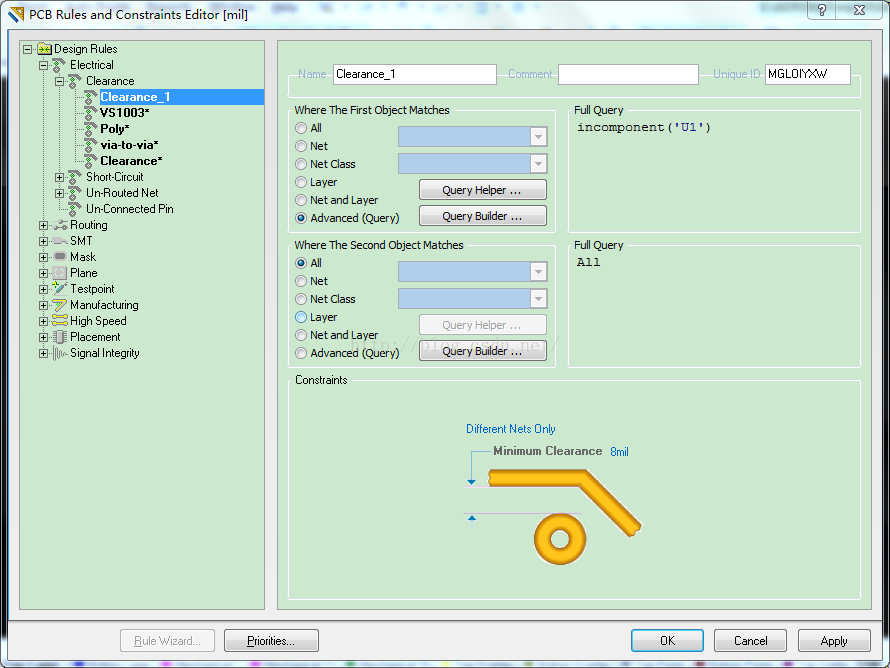

步骤如下(附图):

Design -> Rules -> Clearence -> Electricity -> clearence -> New Rule -> 设置线距规则。

这样设置完成之后,单个元件的线距规则就被修改了,我这里修改的是元器件U1,最小线距为8mil,再去看PCB图就不会出现错误了。

这里我再来说说今天还遇到的问题,我在PCB元器件的时候,发现点击update之后,PCB中的元器件并没有改变。因此我当时画的封装出了点问题,修改之后元器件并没有改变,这可能是AD9内部的一种机制吧。如果你没有删除PCB中的元器件,直接进行添加,就不会改变。因此要先删除,再进行更新PCB。

这是我遇到的使用AD9软件的小错误,慢慢积累吧!终有一天也会积少成多的。

1288

1288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?