SRAM读写时序

对SRAM进行读写数据时,它各个信号线的时序流程如下图

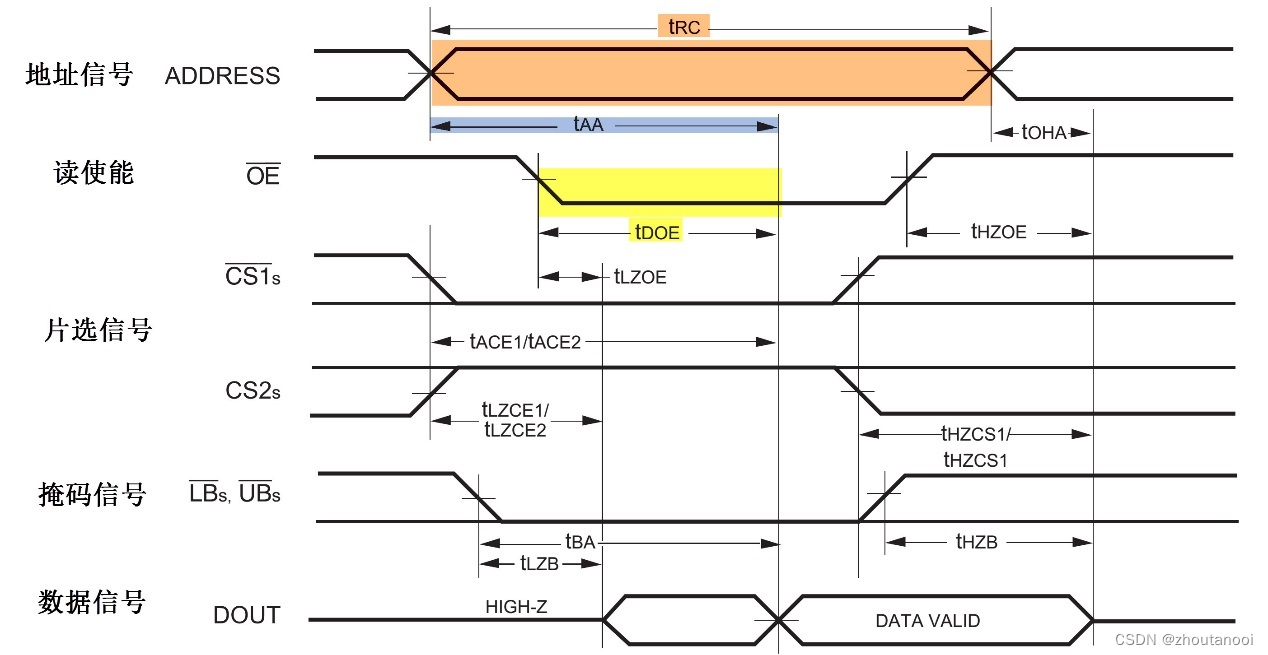

(图一)SRAM的读时序

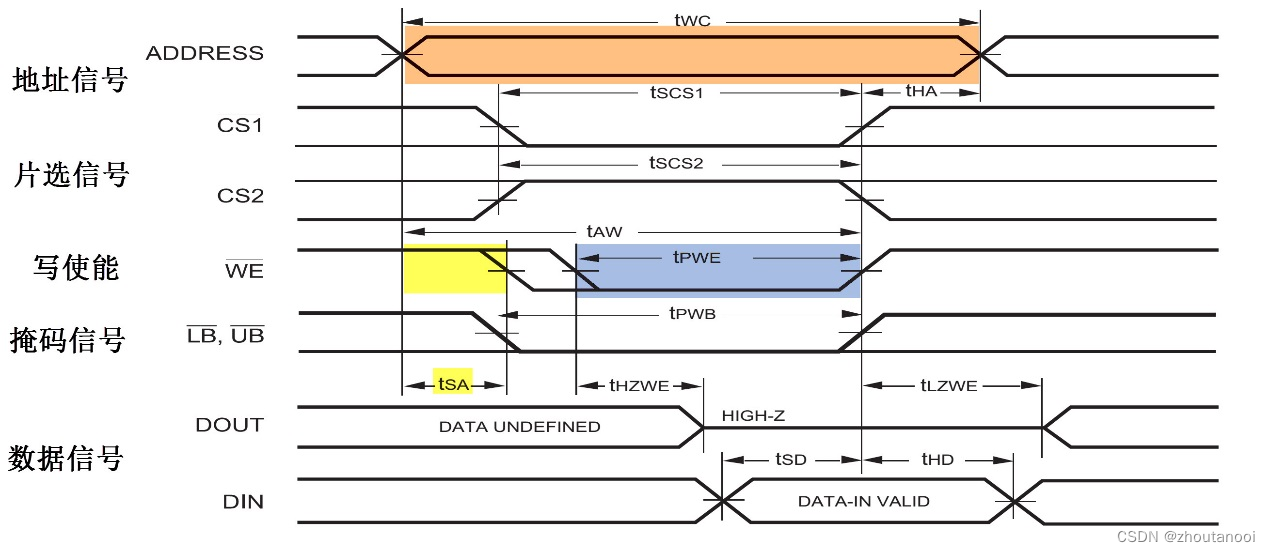

(图二)SRAM的写时序

流程解释

- 主机使用地址信号线发出要访问的存储器目标地址;

- 控制片选信号CS1#及CS2#使能存储器芯片;

- 若是要进行读操作,则控制读使能信号OE#表示要读数据,若进行写操作则控制写使能信号WE#表示要写数据;

- 使用掩码信号B#与UB#指示要访问目标地址的高、低字节部分;

- 若是读取过程,存储器会通过数据线向主机输出目标数据,若是写入过程,主要使用数据线向存储器传输目标数据。

参数介绍

在读写时序中,有几个比较重要的时间参数,在使用STM32 控制的时候需要参考,它们的介绍见下表。

SRAM时序结构体

控制FSMC使用SRAM存储器时主要是配置时序寄存器以及控制寄存器,利用HAL库的SRAM时序结构体以及初始化结构体可以很方便地写入参数。

typedef struct

{

uint32_t FSMC_AddressSetupTime; /*地址建立时间,0-0xF个HCLK周期*/

uint32_t FSMC_AddressHoldTime; /*地址保持时间,0-0xF个HCLK周期*/

uint32_t FSMC_DataSetupTime; /*地址建立时间,0-0xF个HCLK周期*/

uint32_t FSMC_BusTurnAroundDuration;/*总线转换周期,0-0xF个HCLK周期,在NOR FLASH */

uint32_t FSMC_CLKDivision;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2475

2475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?