双非硕士 研一下学期视觉转FPGA(在b站跟小梅哥视频)

长路漫漫,但希望前途光明

同理,一开始先创建文档,这里都省略了

创建文档led_run8.v

led_run8.v的代码如下

module led_run8(

Reset_n,//复位端口,加_n是使用低电平复位

Clk,//时钟端口

Led

);

input Clk;

input Reset_n;

output reg Led;

parameter MCNT = 24999999;

reg [24:0]counter;

always@(posedge Clk or negedge Reset_n) //posedge Clk 为时序描述的标准格式

// <=是非阻塞赋值的意思

if(!Reset_n)

counter <= 0;

else if(counter == MCNT)

counter<=0;

else

counter <= counter+1'd1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <= 0;

else if(counter == MCNT)

Led <=!Led;

endmodule进行模拟仿真,代码内容如下:

`timescale 1ns/1ns

module led_run8_tb();

reg Reset_n;

reg Clk;

wire [3:0]Led;

led_run8 led_run8_test0(

.Reset_n(Reset_n),//复位端口,加_n是使用低电平复位

.Clk(Clk),//时钟端口

.Led(Led[0])

);

defparam led_run8_test0.MCNT=24999;

led_run8 led_run8_test1(

.Reset_n(Reset_n),//复位端口,加_n是使用低电平复位

.Clk(Clk),//时钟端口

.Led(Led[1])

);

defparam led_run8_test1.MCNT=49999;

led_run8 led_run8_test2(

.Reset_n(Reset_n),//复位端口,加_n是使用低电平复位

.Clk(Clk),//时钟端口

.Led(Led[2])

);

defparam led_run8_test2.MCNT=74999;

led_run8 led_run8_test3(

.Reset_n(Reset_n),//复位端口,加_n是使用低电平复位

.Clk(Clk),//时钟端口

.Led(Led[3])

);

defparam led_run8_test3.MCNT=99999;

initial Clk=1;

always #10 Clk = !Clk;

initial begin

Reset_n=0;

#201;

Reset_n=1;

#40000000;

$stop;

end

endmodule验证效果如下

然后可以进行板机验证,首先对其进行管脚分配

然后可以进行板机验证,首先对其进行管脚分配

还是如之前的文章类似,在点击了Open Synthesized Design后,页面右侧就会弹出可以分配管脚的页面,由于项目越复杂,要分配的I/O就越多

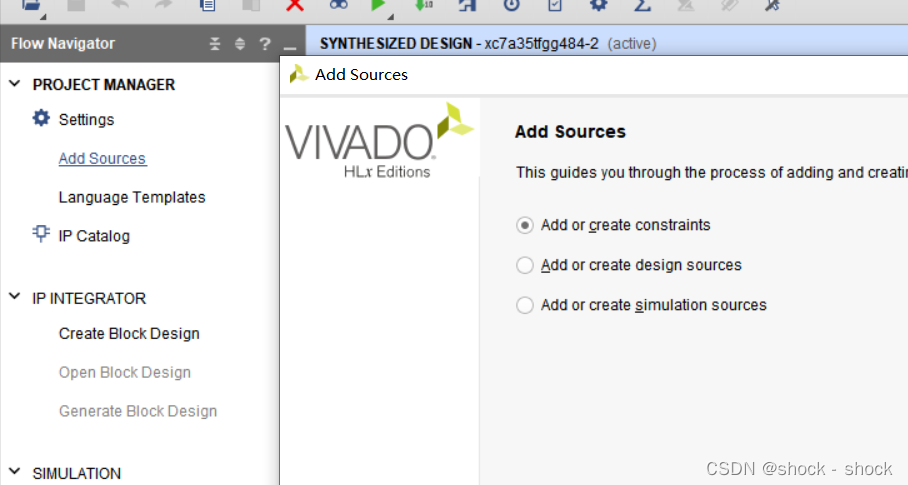

所以首先在左侧找到Add Sources ,选择Add or Create Constrains.

创建步骤与之前类似

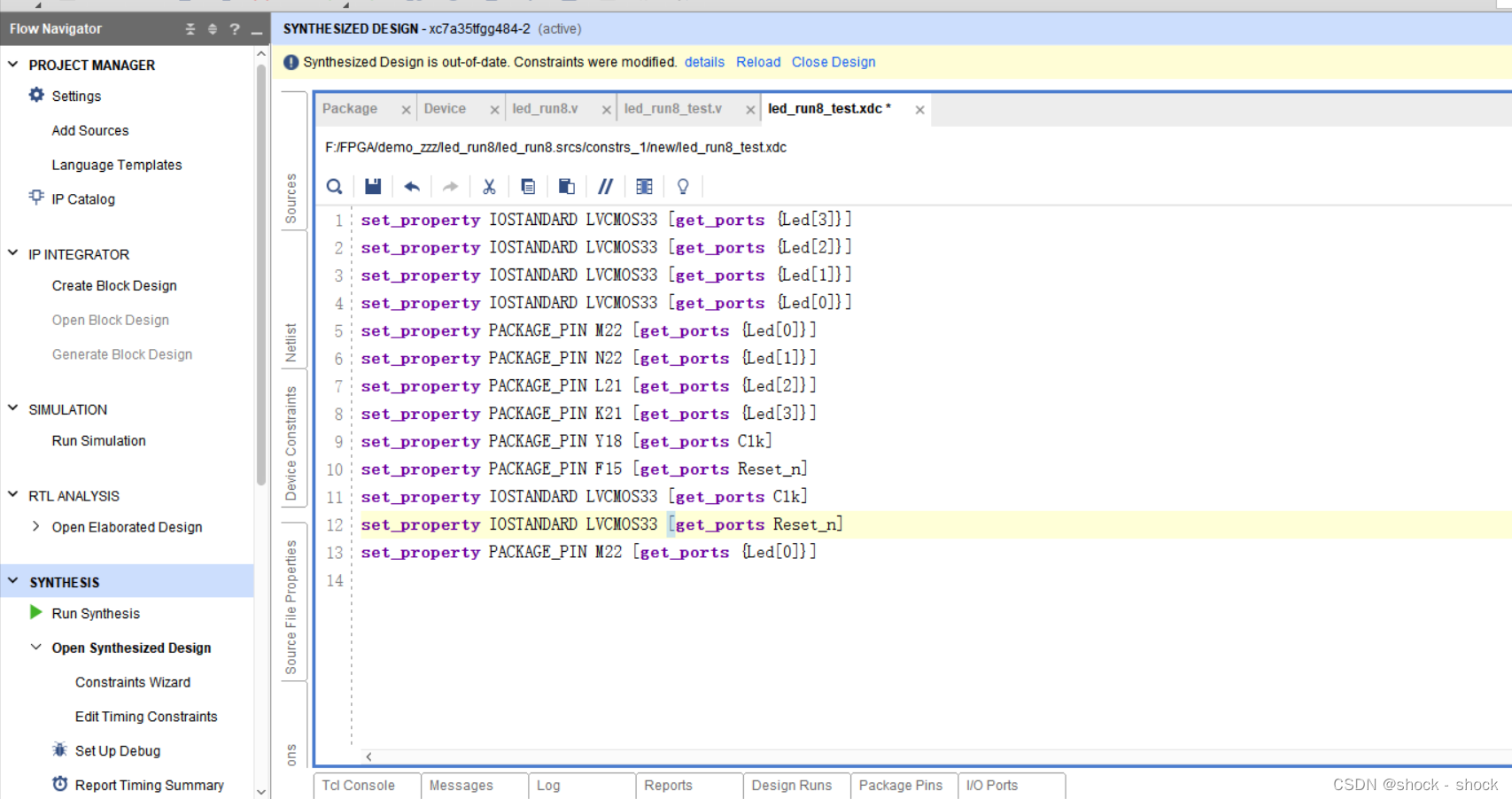

代码内容如下

set_property IOSTANDARD LVCMOS33 [get_ports {Led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {Led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {Led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {Led[0]}]

set_property PACKAGE_PIN M22 [get_ports {Led[0]}]

set_property PACKAGE_PIN N22 [get_ports {Led[1]}]

set_property PACKAGE_PIN L21 [get_ports {Led[2]}]

set_property PACKAGE_PIN K21 [get_ports {Led[3]}]

set_property PACKAGE_PIN Y18 [get_ports Clk]

set_property PACKAGE_PIN F15 [get_ports Reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports Clk]

set_property IOSTANDARD LVCMOS33 [get_ports Reset_n]

set_property PACKAGE_PIN M22 [get_ports {Led[0]}]

后续板机验证步骤就跟之前一样了。

1924

1924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?