双非硕士 研一下学期视觉转FPGA

长路漫漫,但希望前途光明

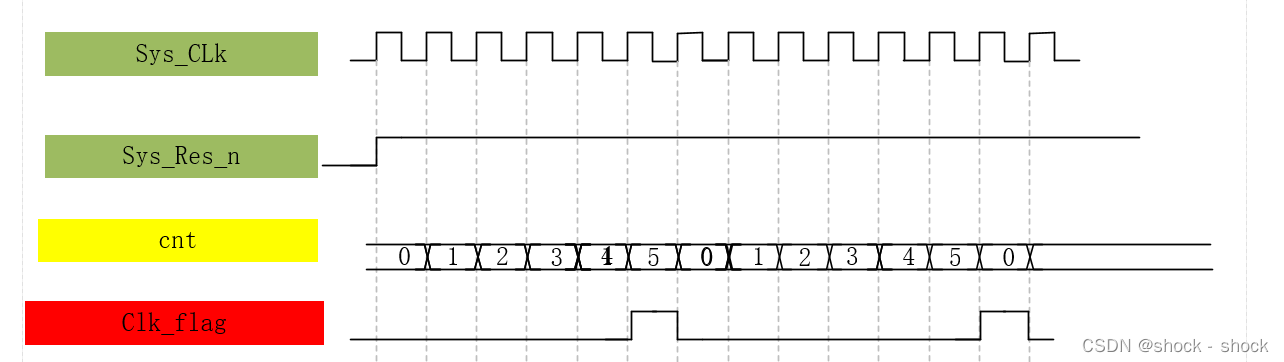

偶分屏就是将普通的时间周期延长,比如延长为六分屏

模拟波形如下

代码如下

module divider_six(

input Clk,

input Reset_n,

output reg divider_six_Clk

);

reg [2:0] cnt;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

cnt <= 0;

else if(cnt == 5)

cnt <= 0;

else

cnt <= cnt + 1'b1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

divider_six_Clk <= 0;

else if(cnt == 4)

divider_six_Clk <= 1'b1;

else

divider_six_Clk <= 0;

endmodule

仿真代码如下

`timescale 1ns / 1ps

module divider_six_tb();

reg Clk;

reg Reset_n;

wire divider_six_Clk;

divider_six divider_six_inst0(

.Clk(Clk),

.Reset_n(Reset_n),

.divider_six_Clk(divider_six_Clk)

);

initial

begin

Clk = 1;

Reset_n = 0;

#201;

Reset_n = 1;

#200000

$stop;

end

always #10 Clk = !Clk;

endmodule

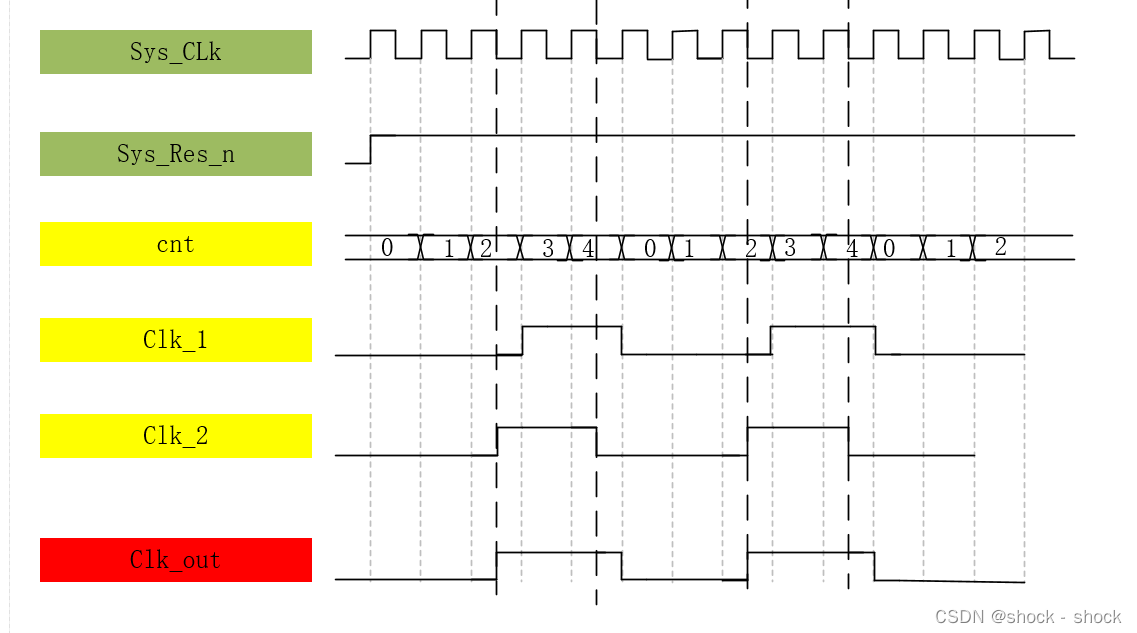

奇分屏 分屏的效果

代码内容 以五分屏为例

module divider_five(

input Clk,

input Reset_n,

output wire Clk_out

);

reg [2:0]cnt;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

cnt <= 0;

else if(cnt == 4)

cnt <= 0;

else

cnt <= cnt + 1'b1;

reg Clk_1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Clk_1 <= 0;

else if(cnt == 2)

Clk_1 <= 1;

else if(cnt == 4)

Clk_1 <= 0;

else

Clk_1 <= Clk_1;

reg Clk_2;

always@(negedge Clk or negedge Reset_n) //取时钟的下降沿

if(!Reset_n)

Clk_2 <= 0;

else if(cnt == 2)

Clk_2 <= 1;

else if(cnt == 4)

Clk_2 <= 0;

else

Clk_2 <= Clk_2;

assign Clk_out = (Clk_1 | Clk_2);

endmodule

仿真代码

`timescale 1ns / 1ps

module divider_five_tb();

reg Clk;

reg Reset_n;

wire Clk_out;

divider_five divider_five_inst(

.Clk(Clk),

.Reset_n(Reset_n),

.Clk_out(Clk_out)

);

initial

begin

Clk = 1;

Reset_n = 0;

#201;

Reset_n = 1;

#20000;

$stop;

end

always #10 Clk = ~Clk;

endmodule

3281

3281

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?