以前做的项目,都是在单片机或DSP上裸跑,代码写起来那叫一个费劲,要自己用定时器做时间片,自己做任务调度,自己写非常底层的代码(比如说将Byte转为Char或String)。以后项目的软件复杂度肯定越来越高,硬件平台也会必然升级,这里自学一下几个基本概念。

1. Real-Time Operating Systems(RTOS)

这里的Real-Time主要体现在:任何任务的执行的最大时间或大部分最大时间是可以确定的。这里解释为:To be considered "real-time", an operating system must have a known maximum time for each of the critical operations that it performs (or at least be able to guarantee that maximum most of the time). 而我们用的Win7和Ubuntu都是属于General-Purpose OS。

RTOS的优点:稳定、任务执行可控,因此很多关键领域必须要用RTOS,比如航天、汽车、工业生产线等。也主要用于嵌入式平台上。

wiki根据2014年的嵌入式市场报告,列出了RTOS的前十名:

- TI-RTOS Kernel (previously called DSP/BIOS)

- RTEMS open source RTOS designed for embedded systems, mainly used for missile and space probes control

2.Instruction Set (ISA)

指令集,就是关于处理器所执行的指令和操作数(机器语言)的一个规范。历史上在不同的微架构上出现了不同的指令集(一说是当时的软硬件不分家),及复杂指令集CISC精简指令集RISC。CISC的指令是不定长的,x86上最长的指令是15字节,这造成了执行效率低下等问题;RISC的指令数量比CISC少,且是固定长度的,方便指令流水。关于CISC和RISC孰优孰劣的问题,见

这里:“CISC和RISC之争早就结束了。现在的处理器速度是快是慢跟指令集架构基本没有关系,HPCA 2013上登了WISC-Madison的一篇文章,有人分析对比了Cortex-A8/A9和Intel i7/Atom,得出了指令集架构的影响力早已被处理器微结构乃至更底层的设计实现给抹平了的结论。”

x86是CISC,ARM、MIPS是RISC。下面给出一个不同指令集对加法的

处理方式,一起体会一下:

C = A+B

- 0-operand (zero-address machines), so called stack machines: All arithmetic operations take place using the top one or two positions on the stack: push a, push b, add, pop c.

- C = A+B needs four instructions. For stack machines, the terms "0-operand" and "zero-address" apply to arithmetic instructions, but not to all instructions, as 1-operand push and pop instructions are used to access memory.

- 1-operand (one-address machines), so called accumulator machines, include early computers and many small microcontrollers: most instructions specify a single right operand (that is, constant, a register, or a memory location), with the implicit accumulator as the left operand (and the destination if there is one): load a, add b, store c.

- C = A+B needs three instructions.

- 2-operand — many CISC and RISC machines fall under this category:

- CISC — move A to C; then add B to C.

- C = A+B needs two instructions. This effectively 'stores' the result without an explicit store instruction.

- CISC — load a,reg1; add b,reg1; store reg1,c; This requires a load/store pair for any memory movement regardless of whether the add result is an augmentation stored to a different place, as in C = A+B, or the same memory location: A = A+B.

- C = A+B needs three instructions.

- RISC — Requiring explicit memory loads, the instructions would be: load a,reg1; load b,reg2; add reg1,reg2; store reg2,c.

- C = A+B needs four instructions.

- CISC — move A to C; then add B to C.

3. Microarchitecture

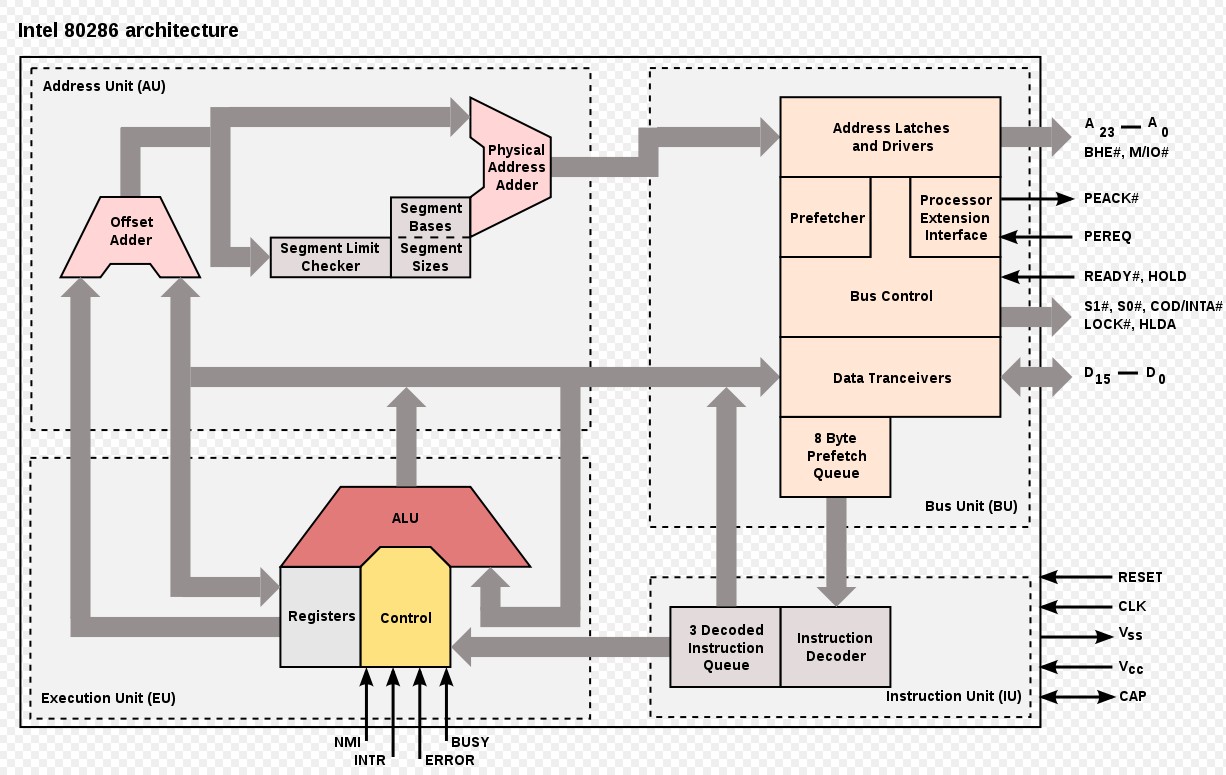

微架构,指的是在处理器上执行ISA的方式,包括ALU、寄存器等单元的互联方式和执行流程:

4. ARM

从来没用过ARM,但非常有必要了解一下。ARM全称是Advanced RISC Machine,是一家英国公司,从事处理器ISA和微架构的设计,ARM公司并不自己卖物理芯片,它只通过授权的方式卖它的架构设计。它的授权方式包括:指令集授权,微架构授权,应用授权等。

- ARM的ISA就是我们所谓的“ARM架构”(ARM architecture),命名方式为ARMvX,最新的是ARMv8。

- ARM微架构(或者说ARM core)命名方式为ARM1~ARM11,ARM11后命名为Cortex(包括M、R、A三个系列)。

其他公司可以根据自身情况向ARM公司购买不同的授权,比如说Apple购买ARMv7-A(ISA)开发出自己的Core:Swift;ST(意法半导体)购买ARM的CortexM系列(微架构)并搭建外围开发出STM32系列MCU芯片,Xilinx也是购买了Cortex-R和Cortex-A开发出Zynq系列FPGA。更多的授权情况,见

List_of_ARM_microarchitectures。而根据ARM微架构开发出来的芯片,见

List_of_applications_of_ARM_cores。

354

354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?