cadence的Auto-interative Delay Tune功能在设置多跟等长线是十分方便的:

Allegro Auto-interactive Delay Tune-教育-高清完整正版视频在线观看-优酷 (youku.com)

Allegro AIDT DDR3自动等长视频教程Auto-Interactive Delay Tune_哔哩哔哩_bilibili

AD中需要先建立一个类,之后进行等长调节;或者activateroute在自动布线的时候就自动等长处理。

【Altium等长线长度设置方法:手动输入和指定网络】:

【Altium】等长线长度设置方法:手动输入和指定网络_哔哩哔哩_bilibili

【Altium Designer 23|AD23如何批量更改同一线宽】:MASK,same

Altium Designer 23|AD23如何批量更改同一线宽_哔哩哔哩_bilibili

PCB设计十大误区-绕不完的等长_pcb 布线等长 弯度怎么算-CSDN博客

Tab键:暂停当前命令,此时可以打开属性对话框进行属性的设置。

选中整个导线后,打开属性右侧的Total是整个属性导线的长度,左侧是表层或者选中导线的长度。

关于整个导线和选中导线的区别,见下面两张图:

Manual:是自定义绕线总长度;From Net是参照某个走线来绕等长

DDR的T型拓扑结构:

AD22 X-Signal功能:

在不同导线上带有端接电阻时候,相当与把导线分为了两截,但是等长线是从输入端到输出端等长的,不能分截做等长,所以有些工程用EXCEL表计算求和算导线的长度,这样显然很麻烦。

DDR绕等长线:

调出PCB,选择xSignails,点击设计中的xSignails,点击运行xSignails向导,是针对于USB3.0和DDR的专用xSignails,普通的需要点击创建xSignails。

左面CPU器件U1,右面DDR器件U5,之后左下角选择网络,点击最下面的分析。

直接过滤为两个DDR端到端的连接,排除了中间端接电阻等的影响。

设置高速等长线的最大容忍偏差:

之后如果xSignails中的等长线不符合等长要求的话会黄色高亮显示报错,如下图所示:

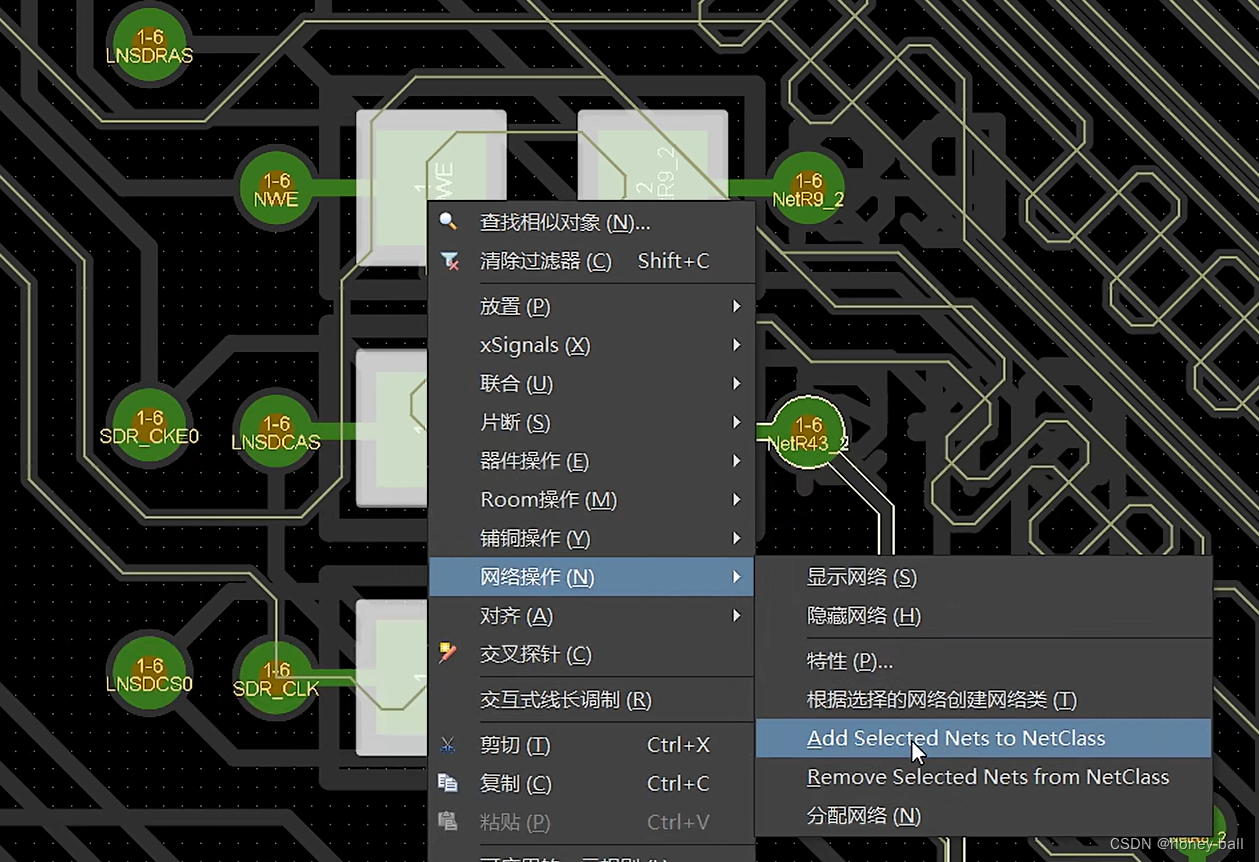

创建add的class类:

左上是第一器件的位号,右上是第二个器件的位号,选择网络class为事先创建的add,之后点击分析即可创建xsignals的一个小类。

这样便能读取T型网络下一端的导线长度,便于对一端的DDR与CPU之间进行等长处理。

遇到分析器避开串接电阻的状况需要将电阻的两个焊盘属性添加到网络class中去:

https://www.bilibili.com/video/BV1Jt4y1p7Qz?vd_source=3cc3c07b09206097d0d8b0aefdf07958

1202

1202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?