SPI是一种高速、全双工、同步的通信总线,速度可达十兆到七十兆,高于IIC,在芯片的管脚上占用四根线。

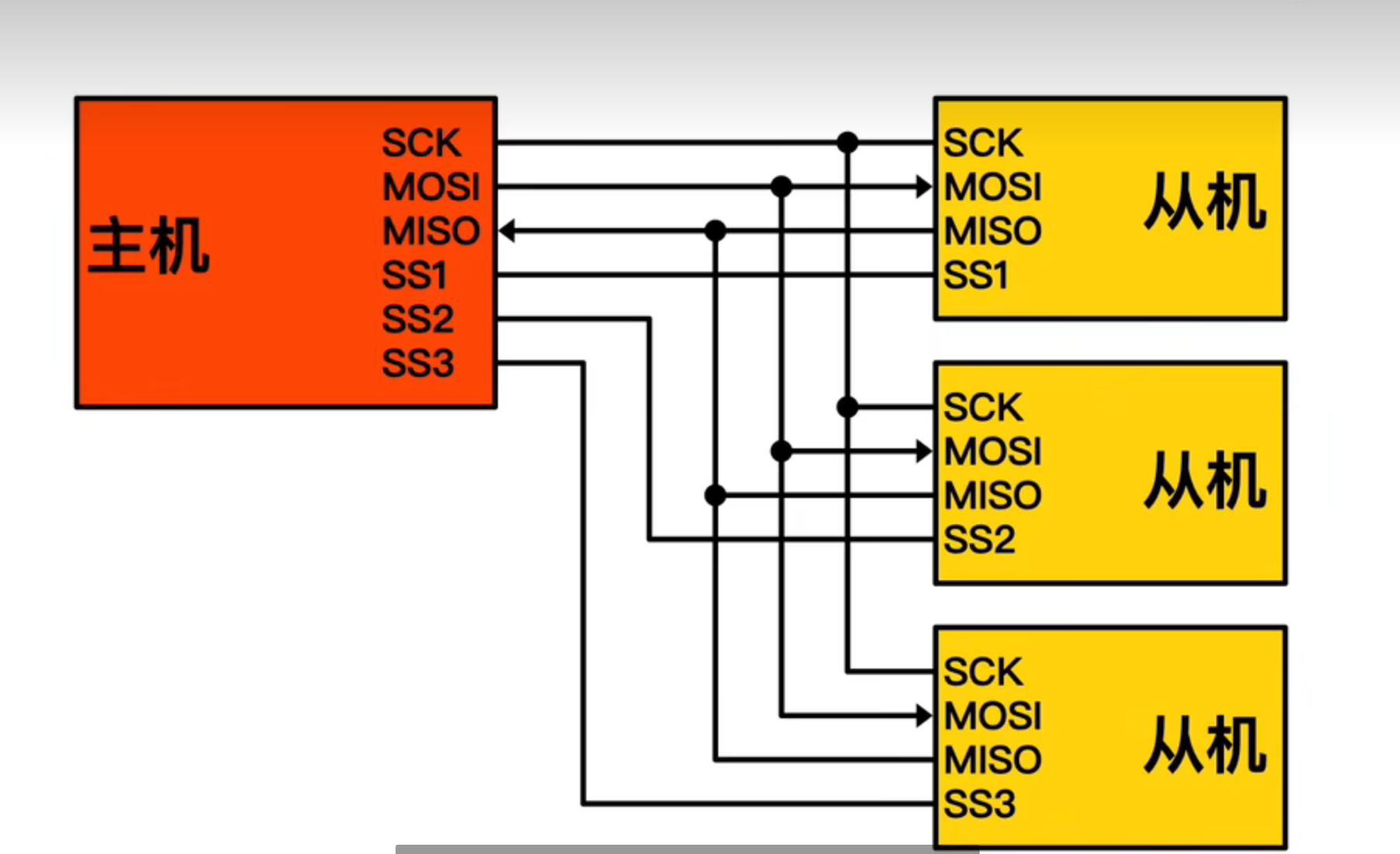

SPI通讯采用一主多从模式。

SPI接口一般使用四条信号线通信:SDI(输入数据),SDO(输出数据),SCK(时钟),CS(片选)

- MISO:主设备输入/从设备输出引脚

- MOSI:主设备输出/从设备输入引脚

- SCLK:串行时钟信号,由主设备产生

- CS/SS:从设备片选信号,由主设备控制,低电平有效。若从机要与主机通信,则拉低SS电平

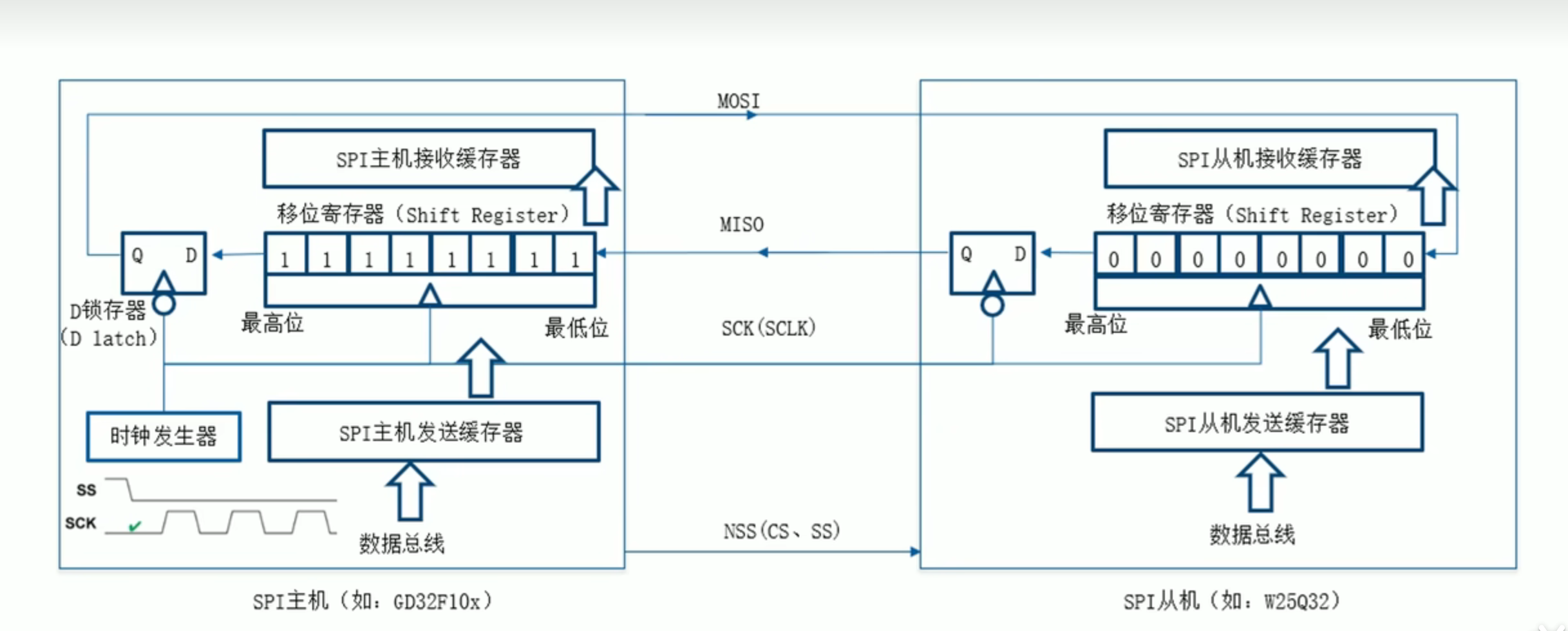

SPI数据发送接收

拉低对应SS信号线,则表示与该设备进行通信

SCLK时钟信号可能是低电平有效,也可能是高电平有效(原因见后文)

SPI一主一从数据交换示意图

1. 拉低片选信号后,

2. 在有效的时钟边沿上(见下文),主从机移位寄存器最高位移到锁存器中,随后主机将最高位通过MOSI信号线移到从机最后一位,同时从机将最高位通过锁存器移到主机最低位

3. 在八个有效的时钟周期后,一帧数据移入到接收缓存器中

4. 发送缓存器再将新一帧数据移入移位缓存器中

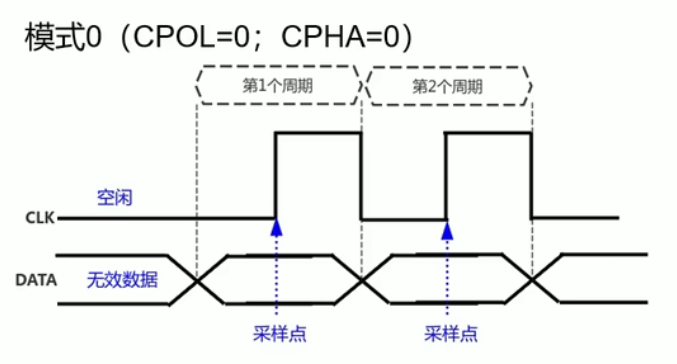

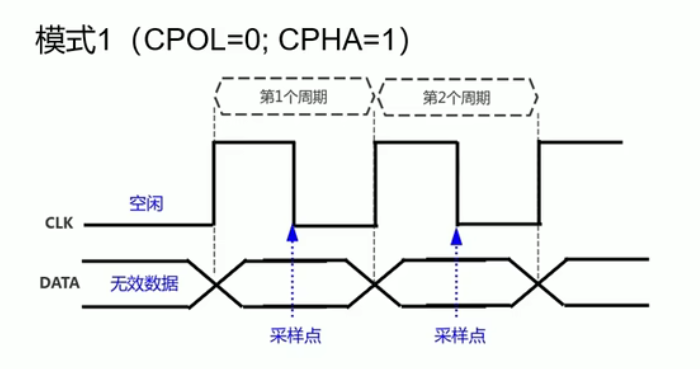

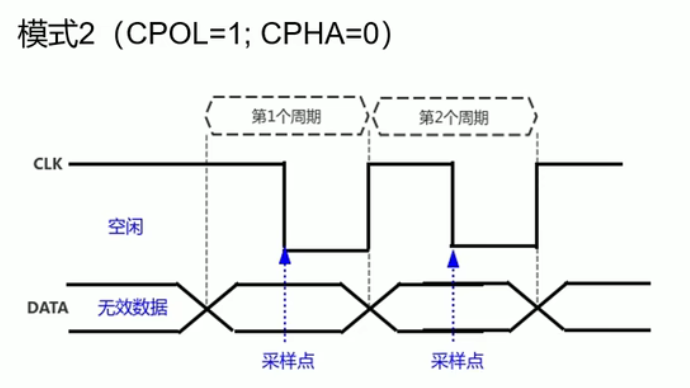

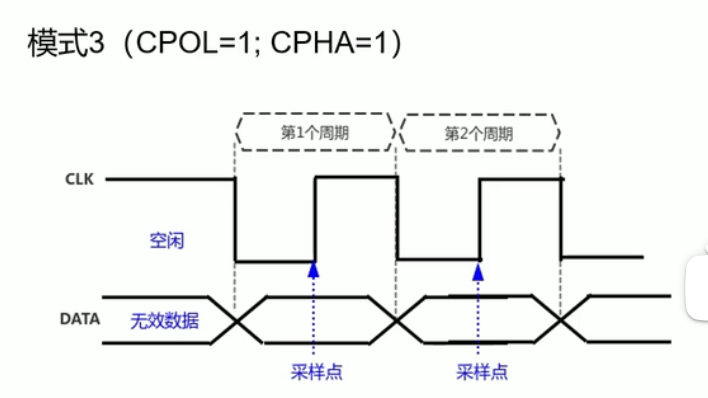

SPI通信模式

CPOL(极性):若为0,则空闲时为低电平;若为1,则空闲时为高电平

CPHA(相位):若为0,则为波形第一个边沿采样;若为1,则为第二个边沿采样

| 模式 | CPOL | CPHA | 说明 |

|---|---|---|---|

| 0 | 0 | 0 | 低电平的上升沿读取 |

| 1 | 0 | 1 | 低电平的下降沿读取 |

| 2 | 1 | 0 | 高电平的下降沿读取 |

| 3 | 1 | 1 | 高电平的上升沿读取 |

stm32的SPI总线见另一博客:stm32——SPI总线-CSDN博客

1953

1953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?