2.用VHDL语言设计一个8位指令计数器PC

① 理解题意,分析题目要求我们先设计一个8位指令计数器PC,在时钟下降沿时,若IN_PC=1,LD_PC=0,则c[7…0]中数据自加1;若IN_PC=0,LD_PC=1,则a[7…0]信号传入c[7…0]中。

② 打开Quartus II,新建工程,工程命名为PC,开始编写源代码。

③ 写好源代码,保存文件。

LIBRARY IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity PC is

port(LD_PC,IN_PC,clk:in std_logic;

a:in std_logic_vector(7 downto 0);

c:out std_logic_vector(7 downto 0));

end PC;

architecture achieve of PC is

signal trans:std_logic_vector(7 downto 0):="00000000";

begin

process(clk)

begin

if(clk'event and clk='0') then

if(IN_PC='1' and LD_PC='0') then

trans<=trans+"00000001";

elsif(IN_PC='0' and LD_PC='1') then

trans<=a;

else

trans<=trans;

end if;

else

trans<=trans;

end if;

end process;

c<=trans;

end achieve;

④ 编译与调试。确保顶层实现的命名和工程名一致。编译成功。

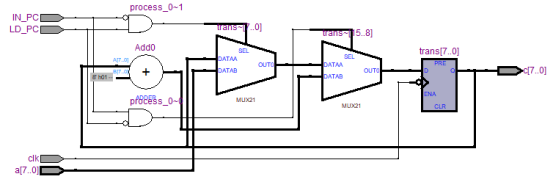

⑤ 查看RTL视图。

⑥ 结果分析及结论。

如RTL图所示,在时钟下降沿时,若IN_PC=1,LD_PC=0,则c[7…0]中数据自加1;若IN_PC=0,LD_PC=1,a[7…0]信号传入c[7…0]中

⑦ 功能仿真的波形及验证。

a.新建波形文件。

b.生成网表,功能仿真。生成网表成功。

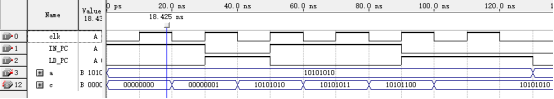

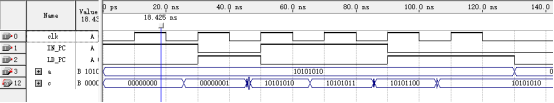

功能仿真成功。功能仿真波形图如图所示:

c.结果分析及结论

20.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,c=00000000+00000001=00000001,仿真无误。

40.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,c=a=10101010,仿真无误。

60.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,c=10101010+00000001=10101011,仿真无误。

80.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,c=10101011+00000001=10101100,仿真无误。

100.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,c=a=10101010,仿真无误。

120.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,c=a=10101010,仿真无误。

⑧ 实现时序仿真。

a.时序仿真成功。

b.时序仿真波形图如下:

c.结果分析及结论

20.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,因为存在延时,一段时间后c=00000000+00000001=00000001,仿真无误。

40.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,因为存在延时,一段时间后c=a=10101010,仿真无误。

60.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,因为存在延时,一段时间后c=10101010+00000001=10101011,仿真无误。

80.0ns时,处于时钟下降沿,IN_PC=1,LD_PC=0,对c进行自加操作,因为存在延时,一段时间后c=10101011+00000001=10101100,仿真无误。

100.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,因为存在延时,一段时间后c=a=10101010,仿真无误。

120.0ns时,处于时钟下降沿,IN_PC=0,LD_PC=1,对c进行传输a值操作,因为存在延时,一段时间后c=a=10101010,仿真无误。

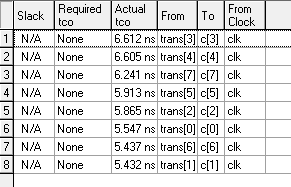

d.编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

从trans3到c3耗时最长,为6.612ns,从trans1到c1耗时最短,为5.432ns,可结果由耗时最长的那个决定,故整体耗时为6.612ns。

925

925

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?