DM365 and DM368 Major System Block Clocking Feature Differences

| DM365-216 | DM365-270 | DM365-300 | DM368 | |

| ARM926 RISC | 216 MHz | 270 MHz | 300 MHz | 432 MHz |

| Co-Processor(HDVICP) | 173 MHz | 216 MHz | 270 MHz | 340 MHz |

| Co-Processor(MJCP) | 173 MHz | 216 MHz | 270 MHz | 340 MHz |

| DDR2 | 173 MHz | 216 MHz | 270 MHz | 340 MHz |

| mDDR | 168 MHz | 168 MHz | 168 MHz | 168 MHz |

| VPSS Logic Block | 173 MHz | 216 MHz | 270 MHz | 340 MHz |

| Peripheral System Bus and EDMA | 86.5 MHz | 108 MHz | 135 MHz | 170 MHz |

| VPBE-VENC | 27 MHz | 74.25 MHz | 74.25 MHz | 74.25 MHz |

| VPFE | 120 MHz | 120 MHz | 120MHz | 120 MHz |

在源码flash_utils/DM36x/Common/src/device.c中对不同的Soc时钟频率进行配置

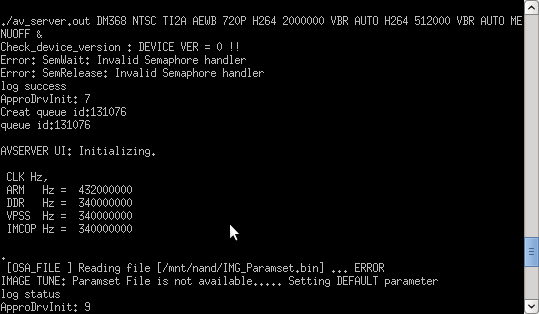

配置为OSC(外部时钟)24MHz,ARM 432MHz,DDR 340MHz即DM368

PLL1配置

Uint32 DEVICE_PLL1Init_432ARM_340DDR2_OSC24()

{

unsigned int CLKSRC=0x0; /*CLKSRC=1 =>External Oscilator

CLKSRC=0 => Onchip oscilator */

/*Power up the PLL*/

PLL1->PLLCTL &= 0xFFFFFFFD;

PLL1->PLLCTL &= 0xFFFFFEFF;

PLL1->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL1->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL1->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(150);

// PLLRST=1(reset assert)

PLL1->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL1->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL1

PLL1->PLLM = 85; // M=85; VCO will 24*2M/N+1 = 680Mhz

PLL1->PREDIV = 0x8000|0x5; // N = 5

PLL1->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

//Program the PostDiv for PLL1

PLL1->POSTDIV = 0x8000;

// Post divider setting for PLL1

PLL1->PLLDIV1 = 0x801B; //POST DIV 680/28=24.3 Mhz->USB PHY

PLL1->PLLDIV2 = 0x8001; //POST DIV 680/2=340Mhz->ARM926/ARM968

PLL1->PLLDIV3 = 0x8001; // POST DIV 680/2 = 340Mhz -> MJCP/HDVICP

PLL1->PLLDIV4 = 0x8003; // POST DIV 680/4 = 170Mhz -> EDMA/Peripheral CFG0 (1/2 Kaleido clock)

PLL1->PLLDIV5 = 0x8001; // POST DIV 680/2 = 340Mhz -> VPSS (max 270)

PLL1->PLLDIV6 = 0x8008; // POST DIV 680/9 = 75.6Mhz -> VENC

PLL1->PLLDIV7 = 0x8000; // POST DIV 680/1 = 680Mhz -> DDRx2

PLL1->PLLDIV8 = 0x800D; // POST DIV 680/14= 48.6Mhz-> MMC0/SD0

PLL1->PLLDIV9 = 0x801B; // POST DIV 680/28 = 24.3Mhz-> CLKOUT

UTIL_waitLoop(300);

/*Set the GOSET bit */

PLL1->PLLCMD = 0x00000001; // Go

UTIL_waitLoop(300);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL0_CONFIG) & 0x07000000) == 0x07000000));

/*Enable the PLL Bit of PLLCTL*/

PLL1->PLLCTL |= 0x00000001; // PLLEN=0

return E_PASS;

}PLL2配置

Uint32 DEVICE_PLL2Init_432ARM_340DDR2_OSC24()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL2->PLLCTL &= 0xFFFFFFFD;

/*Select the Clock Mode as Onchip Oscilator or External Clock on MXI pin*/

/*VDB has input on MXI pin */

PLL2->PLLCTL &= 0xFFFFFEFF;

PLL2->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL2->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL2->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(50);

// PLLRST=1(reset assert)

PLL2->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL2->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL2

PLL2->PLLM = 9; // M=135; VCO will 24*2M/N+1 = 432Mhz

PLL2->PREDIV = 0x8000| 0x0; // N = 0

PLL2->POSTDIV = 0x8000;

PLL2->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

PLL2->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

PLL2->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

PLL2->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

// Post divider setting for PLL2

PLL2->PLLDIV1 = 0x8011; // POST DIV 432/18=24 Mhz ->USB PHY

PLL2->PLLDIV2 = 0x8000; // POST DIV 432/1=432 Mhz -> ARM926/HDVICP Cont

PLL2->PLLDIV3 = 0x8001; // POST DIV 432/2=216 Mhz -> DDRx2

PLL2->PLLDIV4 = 0x8014; // POST DIV 432/21= 20.5714 Mhz->VOICE

PLL2->PLLDIV5 = 0x800F; // POST DIV 432/16=27 Mhz -> VENC

PLL2->PLLCMD = 0x00000001;

UTIL_waitLoop(150);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL1_CONFIG) & 0x07000000) == 0x07000000));

UTIL_waitLoop(4100);

//Enable the PLL2

PLL2->PLLCTL |= 0x00000001; // PLLEN=0

//do this after PLL's have been set up

SYSTEM->PERI_CLKCTRL = 0x36ED027C;

return E_PASS;

}DDR2配置

Uint32 DEVICE_DDR2Init_432ARM_340DDR2_OSC24()

{

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) & 0xFFFF9F3F;

// Set bit CLRZ (bit 13)

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) | 0x00002000;

// Check VTP READY Status

while( !(SYSTEM->VTPIOCR & 0x8000));

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

//SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004000;

// Set bit LOCK(bit7) and PWRSAVE (bit8)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00000080;

// Powerdown VTP as it is locked (bit 6)

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004040;

// Wait for calibration to complete

UTIL_waitLoop( 150 );

// Set the DDR2 to synreset, then enable it again

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

DDR->DDRPHYCR = 0x000000C6;

DDR->SDBCR = 0x00D34A32; //Program SDRAM Bank Config Register

DDR->SDBCR = 0x0053CA32;

DDR->SDTIMR =0x57257CD2; //Program SDRAM Timing Control Register1

DDR->SDTIMR2 =0x422EC742; //Program SDRAM Timing Control Register2

DDR->PBBPR = 0x000000F0;

DDR->SDBCR = 0x00534A32; //Program SDRAM Bank Config Register

DDR->SDRCR = 0xA5C; //Program SDRAM Refresh Control Register

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

while(!(DDR->SDRSTAT&0x04));

return E_PASS;

}

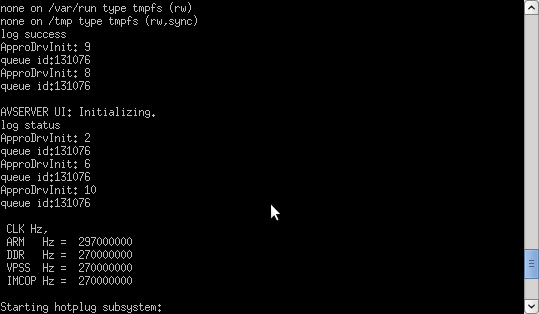

配置为OSC 24MHz,ARM 297MHz,DDR 270Mhz即DM365-300

PLL1配置

Uint32 DEVICE_PLL1Init_297ARM_270DDR2_OSC24()

{

unsigned int CLKSRC=0x0; /*CLKSRC=1 =>External Oscilator

CLKSRC=0 => Onchip oscilator */

/*Power up the PLL*/

PLL1->PLLCTL &= 0xFFFFFFFD;

PLL1->PLLCTL &= 0xFFFFFEFF;

PLL1->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL1->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL1->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(150);

// PLLRST=1(reset assert)

PLL1->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL1->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL1

PLL1->PLLM = 0x2D; // M=45 ; VCO will 24*2M/N+1 = 540Mhz

PLL1->PREDIV = 0x8000|0x3; // N=3

PLL1->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

//Program the PostDiv for PLL1

PLL1->POSTDIV = 0x8000;

// Post divider setting for PLL1

PLL1->PLLDIV1 = 0x8015; // POST DIV 540/22=24.54 Mhz->USB PHY

PLL1->PLLDIV2 = 0x8001; //not use

PLL1->PLLDIV3 = 0x8001; // POST DIV 540/2 = 270Mhz -> MJCP/HDVICP

PLL1->PLLDIV4 = 0x8003; // POST DIV 540/4 = 135Mhz -> EDMA/Peripheral CFG0 (1/2 Kaleido clock)

PLL1->PLLDIV5 = 0x8001; // POST DIV 540/2 = 270Mhz -> VPSS (max 270)

PLL1->PLLDIV6 = 0x8013; // POST DIV 540/20 = 27Mhz -> VENC alternate for SD

PLL1->PLLDIV7 = 0x8000; // POST DIV 540/2 = 270Mhz -> DDR

PLL1->PLLDIV8 = 0x800A; // POST DIV 540/11 = 49.1Mhz-> MMC0/SD0

PLL1->PLLDIV9 = 0x8013; // POST DIV 540/20 = 27Mhz-> CLKOUT

UTIL_waitLoop(300);

/*Set the GOSET bit */

PLL1->PLLCMD = 0x00000001; // Go

UTIL_waitLoop(300);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL0_CONFIG) & 0x07000000) == 0x07000000));

/*Enable the PLL Bit of PLLCTL*/

PLL1->PLLCTL |= 0x00000001; // PLLEN=0

return E_PASS;

}PLL2配置

Uint32 DEVICE_PLL2Init_297ARM_270DDR2_OSC24()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL2->PLLCTL &= 0xFFFFFFFD;

/*Select the Clock Mode as Onchip Oscilator or External Clock on MXI pin*/

/*VDB has input on MXI pin */

PLL2->PLLCTL &= 0xFFFFFEFF;

PLL2->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL2->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL2->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(50);

// PLLRST=1(reset assert)

PLL2->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL2->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL2

PLL2->PLLM = 0x63; // VCO will 24*2M/N+1 = 594Mhz

PLL2->PREDIV = 0x8000|0x7;

PLL2->POSTDIV = 0x8000;

PLL2->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

PLL2->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

PLL2->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

PLL2->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

// Post divider setting for PLL2

PLL2->PLLDIV1 = 0x801E; // 594/31=19.16 Mhz ->USB PHY

PLL2->PLLDIV2 = 0x8001; // 594/2 =297 Mhz -> ARM

PLL2->PLLDIV3 = 0x8001; // POST DIV 594/2=297 Mhz -> DDRx2

PLL2->PLLDIV4 = 0x8004; // POST DIV 594/5=118.8 Mhz -> VOICE

PLL2->PLLDIV5 = 0x8007; // POST DIV 594/8 = 74.25 Mhz ->VIDEO HD

//GoCmd for PostDivider to take effect

PLL2->PLLCMD = 0x00000001;

UTIL_waitLoop(150);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL1_CONFIG) & 0x07000000) == 0x07000000));

UTIL_waitLoop(4100);

//Enable the PLL2

PLL2->PLLCTL |= 0x00000001; // PLLEN=0

//do this after PLL's have been set up

SYSTEM->PERI_CLKCTRL = 0x36ED0E7C; //sample rate 2.048Mhz

return E_PASS;

}DDR2配置

Uint32 DEVICE_DDR2Init_297ARM_270DDR2_OSC24()

{

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) & 0xFFFF9F3F;

// Set bit CLRZ (bit 13)

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) | 0x00002000;

// Check VTP READY Status

while( !(SYSTEM->VTPIOCR & 0x8000));

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

//SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004000;

// Set bit LOCK(bit7) and PWRSAVE (bit8)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00000080;

// Powerdown VTP as it is locked (bit 6)

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004040;

// Wait for calibration to complete

UTIL_waitLoop( 150 );

// Set the DDR2 to synreset, then enable it again

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

DDR->DDRPHYCR = 0x000000C6;

DDR->SDBCR = 0x00D34A32; //Program SDRAM Bank Config Register

DDR->SDBCR = 0x0053CA32;

DDR->SDTIMR =0x44DC63D2; //Program SDRAM Timing Control Register1

DDR->SDTIMR2 =0x4225C742; //Program SDRAM Timing Control Register2

DDR->PBBPR = 0x000000F0;

DDR->SDBCR = 0x00534A32; //Program SDRAM Bank Config Register

DDR->SDRCR = 0x83A; //Program SDRAM Refresh Control Register

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

while(!(DDR->SDRSTAT&0x04));

return E_PASS;

}

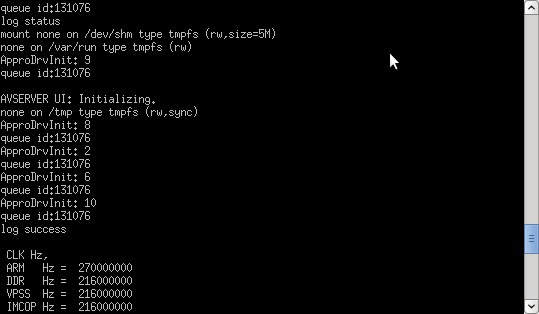

配置为OSC 24MHz,ARM 270MHz,DDR 216MHz即DM365-270

PLL1配置

Uint32 DEVICE_PLL1Init_270ARM_216DDR2_OSC24( )

{

unsigned int CLKSRC=0x0;

unsigned int j;

/*Power up the PLL*/

PLL1->PLLCTL &= 0xFFFFFFFD;

PLL1->PLLCTL &= 0xFFFFFEFF;

PLL1->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL1->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL1->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(150);

// PLLRST=1(reset assert)

PLL1->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL1->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL1

PLL1->PLLM = 0x9; // VCO will 24*2M/N+1 = 432 Mhz

PLL1->PREDIV = 0x8000|0x0;

PLL1->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

//Program the PostDiv for PLL1

PLL1->POSTDIV = 0x8000;

// Post divider setting for PLL1

PLL1->PLLDIV2 = 0x8001;

PLL1->PLLDIV3 = 0x8001; // POST DIV 432/2 -> MJCP/HDVICP

PLL1->PLLDIV4 = 0x8003; // POST DIV 432/4 -> EDMA/EDMA CFG

PLL1->PLLDIV5 = 0x8001; // POST DIV 432/2 -> VPSS

PLL1->PLLDIV7 = 0x8000; // POST DIV 432/2 -> DDR

PLL1->PLLDIV8 = 0x8003; // POST DIV 432/4 -> MMC0/SD0

PLL1->PLLDIV9 = 0x8001; // POST DIV 432/2 -> CLKOUT

UTIL_waitLoop(300);

/*Set the GOSET bit */

PLL1->PLLCMD = 0x00000001; // Go

UTIL_waitLoop(300);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL0_CONFIG) & 0x07000000) == 0x07000000));

/*Enable the PLL Bit of PLLCTL*/

PLL1->PLLCTL |= 0x00000001; // PLLEN=0

return E_PASS;

}PLL2配置

Uint32 DEVICE_PLL2Init_270ARM_216DDR2_OSC24()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL2->PLLCTL &= 0xFFFFFFFD;

/*Select the Clock Mode as Onchip Oscilator or External Clock on MXI pin*/

/*VDB has input on MXI pin */

PLL2->PLLCTL &= 0xFFFFFEFF;

PLL2->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL2->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL2->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(50);

// PLLRST=1(reset assert)

PLL2->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL2->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL2

PLL2->PLLM = 0x2D; // VCO will 24*2M/N+1 = 540Mhz

PLL2->PREDIV = 0x8000|0x7;

PLL2->POSTDIV = 0x8000;

PLL2->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

PLL2->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

PLL2->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

PLL2->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

// Post divider setting for PLL2

PLL2->PLLDIV2 = 0x8000; // 270/1 =270 Mhz -> ARM

PLL2->PLLDIV4 = 0x8005; // POST DIV 270/6 VOICE

PLL2->PLLDIV5 = 0x8009; // POST DIV 270/10 = 27MHZ ->VIDEO SD

//GoCmd for PostDivider to take effect

PLL2->PLLCMD = 0x00000001;

UTIL_waitLoop(150);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL1_CONFIG) & 0x07000000) == 0x07000000));

UTIL_waitLoop(4100);

//Enable the PLL2

PLL2->PLLCTL |= 0x00000001; // PLLEN=0

//do this after PLL's have been set up

SYSTEM->PERI_CLKCTRL = 0x243F04FC;

return E_PASS;

}DDR2配置

Uint32 DEVICE_DDR2Init_270ARM_216DDR2_OSC24()

{

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) & 0xFFFF9F3F;

// Set bit CLRZ (bit 13)

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) | 0x00002000;

// Check VTP READY Status

while( !(SYSTEM->VTPIOCR & 0x8000));

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

//SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004000;

// Set bit LOCK(bit7) and PWRSAVE (bit8)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00000080;

// Powerdown VTP as it is locked (bit 6)

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004040;

// Wait for calibration to complete

UTIL_waitLoop( 150 );

// Set the DDR2 to synreset, then enable it again

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

DDR->DDRPHYCR = 0x000000C5;

DDR->SDBCR = 0x08D34832; //Program SDRAM Bank Config Register

DDR->SDBCR = 0x0853C832;

DDR->SDTIMR = 0x369342D1; //Program SDRAM Timing Control Register1

DDR->SDTIMR2 = 0x421DC702; //Program SDRAM Timing Control Register2

DDR->PBBPR = 0x000000FE;

DDR->SDBCR = 0x08534832; //Program SDRAM Bank Config Register

DDR->SDRCR = 0x00000695; //Program SDRAM Refresh Control Register

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

return E_PASS;

}

配置为OSC24MHz,ARM 216MHz,DDR 173MHz即DM365-216

PLL1配置

Uint32 DEVICE_PLL1Init_ARM216_DDR173_OSC24()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL1->PLLCTL &= 0xFFFFFFFD;

PLL1->PLLCTL &= 0xFFFFFEFF;

PLL1->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL1->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL1->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(150);

// PLLRST=1(reset assert)

PLL1->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL1->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL1

PLL1->PLLM = 0x88; // VCO will 24*2M/N+1 = 343.58 Mhz

PLL1->PREDIV = 0x8000|0x12;

PLL1->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

//Program the PostDiv for PLL1

PLL1->POSTDIV = 0x8000;

// Post divider setting for PLL1

PLL1->PLLDIV2 = 0x8001;

PLL1->PLLDIV3 = 0x8001; // POST DIV 343.58/2 -> MJCP/HDVICP

PLL1->PLLDIV4 = 0x8003; // POST DIV 343.58/4 -> EDMA/EDMA CFG

PLL1->PLLDIV5 = 0x8001; // POST DIV 343.58/2 -> VPSS

PLL1->PLLDIV7 = 0x8000; // POST DIV 343.58/2 -> DDR

PLL1->PLLDIV8 = 0x8003; // POST DIV 343.58/4 -> MMC0/SD0

PLL1->PLLDIV9 = 0x8001; // POST DIV 343.58/2 -> CLKOUT

UTIL_waitLoop(300);

/*Set the GOSET bit */

PLL1->PLLCMD = 0x00000001; // Go

UTIL_waitLoop(300);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL0_CONFIG) & 0x07000000) == 0x07000000));

/*Enable the PLL Bit of PLLCTL*/

PLL1->PLLCTL |= 0x00000001; // PLLEN=0

return E_PASS;

} PLL2配置

Uint32 DEVICE_PLL2Init_ARM216_DDR173_OSC24()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL2->PLLCTL &= 0xFFFFFFFD;

/*Select the Clock Mode as Onchip Oscilator or External Clock on MXI pin*/

/*VDB has input on MXI pin */

PLL2->PLLCTL &= 0xFFFFFEFF;

PLL2->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL2->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL2->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(50);

// PLLRST=1(reset assert)

PLL2->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL2->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL2

PLL2->PLLM = 0x9; // VCO will 24*2M/N+1 = 432Mhz

PLL2->PREDIV = 0x8000|0x0;

PLL2->POSTDIV = 0x8000;

PLL2->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

PLL2->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

PLL2->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

PLL2->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

// Post divider setting for PLL2

PLL2->PLLDIV2 = 0x8001; // 432/2 =216 Mhz -> ARM

//PLL2->PLLDIV4 = 0x8068; // POST DIV 432/106 VOICE

PLL2->PLLDIV5 = 0x800F; // POST DIV 432/16 = 27MHZ ->VIDEO SD

//GoCmd for PostDivider to take effect

PLL2->PLLCMD = 0x00000001;

UTIL_waitLoop(150);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL1_CONFIG) & 0x07000000) == 0x07000000));

UTIL_waitLoop(4100);

//Enable the PLL2

PLL2->PLLCTL |= 0x00000001; // PLLEN=0

//do this after PLL's have been set up

SYSTEM->PERI_CLKCTRL = 0x243F04FC;

return E_PASS;

} DDR2配置

Uint32 DEVICE_DDR2Init_ARM216_DDR173_OSC24()

{

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) & 0xFFFF9F3F;

// Set bit CLRZ (bit 13)

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) | 0x00002000;

// Check VTP READY Status

while( !(SYSTEM->VTPIOCR & 0x8000));

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

//SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004000;

// Set bit LOCK(bit7) and PWRSAVE (bit8)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00000080;

// Powerdown VTP as it is locked (bit 6)

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004040;

// Wait for calibration to complete

UTIL_waitLoop( 150 );

// Set the DDR2 to synreset, then enable it again

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

DDR->DDRPHYCR = 0x000000C6;

DDR->SDBCR = 0x08D34832; //Program SDRAM Bank Config Register

DDR->SDBCR = 0x0853C832;

DDR->SDTIMR = 0x369342D1; //Program SDRAM Timing Control Register1

DDR->SDTIMR2 = 0x421DC702; //Program SDRAM Timing Control Register2

DDR->PBBPR = 0x000000FE;

DDR->SDBCR = 0x08534832; //Program SDRAM Bank Config Register

DDR->SDRCR = 0x00000695; //Program SDRAM Refresh Control Register

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

return E_PASS;

}

配置为OSC19.2MHz,ARM 216MHz,DDR 173MHz即DM365-216

PLL1配置

Uint32 DEVICE_PLL1Init_216ARM_173DDR2_OSC19P2MHZ()

{

unsigned int CLKSRC=0x0;

unsigned int j;

/*Power up the PLL*/

PLL1->PLLCTL &= 0xFFFFFFFD;

PLL1->PLLCTL &= 0xFFFFFEFF;

PLL1->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL1->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL1->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(150);

// PLLRST=1(reset assert)

PLL1->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL1->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL1

PLL1->PLLM = 0x2d; // VCO will 24*2M/N+1 = 432 Mhz

PLL1->PREDIV = 0x8000|0x3;

PLL1->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

// for(j=0; j<0x100; j++) {}

PLL1->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

//Program the PostDiv for PLL1

PLL1->POSTDIV = 0x8000;

// Post divider setting for PLL1

PLL1->PLLDIV2 = 0x8001;

PLL1->PLLDIV3 = 0x8001; // POST DIV 432/2 -> MJCP/HDVICP

PLL1->PLLDIV4 = 0x8003; // POST DIV 432/4 -> EDMA/EDMA CFG

PLL1->PLLDIV5 = 0x8003; // POST DIV 432/4 -> VPSS

PLL1->PLLDIV6 = 0x800f; // POST DIV 432/16 - 27 MHZ ->VENC SD

PLL1->PLLDIV7 = 0x8000;

PLL1->PLLDIV8 = 0x8003; // POST DIV 432/4 -> MMC0/SD0

PLL1->PLLDIV9 = 0x8001; // POST DIV 432/2 -> CLKOUT

UTIL_waitLoop(300);

/*Set the GOSET bit */

PLL1->PLLCMD = 0x00000001; // Go

UTIL_waitLoop(300);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL0_CONFIG) & 0x07000000) == 0x07000000));

/*Enable the PLL Bit of PLLCTL*/

PLL1->PLLCTL |= 0x00000001; // PLLEN=0

return E_PASS;

}PLL2配置

Uint32 DEVICE_PLL2Init_216ARM_173DDR2_OSC19P2MHZ()

{

unsigned int CLKSRC=0x0;

/*Power up the PLL*/

PLL2->PLLCTL &= 0xFFFFFFFD;

/*Select the Clock Mode as Onchip Oscilator or External Clock on MXI pin*/

/*VDB has input on MXI pin */

PLL2->PLLCTL &= 0xFFFFFEFF;

PLL2->PLLCTL |= CLKSRC<<8;

/*Set PLLENSRC '0', PLL Enable(PLLEN) selection is controlled through MMR*/

PLL2->PLLCTL &= 0xFFFFFFDF;

/*Set PLLEN=0 => PLL BYPASS MODE*/

PLL2->PLLCTL &= 0xFFFFFFFE;

UTIL_waitLoop(50);

// PLLRST=1(reset assert)

PLL2->PLLCTL |= 0x00000008;

UTIL_waitLoop(300);

/*Bring PLL out of Reset*/

PLL2->PLLCTL &= 0xFFFFFFF7;

//Program the Multiper and Pre-Divider for PLL2

PLL2->PLLM = 0xE0; // VCO will 24*2M/N+1 = 344.064Mhz

PLL2->PREDIV = 0x8000|0x18;

PLL2->POSTDIV = 0x8000;

PLL2->SECCTL = 0x00470000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 1

PLL2->SECCTL = 0x00460000; // Assert TENABLE = 1, TENABLEDIV = 1, TINITZ = 0

PLL2->SECCTL = 0x00400000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 0

PLL2->SECCTL = 0x00410000; // Assert TENABLE = 0, TENABLEDIV = 0, TINITZ = 1

// Post divider setting for PLL2

PLL2->PLLDIV2 = 0x8000;

PLL2->PLLDIV3 = 0x8001; // POST DIV 344.064/2 -> DDR

PLL2->PLLDIV4 = 0x8006;

PLL2->PLLDIV5 = 0x8000;

//GoCmd for PostDivider to take effect

PLL2->PLLCMD = 0x00000001;

UTIL_waitLoop(150);

/*Wait for PLL to LOCK */

while(! (((SYSTEM->PLL1_CONFIG) & 0x07000000) == 0x07000000));

UTIL_waitLoop(4100);

//Enable the PLL2

PLL2->PLLCTL |= 0x00000001; // PLLEN=0

//do this after PLL's have been set up

SYSTEM->PERI_CLKCTRL = 0x0BFF05FC;

return E_PASS;

}DDR2配置

Uint32 DEVICE_DDR2Init_216ARM_173DDR2_OSC19P2MHZ(){

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) & 0xFFFF9F3F;

// Set bit CLRZ (bit 13)

SYSTEM->VTPIOCR = (SYSTEM->VTPIOCR) | 0x00002000;

// Check VTP READY Status

while( !(SYSTEM->VTPIOCR & 0x8000));

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

//SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004000;

// Set bit LOCK(bit7) and PWRSAVE (bit8)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00000080;

// Powerdown VTP as it is locked (bit 6)

// Set bit VTP_IOPWRDWN bit 14 for DDR input buffers)

SYSTEM->VTPIOCR = SYSTEM->VTPIOCR | 0x00004040;

// Wait for calibration to complete

UTIL_waitLoop( 150 );

// Set the DDR2 to synreset, then enable it again

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

DDR->DDRPHYCR = 0x000000C5;

DDR->SDBCR = 0x08D34832; //Program SDRAM Bank Config Register

DDR->SDBCR = 0x0853C832;

DDR->SDTIMR = 0x2C923251; //Program SDRAM Timing Control Register1

DDR->SDTIMR2 = 0x4217C722; //Program SDRAM Timing Control Register2

DDR->PBBPR = 0x000000FE;

DDR->SDBCR = 0x0853483; //Program SDRAM Bank Config Register

DDR->SDRCR = 0x00000546; //Program SDRAM Refresh Control Register

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_SYNCRESET);

DEVICE_LPSCTransition(LPSC_DDR2,0,PSC_ENABLE);

return E_PASS;

}

1528

1528

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?