在本篇文章中,将实现在Xilinx ZYNQ上实现用PL部分驱动VGA显示12bit的彩色图像,涉及到VGA的驱动原理,vivado上的PLL IP和ROM IP的使用以及彩色图像coe文件的生成。最后将提供整个项目代码。

本文所使用的开发板是Miz702(兼容zedboard),软件开发环境:vivado 2015.2

一、VGA的原理

VGA的协议比较简洁,主要是有五个信号线组成,行同步信号 HSYNC,场同步信号VSYNC和3条色彩电压传输信号(R、G、B分别对应)。色彩信

号的电压为 0~0.7V。本次要实现的分辨率是640*480,帧率是60Hz,所需要的时钟是25Mhz.话不多说,直接上图:

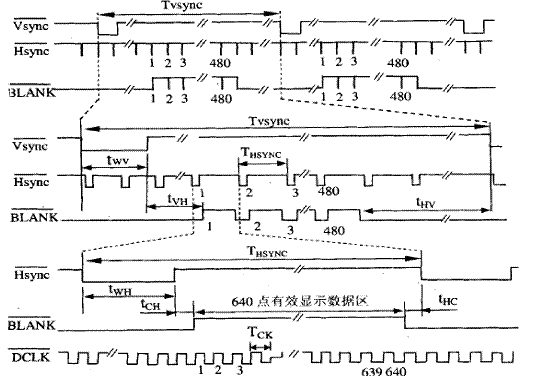

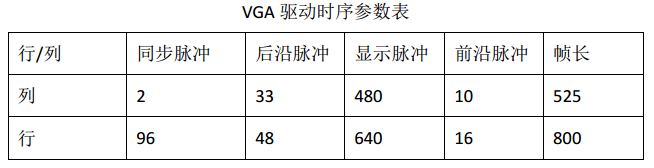

VGA 时序图

需要注意的是,VGA的时序图和参数表可以看出,每帧需要525个vsync脉冲,在每个vsync的周期中,即Tvsync,又包含着800个hsync脉冲,而图像RGB的有效时间在hsync的640个显示脉冲之中。

二、逻辑实现

//vga_sync.v VGA同步控制逻辑

module vga_sync(

input wire clk,

input wire rst_n,

output wire video_en, //数据有效

output reg hsync, //场同步信号

output reg vsync, //行同步信号

output wire [9:0] pixel_x, //待显示待像素的x坐标

output wire [9:0] pixel_y //待显示待像素的y坐标

);

reg [9:0] pixel_cnt;

reg [9:0] line_cnt;

reg v_video_en;

reg h_video_en;

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

pixel_cnt <= 10'b0;

end

else

本文介绍了如何在ZYNQ-7000 FPGA平台上使用PL部分驱动VGA显示640x480分辨率的12bit彩色图像。通过理解VGA的原理,配置PLL和ROM IP,以及生成coe文件,最终实现了图像的显示。详细步骤包括VGA时序、逻辑实现、coe文件生成和代码烧录。

本文介绍了如何在ZYNQ-7000 FPGA平台上使用PL部分驱动VGA显示640x480分辨率的12bit彩色图像。通过理解VGA的原理,配置PLL和ROM IP,以及生成coe文件,最终实现了图像的显示。详细步骤包括VGA时序、逻辑实现、coe文件生成和代码烧录。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3123

3123

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?