September 28, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52688654

声明:转载请注明作者及出处。

百度百科定义:

SPI(Serial Peripheral Interface–串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。外围设备包括FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI接口应用:

串行flash的读写擦除命令通过SPI接口进行通信。

CPU芯片与FPGA通过SPI接口进行通信。

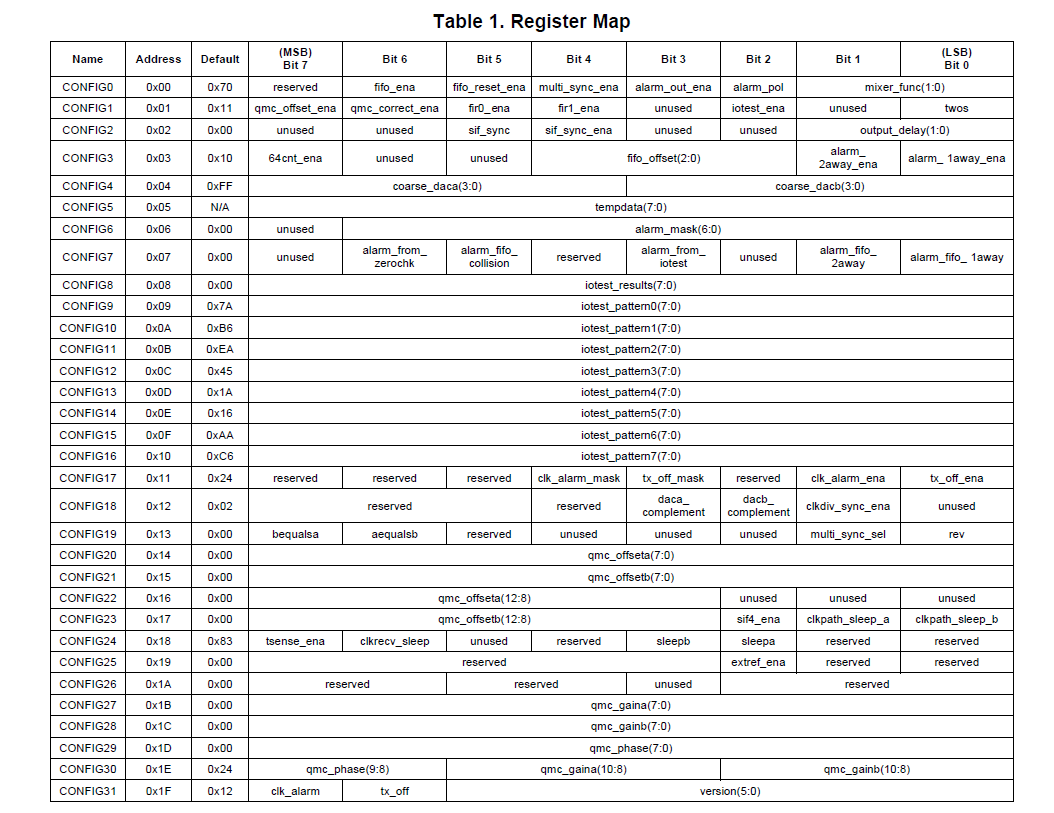

其他功能集成电路芯片参数寄存器配置。(例如DAC芯片内部有很多寄存器(因为芯片有很多功能,要通过设置寄存器不同的开关来打开或关闭相应的功能,一上电去初始化寄存器)需要我们去配置。FPGA一上电也是通过配置芯片里边来读取数据,然后配置FPGA内部的SRAM。FPGA是读取FLASH里边的串行数据,读取完校验完才配置到我们的FPGA的SRAM中去)

速度比串口快,而且是同步传输。

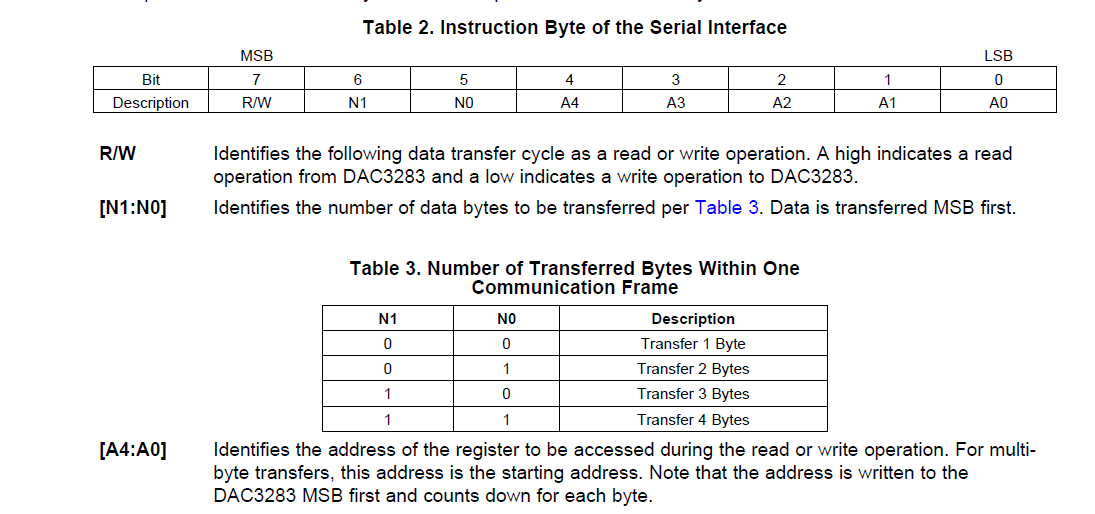

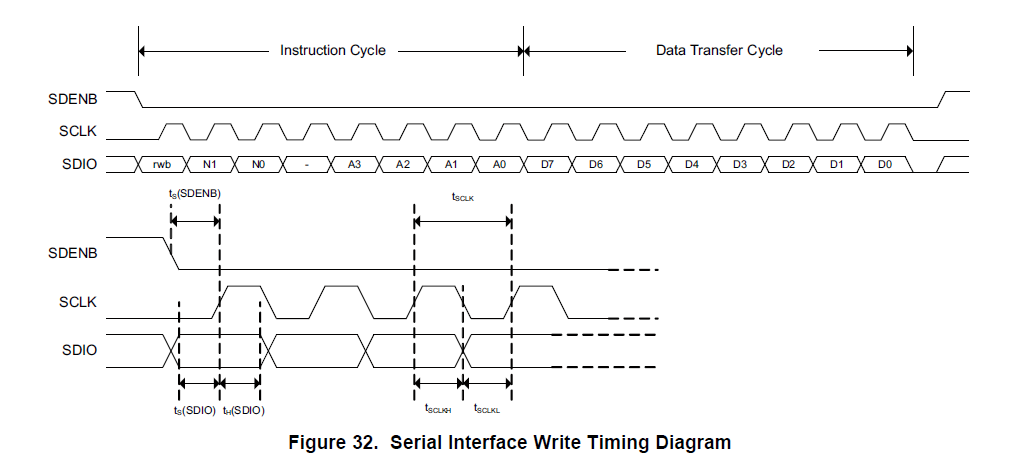

某DAC芯片的SPI配置时序(数字模拟转换器(英语:Digital to analog converter,英文缩写:DAC)是一种将数字信号转换为模拟信号(以电流、电压或电荷的形式)的设备。)

SPI(Serial Peripheral Interface)

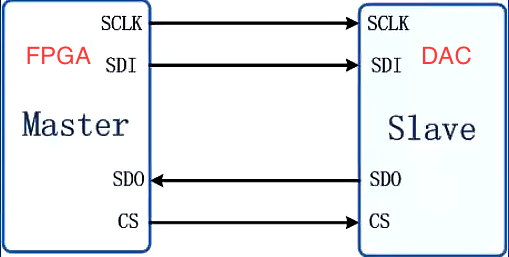

下边是四线SPI(三线的SPI是把SDI和SDO合并成了一个SDIO双向的)

SCLK主机给从机的系统时钟

SDI主机输出给从机的数据。

SDO从机输出给主机的数据

CS:chip select 片选信号,此信号可以使一个主机控制多个从机,此信号有效表示此从机被选中通信。(片选可以理解成选片,很多芯片挂在同一总线上的时候,需要有一个信号来区别总线上的数据和地址由哪个芯片处理,这时就需要一个片选信号CS(chip select),一般是在划分地址空间时,由逻辑电路产生的。在数字电路设计中,一般开路输入管脚呈现为高电平,因此片选信号绝大多数情况下是一个低电平。

带-n的是低电平有效;不带的是高电平有效。)

查看文档DAC3283.pdf

在这种有命令和数据的情况下,可以把命令和数据都存到我们的RAM中去,这样我们在读出来的时候就按照比特,一个比特一个比特的给它发过去就可以了,可以简化逻辑。

这样虽然占用了更多的ram空间,但是节省逻辑空间。因为Block Memory它大小是固定的,比如说它里边的深度是256,比如cycloneIV最小的是m9k,那么它也会占用整个9k的memory,就算用里面的一点也会把整块占用,布局布线和综合。

因此可以把存储数据和命令都存储到ram,方便我们操作。

案例实现:首先数据存储到RAM或ROM中,然后再从RAM或ROM中读出来再发送。

这里有32个寄存器,像这种配置,有些时候我们配置的时候不能连续的配置两个寄存器,每配置完一个寄存器要把使能拉高,停一拍。做FLASH擦出或读写的时候中间有个保护时间,就是说你两次命令需要间隔多长时间。我们中间要隔一定的周期数再发第二个命令。所以,我们发送完一个数据的时候,我们等待一段时间再去发送第二个命令。所以我们把这个顺序流程定义成一个状态机,我们用状态机的方式去控制它的流程。

状态迁移图:

图片

建立一个ram的IP核:

//D:\VivadoProjects\FPGA_From_e_to_c\ex_7\quartus_prj\ipcore_dir\ram_16x32_sr_inst.v

ram_16x32_sr ram_16x32_sr_inst (

.address ( address_sig ),

.clock ( clock_sig ),

.data ( data_sig ),

.wren ( wren_sig ),

.q ( q_sig )

);建立一个.mif文件,用来初始化ram:

--D:\VivadoProjects\FPGA_From_e_to_c\ex_7\quartus_prj\ipcore_dir\ram_16x32_sr.mif

-- Copyright (C) 1991-2013 Altera Corporation

-- Your use of Altera Corporation's design tools, logic functions

-- and other software and tools, and its AMPP partner logic

-- functions, and any outp

本文详细介绍了SPI接口的工作原理及其在FPGA中的应用,包括SPI与串行Flash、CPU之间的通信,以及如何配置DAC芯片。通过使用状态机控制数据传输流程,文章还展示了如何建立RAM IP核和初始化MIF文件进行仿真。

本文详细介绍了SPI接口的工作原理及其在FPGA中的应用,包括SPI与串行Flash、CPU之间的通信,以及如何配置DAC芯片。通过使用状态机控制数据传输流程,文章还展示了如何建立RAM IP核和初始化MIF文件进行仿真。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1059

1059

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?