September 17, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52564050

声明:转载请注明作者及出处。

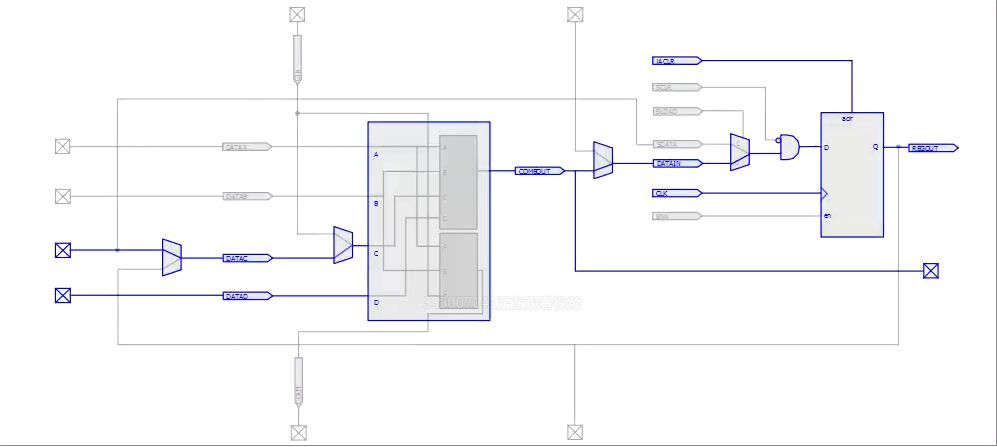

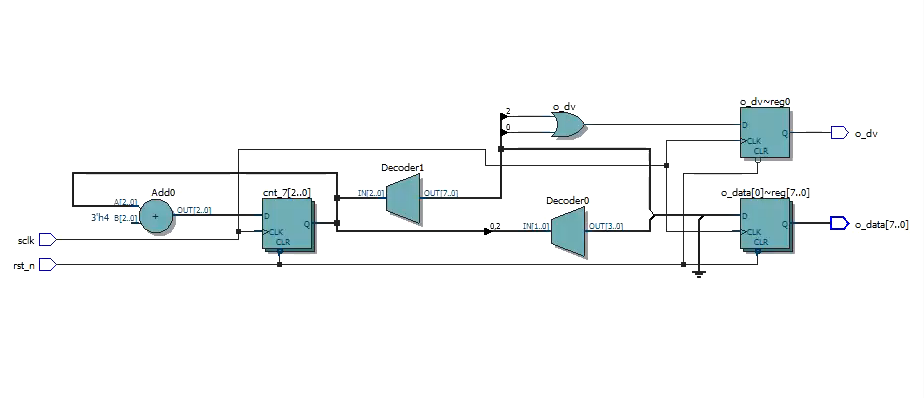

上图,是在Quartus II里显示的最底层,右上方表示一个reg。

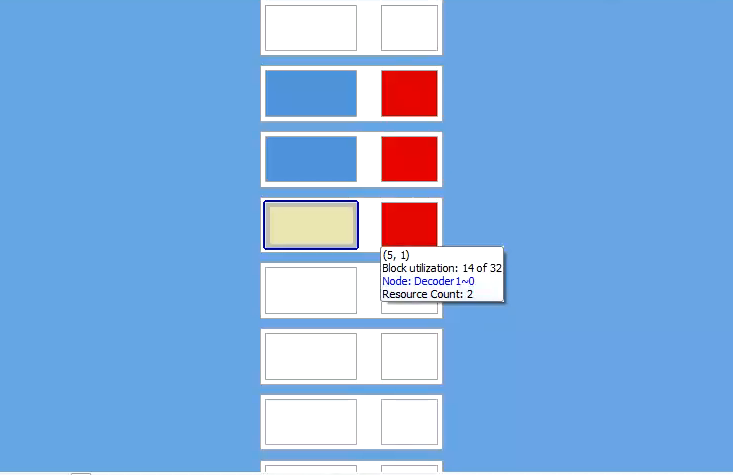

上图,这一个小块叫一个LE,是FPGA的基本单元

上图,这一个大块叫LAB,是逻辑阵列块,里面包含了多个LE

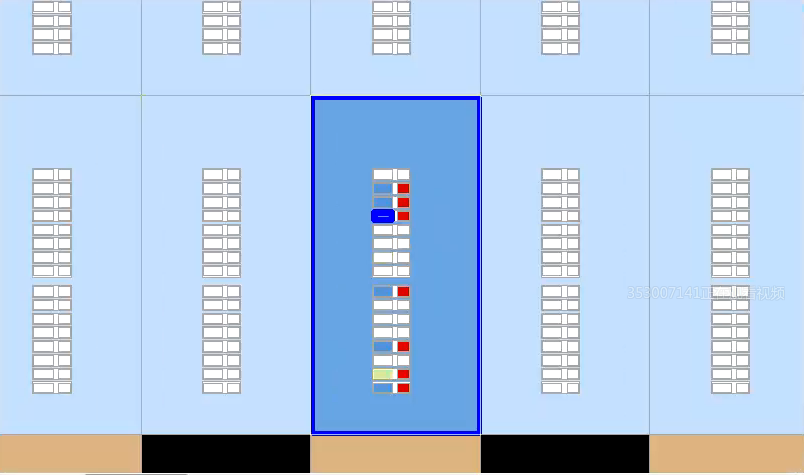

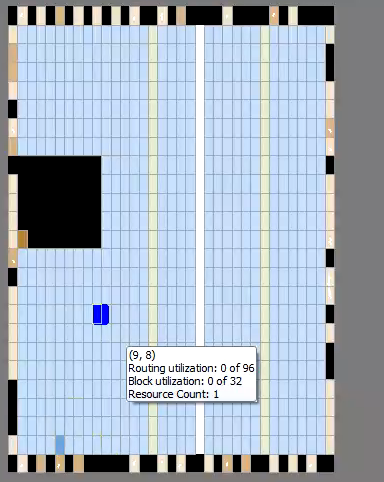

上图,板面上包含了很多个LAB,每个LAB都有对应的坐标

时钟走的线是金线,延时相当小,并且到每一级寄存器的延时都保持一致;

如果我们用数据线,数据线是铜线,它的介质是不一样的,它的特性也不一样。

所以使得我们数据传输的时候出现时序违例。这就是posedge,negedge只用时钟信号而不用其他信号的原因。negedge a,就是指a从1跳变0的那一刻的状态(下降沿)。

module ex_case(

input wire rst_n,

input wire sclk,

output reg o_dv,//使能标志信号,标志数据有效

output reg [7:0] o_data,

//用于数据输入

input wire [9:0] i_data,

input wire [7:0] i_addr

);

reg [2:0] cnt_7;//计数器

//不同功能的寄存器分开always块来写,这样可维护性强,可读性强

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cnt_7<=3'd0;

else

cnt_7<=cnt_7 + 1

本文介绍了Verilog中的case语法和task语法,探讨了在FPGA设计中的应用。通过Quartus II的实例展示了FPGA的基本单元LE和逻辑阵列LAB。时钟信号的时序特性被强调,解释了posedge和negedge仅用于时钟信号的原因,以避免时序违例。

本文介绍了Verilog中的case语法和task语法,探讨了在FPGA设计中的应用。通过Quartus II的实例展示了FPGA的基本单元LE和逻辑阵列LAB。时钟信号的时序特性被强调,解释了posedge和negedge仅用于时钟信号的原因,以避免时序违例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8925

8925

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?