1 SDRAM原理分析

本节先介绍了SDRAM的基本原理,然后介绍了一个具体SDRAM芯片HY57V641620HG的特性和引脚描述。

1.1 SDRAM介绍

DRAM是动态存储器Dynamic RAM的缩写,SDRAM是Synchronous DRAM的缩写,中文就是同步动态存储器的意思。从技术角度上讲,同步动态存储器(SDRAM)是在现有的标准动态存储器中加入同步控制逻辑(一个状态机),利用一个单一的系统时钟同步所有的地址数据和控制信号。使用SDRAM不但能提高系统表现,还能简化设计、提供高速的数据传输。在功能上,它类似常规的DRAM,且也需时钟进行刷新。可以说,SDRAM是一种改善了结构的增强型DRAM。SDRAM 的存储单元可以理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷新(充电)。由此可见,要在系统中使用SDRAM,就要求微处理器具有刷新控制逻辑,或在系统中另外加入刷新控制逻辑电路。SDRAM是多个Bank结构的,一般是一个Bank正在使用,其他Bank处于预充电状态,这样轮流读写和充电就不需要等待了,大大提高了存储器的访问速度。但是要实现这个功能,还必须增加对多个Bank的管理模块,控制Bank来进行预充电,所以在在多个Bank的SDRAM中,会有多根Bank的选择引脚。

1.2 HY57V641620HG的结构

HY57V641620HG是一个8MB的CMOS同步DRAM,尤其适合大容量存储和高带宽的存储场合。HY57V641620HG分为4个Bank,每个Bank大小为2MB。它所有的输入和输出是和时钟输入上升沿同步的,且电平与LVTTL相兼容。内部数据通道提高了带宽。特性如下:

l 单电源供电,电压3.0V~3.6V

l 54引脚TSOP II封装

l 所有引脚与LVTTL接口兼容

l 所有输入输出参考系统时钟

l 具有UDQM或LDQM数据屏蔽功能

l 可编程脉冲宽度和脉冲类型

l 可编程CAS#反应时间

l 自动刷新和自我刷新功能

l 64ms 内4096个自动刷新周期

1 引脚分配图

引脚描述如表所示。

表 RAM引脚描述

| 引脚 | 引脚名 | 描述 |

| CLK | 时钟 | 系统时钟输入 |

| CKE | 时钟使能 | 内部时钟控制信号 |

| CS# | 片选 | 禁止/使能除CLK、CKE和DQM的所有输入 |

| BA0、BA1 | Bank地址 | 选择某个Bank,00~11分别对应Bank0~Bank1 |

| RAS# | 行地址选择 | RAS#为行地址选择,当为低电平时行地址单元 使能 |

| CAS# | 列地址选择 | CAS#为行地址选择,当为低电平时行地址单元使能 |

| WE# | 写使能 | WE#为低时,允许写操作 |

| LDQM/UDQM | 数据输入/输出屏蔽 |

|

| DQ0~DQ15 | 数据输入/输出 | 输入和输出数据 |

| VDD/VSS | 电源/地 | 内部电路和输入缓冲电源供电 |

| VDDQ/VSSQ | 数据输出电源/地 | 输出缓冲电源供电 |

| NC | 未连接 | 不使用,悬空即可 |

2 接口电路与程序设计

本节讲述了HY57V641620HG SDRAM与S 3C 44B0X的电路连接方式和S 3C 44B0X上存储器控制器寄存器的设置,对于SDRAM的读写操作只需一对读写宏就能完成,最后由在一个Main函数中测试了读写操作宏的正确性。

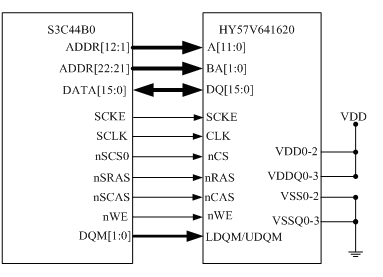

2.1 电路连接

要在系统中使用SDRAM,要求微处理器具有刷新控制逻辑,或在系统中另外加入刷新控制逻辑电路。S 3C 44B0X及其他一些ARM芯片在片内具有独立的SDRAM刷新控制逻辑,可方便地与SDRAM相连接。

SDRAM连接电路图如2所示,它接在Bank6上。HY57V641620HG分成4个Bank;每个Bank的容量为 1M ×16位。Bank的地址由BA1和BA0决定,00对应Bank0、01对应Bankl、10对应Bank2、 11对应Bank3。在每个Bank中,分别用行地址脉冲选通RAS和列地址脉冲选通CAS进行寻址。HY57V641620HG的行地址取地址线A0~A11位,即RA0~RA11;列地址取地址线低8位,即CA0~CA7。SDRAM由S 3C 44B0X专用SDRAM片选信号nSCS0/nGCS6选通,地址空间为0x 0C 000000~0x 0C 7FFFFF。

2 SDRAM连接电路图

2.2 硬件和寄存器设置

由于HY57V641620HG接在Bank6上,首先应当设置BWCON寄存器的第27位~第24位,即ST6、WS6和DW6。ST6决定Bank6上的SRAM是否采用UB/LB,默认为不采用,本实例默认即可,WS6决定Bank6的等待是否使能,默认为禁止等待,本实例也默认即可。DW6时决定Bank6的数据总线宽度。根据HY57V641620HG,本实例将其配置为16位的数据总线宽度,即DW6 = 01。

BANKCON寄存器中的MT位在第四章已经介绍过,将其配置为SDRAM,即MT = 11。Trcd位设置为00,即RAS#信号到CAS#信号的延迟时间为2个时间周期。SCAN位根据HY57V641620HG芯片需设置为8位列地址线。这里还要根据处理器主频来计算刷新计数器REFRESH[10:0]位。计算公式见第四章表4-8。

BANKSIZE寄存器中的SCLKEN位可以取默认值0,也可以为1,在这取1,即减少功耗。BK76MAP位取默认值000刚好满足要求,即32MB/32MB。各寄存器参数设置如下:

;BANKCON6寄存器参数

B6_MT EQU 0x3 ;SDRAM

B6_Trcd EQU 0x0 ;2个时钟周期

B6_SCAN EQU 0x0 ;8bit

;REFRESH寄存器参数

REFEN EQU 0x1 ;刷新使能

TREFMD EQU 0x0 ;CBR/自动刷新

Trp EQU 0x0 ;2个时钟周期

Trc EQU 0x1 ;5个时钟周期

Tchr EQU 0x2 ;3个时钟周期

;REFCNT = 2048 + 1 - MCLK(MHz) * 16

REFCNT EQU 1049 ;刷新周期为16us, MCLK=64MHz 根据系统时钟计算

;SDRAM的刷新数率

;BANKSIZE寄存器参数

SCLKEN EQU 0x1 ;减少功耗

BK67MAP EQU 0x000 ;Bank6和Bank7映射关系为32MB/32MB

;MRSR寄存器参数

B6_WBL EQU 0x0 ;写脉冲长度为0

B6_TM EQU 0x00 ;模式寄存器设置

B6_CL EQU 0x010 ;CAS#延迟时间为2个时间周期

B6_BT EQU 0x0 ;序列脉冲

B6_BL EQU 0x0 ;脉冲长度为1

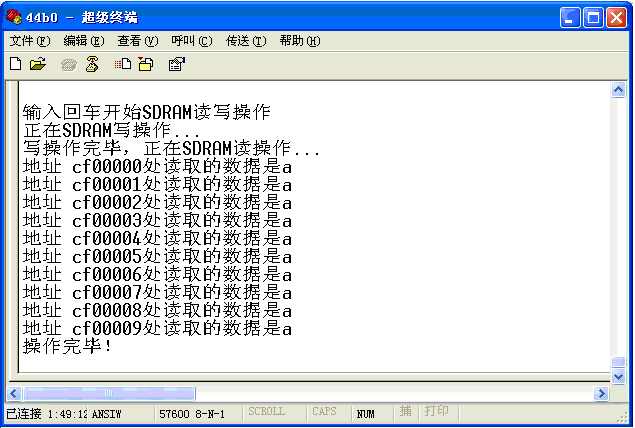

2.3 程序的编写

ARM处理器能自动产生刷新、读写SDRAM的时序,所以本程序比较简单,只要将字符“a”写入0x0cf00000起始的10个地址空间的RAM中,再读取出来校验即可。注意0x 0c 000000为SDRAM的起始地址,为保护靠近0x 0c 000000的运行的程序,实例进行读写的空间要取大一些,这里取0x0cf00000。程序主体如下:

#define WriteSdram(address,data) *((volatile U8 *)(address))=(U8)data //写SDRAM宏

#define ReadSdram(address) *((volatile U8 *)(address)) //读SDRAM宏

void Main (void)

{

……

UartPrintf("/n输入回车开始SDRAM读写操作");

if(UartGetch()=='/r')

{

UartPrintf("/n正在SDRAM写操作…");

j=0x0cf00000;

for(i=0;i<10;i++) //从0x0cf00000开始,写入10个‘a’

{

WriteSdram(j,'a');

j++;

}

j=0x0cf00000;

UartPrintf("/n写操作完毕,正在SDRAM读操作…");

for(i=0;i<10;i++)

{

ReadData = ReadSdram(j); //从0x0cf00000开始,读取10个‘a’

UartPrintf("/n地址%8x处读取的数据是%c", j, ReadData);

j++;

}

UartPrintf("/n操作完毕!");

}

}

2.4 程序运行结果

3 小结

介绍HY57V641620HG SRAM的操作,不像对Flash Rom操作,还需要写入命令字,对RAM的读写操作比较简单,只要在相应的地址进行普通读写就行。使用SDRAM不但能提高系统表现,还能简化设计、提供高速的数据传输。嵌入式一般需要或大或小的RAM空间来保证程序的运行需要。

7171

7171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?