接口名称:DRAM

英文全称:Dynamic Random Access Memory

中文:动态随机存取存储器(常见的系统内存)

标准维护和制定:JEDEC/EIA(JOINT ELECTRON DEVICE ENGINEERING COUNCIL)

核心成员:

网址:www.jedec.org

当前规范:DDR(JESD79)/DDR2 (JESD79-2)/DDR3 (JESD79-3)/DDR4 (JESD79-4)/LPDDR (JESD209)/ LPDDR2 (JESD209-2)/LPDDR3 (JESD209-3) /LPDDR4 (JESD209-4).

最新版本:DDR SDRAM/DDR2/DDR3/DDR4/DDR5(正式标准未公布)

生效时间:2017年10月

下一版本:DDR5(TBD)

说明:DRAM通常是晶体管及电容器所组合,电容器在一秒内重复充电数百次以保存其中的记忆值,DRAM是随机存取内存(RAM)的其中一种,它和只读存储器(ROM)最大的差别是RAM的储存数据会随着电力的消逝而消失。

DRAM的发展史:

-

FPM/EDO:1996年以前应用为主,SOJ包装模式,运作频率和CPU的总线异步。

-

SDRAM:开始导入DRAM运作频率和CPU的总线频率同步.所以称为同步DRAM. 同步控制的技术使得CPU和内存的Timing cycle同步,计算机的整体效率亦大幅提升,目前DRAM都是架构在SDR之上演进而成 。

-

DDR(Double data rate): 同一频率送出2组数据(正/负),速度较SDR快一倍,引入DLL电路.内存速度400~500MHz。

-

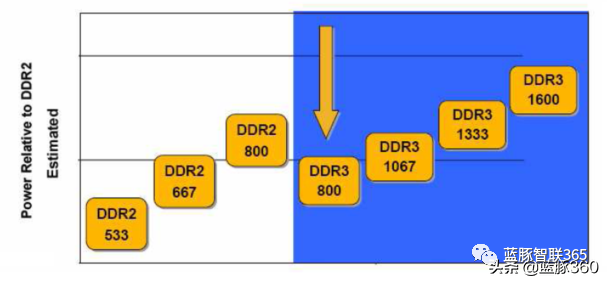

DDR2: 提高内存速度到800~1066 MHz .因应速度提升引入提升讯号质量功能(ex: ODT/OCD..)及command bus新指令(Posted CAS & Additive Latency) .

-

DDR3: 提高内存速度到1066~1866 MHz .持续因应速度提升引入提升信号质量功能, Dynamic ODT, M.P.R/Write level memory training功能。

-

DDR4: 工作电压1.2V,工作频率有2133MHz、2400MHz、2666MHz、2800MHz、3000MHz和3200MHz等分类。

-

DDR5:工作电压1.1V,内存带宽是DDR4的两倍--3.2-6.4Gbps.频率达4800MHz~6400MHz。

一、接口结构

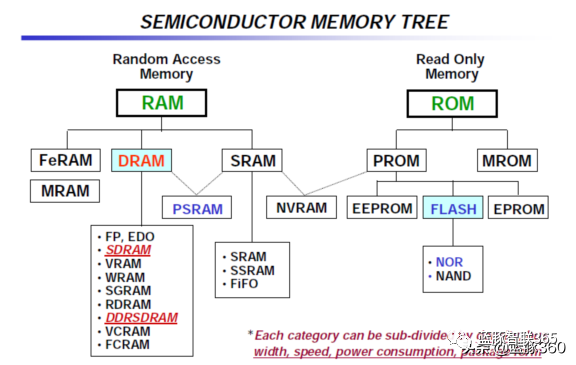

上图是一个半导体存储器的分类树形图。可见DRAM只是RAM中的一种,RAM一般用作缓冲,而ROM一般用作代码存储。缓冲越大,系统的性能将会越好,特别是对于大型操作系统,RAM的性能有时就代表了一个系统的性能。

DDR全称为DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)双倍速率同步动态随机存储器,DDR SDRAM最早是由三星公司于1996年提出, 由日本电气、三菱、富士通、东芝、日立、德州仪器、三星及现代等八家公司协议订立的内存规格,并得到了Intel和AMD等主要芯片组厂商的支持,当前已经从第一代DDR SDRAM发展到DDR4,即将发布DDR5.怎么样区分呢?

DDR SDRAM供电:2.5V

DDR2供电:1.8V

DDR3供电:1.5V

DDR4供电:1.2V

DDR5供电:1.1V

为降低功耗,又发展了LPDDR、LPDDR2、LPDDR3、LPDDR4及DDR3L,它们的供电分别为:

DDR3L供电:1.35V

DDR3U供电:1.25V

LPDDR2供电:1.5V

LPDDR3供电:1.2V

LPDDR4供电:1.1V (采用LVSTL--Low Voltage Swing Terminated Logic)

电气接口:电气接口则由「LVTTL」改变为「SSTL2」。DDR SDRAM则是以数据传输量作为命名原则,例如PC1600以及PC2100,单位 MB/s。所以 DDR SDRAM中的DDR200 其实与 PC1600 是相同的规格,数据传输量为1600MB/s(64bit×100MHz×2÷8=1600MBytes/s),而 DDR266与PC2100 也是一样的情形64bit×133MHz×2÷8=2128MBytes/s。

GDDR(Graphics Double Data Rate):是用于显示的RAM技术,其特点是高带宽、高延时。GDDR5技术实际来源于DDR3,只不过降低了电压,减少了位宽(但支持更多Channel),通过数据编码和读写线分开提高了数据速率(3G~6GT/s)。GDDR5已经使用了将近10年,目前最新的标准是GDDR6。

DRAM具有以下信号线:

-

DQ & DQS : Data input & output pin, DQS is the strobe of Data. The most critical signal in DRAM application.

-

CK & /CK: All of the address & command signal was sampled at the cross point of CK & /CK. Almost all of the DRAM timing related to CK & /CK signals。

-

Control:<CKE, ODT,CS> This group was separate with Address/Command because it will be “Rank” dependent on DIMM application and it is usually “1T” timing that worse than Address/Command signals.

-

Address&/Command : <A0~A15, BA0~BA2, RAS, CAS,WE> Provide the input command and Row/Column address from controller. Also used for MRB setting in initialization stage. Usually “2T” timing for application, so it’s not as worse as the other signals.

二、工作原理

2.1 DRAM CELLL的基本架构

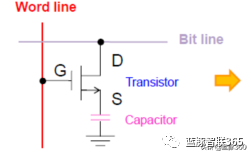

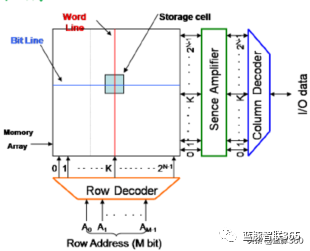

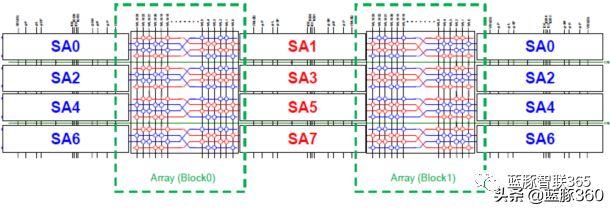

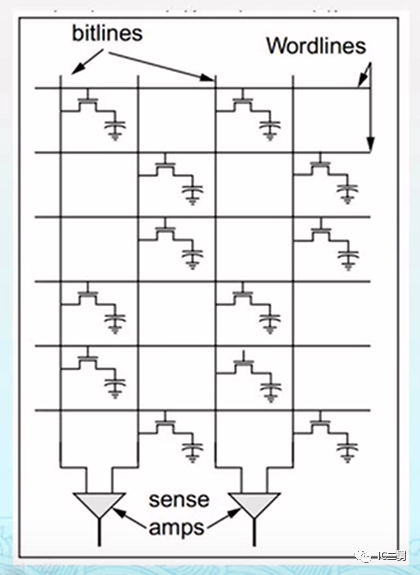

第一个存储器是由INTEL在1970年发明的,1978年日本富士通开发出第一个DRAM存储器。DRAM,即动态随机存取存储器,一个DRAM内存单元包括一个晶体管和一个电容,晶体管负责开关切换,电容负责存储电荷,如下图所示;内存以位(bit)来表示内存容量,每个 储存的最小单元称为Cell。DRAM Cell以数组(Array)方式排列。以行(Column,Y轴)与列(Row,X轴)组合定义 其记忆地址(Address),此地址经由译码 器(Decoder)解码后,对应到Array中的WL(Word Line)与BL(Bit Line),便可对选取的Cell做数据的存取。

SA (Sense Amplifier)感应放大器 : 利用差动放大器的原理,将cell capacitor所读取到的小信号(△V或-△V)放大至VBLH或0,亦即所谓的信号“1”or“0”。每一组SA控制左右两侧的Array(以Block作区分),且负责一组Bit Line pair(BL & /BL)其外挂cell上信号的放大。

容量计算方法:Size=2(C+R+B)xD

C: column address pin number

R: row address pin number

B: bank select pin number

D: DQ pin number

2Gb *8 为例:

R=15 ; C=10 ; D=8 ; B=3 (8个Bank)

Size=2^(15+10+3)x8=2^31=2Gb

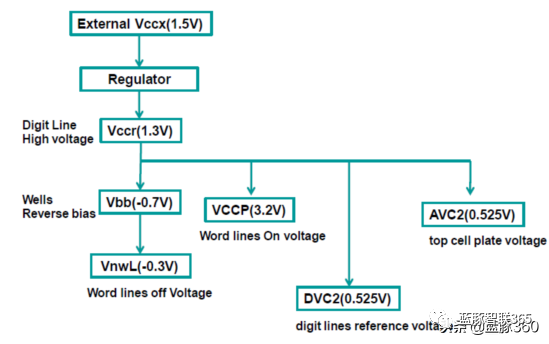

内部偏置电压(以1.5V外部供电的DDR3为例):

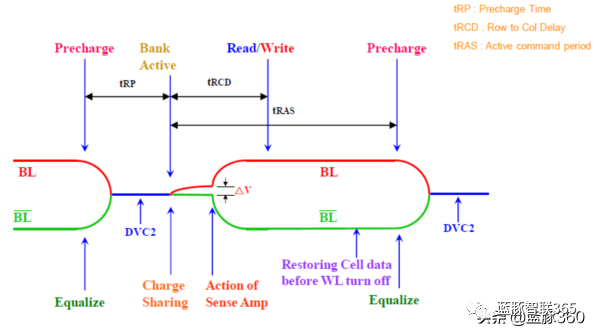

动作原理(状态图)

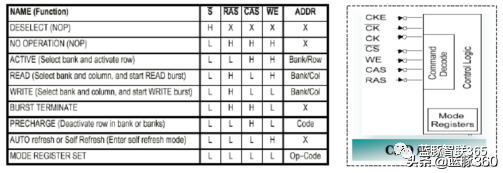

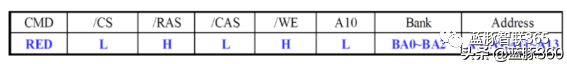

命令表:根据下表执行各种命令。

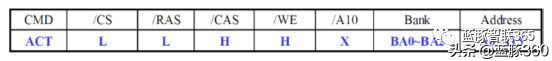

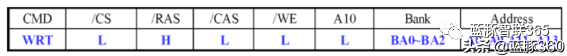

Active Command ACT操作:

/CS => Low : Chip is selected /RAS => Low : Strobe Row Address

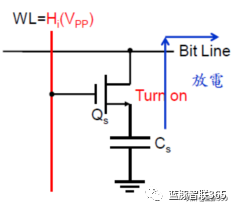

Active是DRAM要能读写数据时的必要动作, 将WL升压使晶体管导通,电荷才能在BL与电容间流动,才能存取资料。

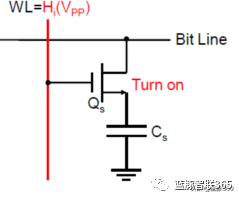

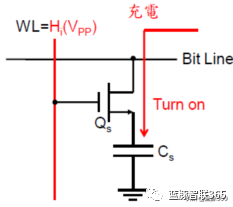

Write Command写操作:

/CS => Low : Chip is selected

/CAS=>Low : Strobe Column Address

/WE => Low : This is a write command

1.Word Line必须处于Active的状态下,建立Bit Line的电压。

2.当Write”1”,电容器自Bin Line经由MoS晶体管充电并储存电荷,藉此写入”1”.

3.当Write”0”,电容器的电荷经由MoS晶体管放电至Bin Line上,藉此写入”0”.

Read Command读操作:

/CS => Low : Chip is selected

/CAS => Low : Strobe Column Address

/WE => High : This is a read command

1.Word Line必须处于Active的状态下,侦测Bit Line上的电位变化。

2.当Cell内的数据为“1”时,电容器的电荷经由MoS晶体管放电至Bit Line上,将使Bit Line的电压瞬间微微提升,侦测电路便可判别出“1”的data

3.当Cell内的资料为“0”时,Bit Line上的电荷经MoS晶体管流向电容器,将使Bit Line的电压

瞬间微微下降,侦测电路便可判别出 “0”的data.

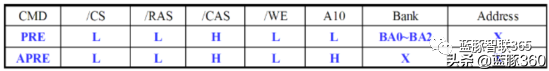

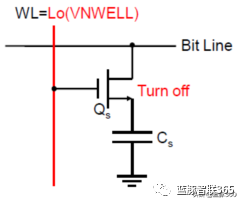

Precharge 预充电操作:

A10 => Low : Pre-Charge one Bank

A10 => High : Pre-Charge all Bank

1.DRAM是将资料经由BL存取于Cell中,BL 升降压时间会影响访问速度,在存取数据及Active动作前先将BL电压提升至1/2VBLH(=VBLEQ),这个动作即为Precharge。

2.Precharge时会将WL关掉(V=VNEWW),使晶体管呈现关闭状态,以免影响Cell储存的

资料。

Refresh Command Operation 刷新操作:

储存在电容器的电子经过一段时间之后,会由于漏电流而逐渐流失,使得储存在电容器的资料无法一直保持。因此为了避免数据流失,每隔一段时间就必须将数据重新写入一次。

Refresh 有三种:

² RAS Only Refresh (ROR)

² Auto Refresh (CBR)

² Self Refresh

带宽的计算

带宽 : Gbyte/sec = data bit(I/O总数) x 数据传输速度(MHz)

举例:

1.系统使用4ea DDR3 1600 128MX8,带宽=32(I/O)x 1600/8=6.4GB/s, 提供系统储存容量= 128x4= 512MB

2.系统使用2ea DDR3 1600 64MX16,带宽=32(I/O)x 1600/8=6.4GB/s, 提供系统储存容量= 64x4= 256M

实际运用上, 若颗粒I/O数一样,1600理论上较1333带宽高20%,但实际上终端客户”使用”的“感受”可能没有差异, 主要原因是系统对DRAM的”Hit rate”不高.

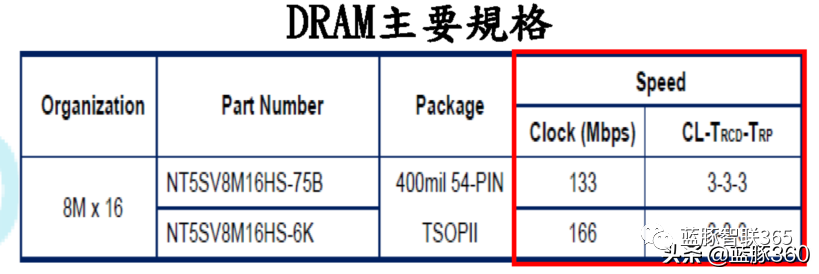

从SDR开始定义,CL-TRCD-TRP为高速内存的重要中心参数,此参数的时间随着制程演进及速度提升改变不大,因为数据传输的物理限制。

EX:

SRD 166 3-3-3 , TRCD=18ns

DDR 400 3-3-3 , TRCD=15ns( 5nsx3)

DDR2 800 6-6-6 , TRCD=15ns( 2.5nsx6)

DDR3 1600 11-11-11 TRCD=13.75ns( 1.25nsx11)

三、应用设计

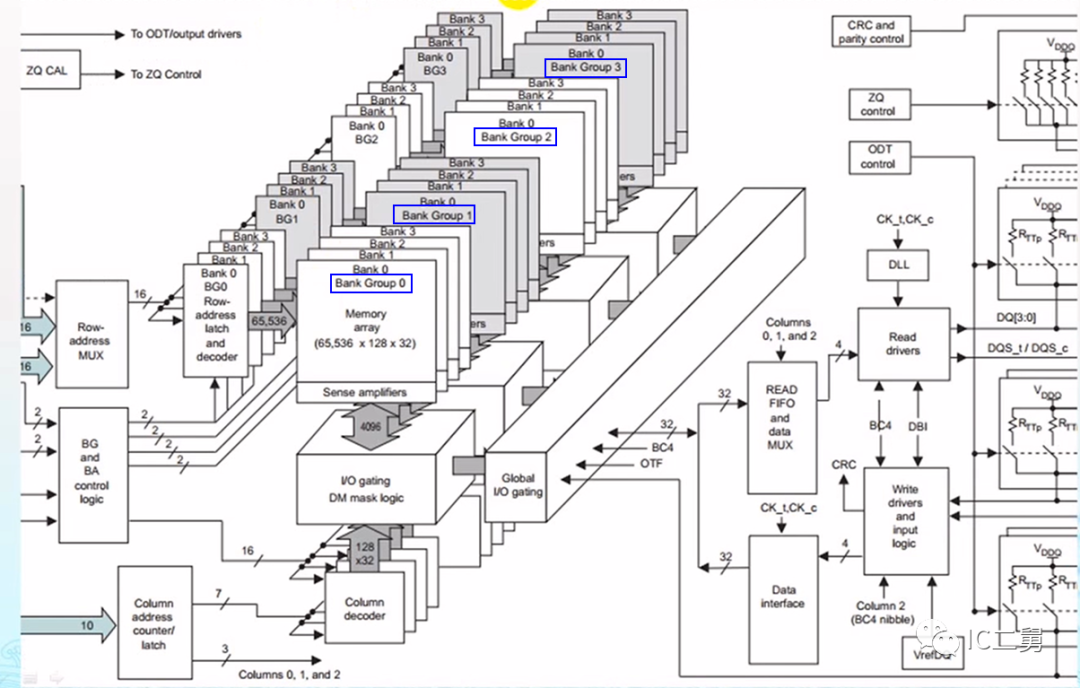

当前我们大部分产品都用到DDR3或DDR3L SDRAM。其原理框图如下图所示:

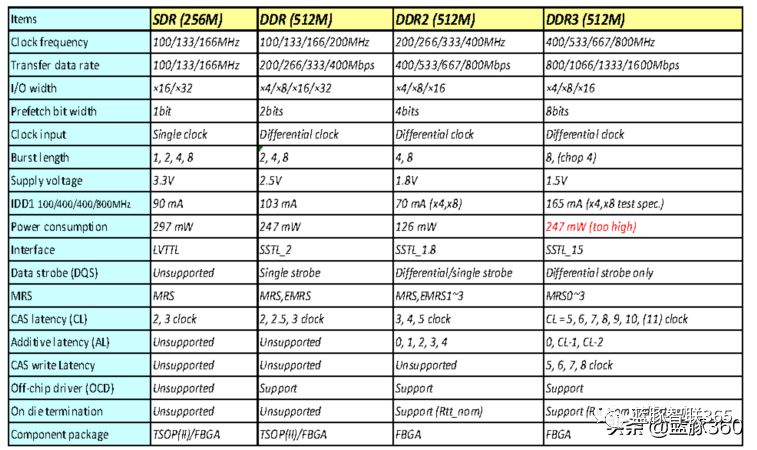

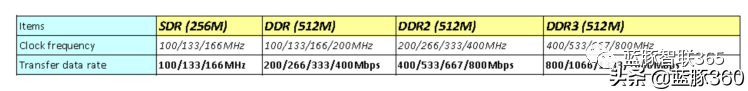

从上面的表格中,我们可以了解到,从SDRAM、DDRAM、DDR2、DDR3以及DDR3L、LPDDR3、DDR4等它们的供电电源电压是不一样的,注意设计时提前确认。

电源电压Supply Voltage不一样;

接口电平Interface不一样;

CAS Latency不一样;

封装Package不一样;

时钟速率Clock Frequency不断提高;

设计注意事项:

-

须注意Layout时各讯号与对应频率的线长要求.在消费电子产品上ADD/CMD可视为同一组,DQ/DQS为另一组,同一组信号须等长.

-

阻抗控制Impedance control,模块(DIMM)设计上一般是要求DQ阻抗60 ohm, CMD/ADDR阻抗40 ohm, 主要是PC应用上driver/receiver与stub resistor整体评估过后的组合.

-

signal与signal之间尽可能有ground或power net/trace 作shielding(可以作为current return path), signal trace与ground/power trace尽量靠近.

-

Signal trace 与 trace之间的间距尽量远.

-

Signal trace尽量避免用via, 减少换层。

-

Decoupling capacitor摆放的位置越靠近DRAM越好.

-

更重要的是impedance要一路控制在均匀的阻值.

-

Stackup上的设计, 会影响impedance控制以及讯号之间crosstalk的程度

-

Data eye window小,须注意主芯片signal driving strength 避免影响讯号 high/low pulse balance.

-

须注意VREF稳定性(spec 为VDD +/- 1%, 考虑ac noise 1%, 实际应用上VDD +/- 2%条件内存端可以涵盖)避免影响DRAM接收讯号的能力(signal setup/hold time取决于VREF+/- Vih/vil)

-

需谨慎使用频率展频功能及展频后jitter的结果,展频将严重影响DLL(延迟锁定回路)的表现造成DRAM输出讯号异常

-

预计Android模式将会大量使用省电(Power down)及休眠(self-refresh)模式使用,容易影响DLL性能表现,VDD的稳压(避免从静态到动态瞬间因电流增加产生压降)较DDR2更为重要!DD3 VDD规格为+/-5%, 此处所探讨的是瞬间大电流所导致的VDD压降幅度.

四、测试与验证

DDR5、DDR4、DDR3/DDR2/DDR SDRAM等存储器件工作在高速状态,测试重点关注的是信号完整性(SI)。关于SI的测试,请参考相关的技术文档。

DRAM,何去?何从?

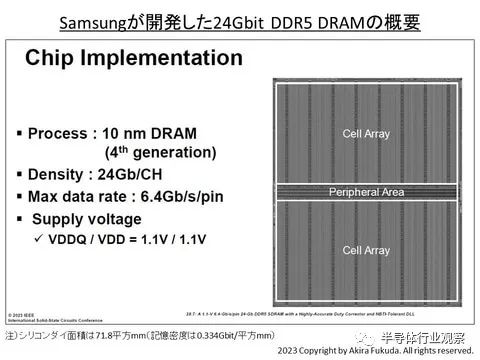

在2023年2月在国际学会ISSCC上,三星电子正是披露了公司研发的存储容量为24Gbit的DDR5 DRAM的概要(下图左)和硅芯片(下图右)。就在学会上发布的DRAM而言,该DRAM容量堪称最大。

自DRAM的生产技术世代进入10纳米代际(及20纳米代际以下)以来,已经过去五年。在这五年里,DRAM技术、产品情况皆出现了明显变化。虽然笔者一直在汇总一下DRAM的技术研发趋势,但其定位却发生了较大变化。本文中,笔者首先从2000年以来的DRAM技术开始回顾。

“

微缩化进步的牵引力不再是DRAM

业界普遍认为,在2000年之前,半导体生产技术的进步皆由DRAM的微缩化引领,甚至一度被誉为拉动工艺技术进步的“Process Driver(工艺牵引力)”。但是,进入2000年,情况却发生了变化。NAND闪存(当时的平面型存储半导体)的进步极大了带动了生产技术的微缩化发展。NAND闪存成为了微缩化加工的“牵引力主角”。

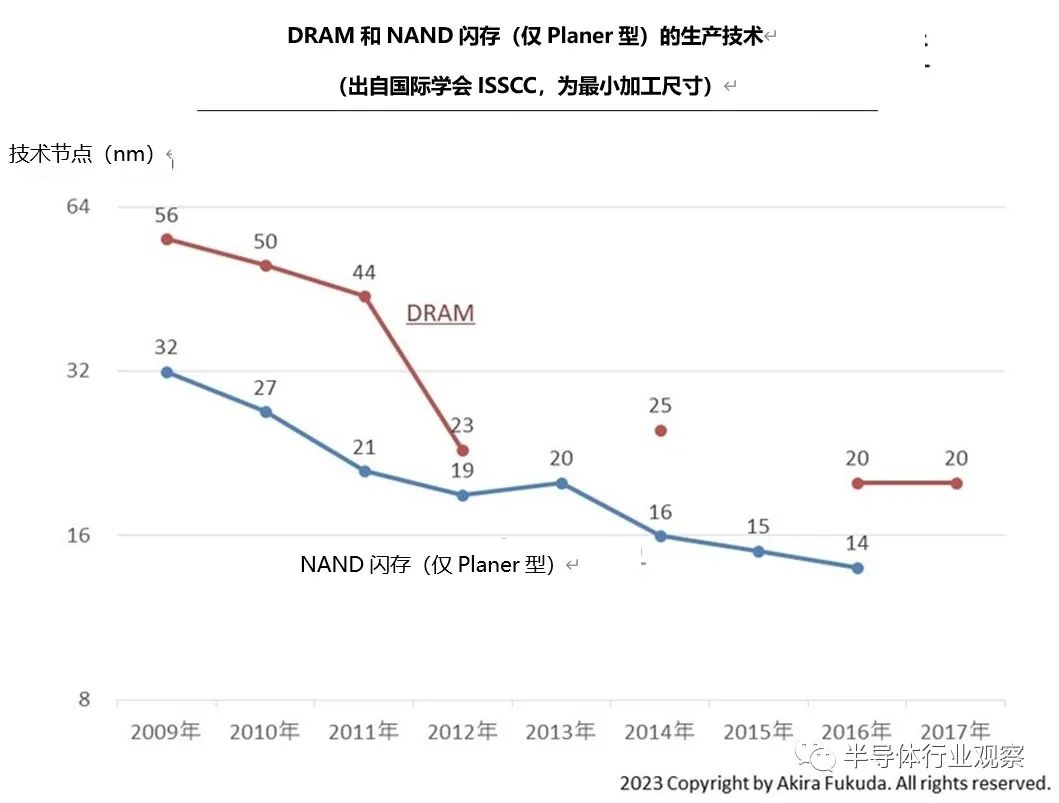

线路技术国际学会ISSCC(IEEE International Solid-State Circuits Conference,每年二月在美国旧金山举办会议)是全球半导体业界最知名单位,近期公布了其试做芯片的研发成果。2009年一2011年的技术节点(最小加工尺寸)如下,DRAM为56nm一44nm,NAND闪存(Planer型)为32nm一21nm。

DRAM和NAND闪存(仅Planer型)的技术节点(生产技术代际:2009年一2017年)。上图为笔者总结的国际学会ISSCC公布的试做芯片数据。(图片出自:pc.watch)

一度走在微缩化最前沿的NAND闪存在2015年达到极限,并放弃了加工尺寸的微缩化,改为3D堆叠。NAND闪存的微缩化几乎不再进步,2015年以后DRAM再次成为微缩化的主要驱动。

“

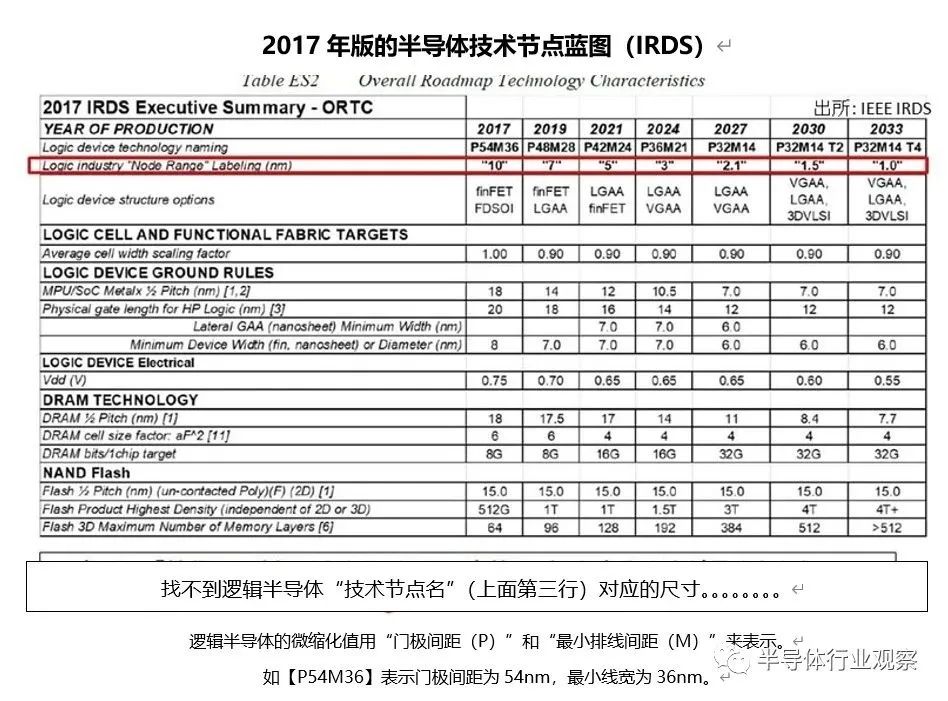

逻辑半导体的“技术节点名”与实际尺寸背离

2000年以前,主要由DRAM驱动整个半导体业界(存储半导体和逻辑半导体)的微缩化发展;但2015年一2024年DRAM却没有引领逻辑半导体微缩化发展。理由有以下两点。

其一,逻辑半导体晶体管的3D化。MOS FET结构从平面型改为3D FinFET,因此门极长度(Gate Length,或者是“沟道长度”,一直是半导体微缩化的指标)的定义将不再有意义。取而代之的是“标准单元(Standard Cell,逻辑半导体的最小单位)”的“门极间距(Gate Pitch)”和最小线宽(严密来讲,应该是二者的积)。当下最尖端逻辑半导体的“技术节点”5纳米、7纳米等数值,不过是一个标签符号,实际(硅芯片)是不存在的。

2017年版的半导体技术蓝图(IRDS)。从上至下为逻辑半导体、NAND、DRAM、NAND闪存(技术代际为笔者推测)。可以看出,找不到逻辑半导体技术节点(红框)对应的尺寸。(图片出自:pc.watch)

其二,逻辑半导体芯片·工艺技术与DRAM芯片·工艺技术的差异很大。在每一代逻辑半导体生产工艺中,晶体管的技术变化或大或小,如应变硅(Strained Silicon)、HKMG(高介电率金属门极)、FinFET、COAG(Contact Over Active Gate)等。此外,还已经研发了铜(Cu)排线、低介电率的绝缘层膜等,并全面投入应用于多层排线。

“

DRAM的技术节点反映了真实的物理尺寸

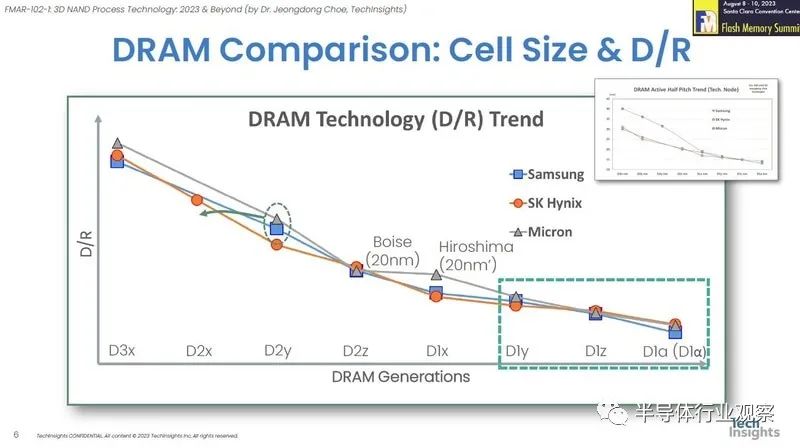

DRAM的技术节点名称与实际尺寸接近,且不同于逻辑半导体。DRAM的技术节点名称多以代码来表示,如30纳米代际为“D3z”、20纳米代际为“D2x”。

依据代码也不难推测出其技术节点,如“D2x”约为28纳米、“D2y”约为25纳米、“D2z”约为22纳米。虽然技术节点的代码依DRAM厂家不同而不同,但差异不大。

大型DRAM厂家的技术节点和设计规则(D/R)之间的关系。可以看出,大型DRAM厂家的技术节点名称和实际设计规则之间存在差异。出自TechInsights公司(一家提供半导体芯片解析服务的企业)于2023年8月在“闪存峰会”上公布的资料。(图片出自:pc.watch)

技术节点相当于尺寸的现象存在于存储单元阵列(Memory Cell Array)的“活跃区(Active Region,或有源区、主动区)”。“活跃区”排列准确,且间距(Pitch)的1/2(Half Pitch)即为技术节点名称。换句话说,“D1x”代际(18纳米代际、也被成为1Xnm)的DRAM硅芯片的单元晶体管以36nm间距排列。

从TechInsights公司于2018年12月的披露的数据来看,三家DRAM厂家的“D1x”代际(1Xnm、Half-pitch)的最小尺寸如下,三星电子为18纳米、SK海力士为17.5纳米、镁光科技为19纳米。三家差异不大。

“

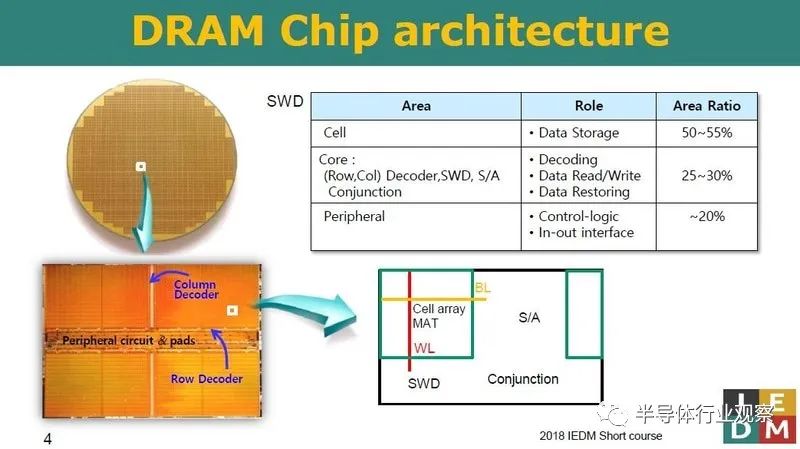

DRAM芯片的基本架构

接下来笔者将介绍DRAM芯片的基本架构(Architecture)。在DRAM的制造工艺中,厂家会尽可能多地在硅晶圆上制作DRAM芯片。从硅晶圆上切出的一颗DRAM芯片通常分为“存储单元阵列区域(通常由偶数个Sub-array构成)”和“周边线路区域(Peripheral)”

“存储单元阵列”作为DRAM的存储区域,理论上应该是2维阵列形状(Matrix)。就如同象棋棋盘或者奥赛罗(Othello)黑白棋的棋盘一样,行和列的交叉点即为“存储单元(Memory Cell)”,由“行的编号”和“列的编号”锁定存储单元的范围。此处,行的编号为“行地址(Row Address)”、列的编号为“列地址(Column Address)”。

在存储单元阵列区域,又分为“存储单元”、“核(Core)”。存储单元用于存储信号,由一个晶体管(MOSFET)和一个电容(Capacitor,即Cell Capacitor)构成。核(Core)内线路如下,从存储单元阵列中选择所需存储单元,并读取、写入数据。且配有“字线解码器(Word Line Decoder,用于选择单元晶体管的门极(字线))”、“位线解码器(Bit Line Decoder,用于选择源极(位线))”、用于放大数据读取和写入信号的“Sense Amplifier”、用于连接各部分的排线等。

周边线路(Peripheral)由控制线路和输出线路构成。控制线路主要根据外部输入的指令、地址,让DRAM内部工作。输出/输入线路负责数据的输入(写入)、输出(读取)。

上图为DRAM的基本架构说明图。左上角为硅晶圆照片(推测实际直径尺寸为300mm)。左下角为DRAM的硅芯片照片。硅芯片中心左右两侧有周边线路、输出/输入Pad点、行解码器(Row Decoder),中央的上下部分有列解码器(Column Decoder)。上图右下角是存储单元阵列(Sub-array)的基本结构。红色字线(WL)和黄色位线(WL)的交叉点上有一个存储单元。字线的端部配与副字线驱动(SWD)相连、位线的端部与读出放大器(Sense Amplifier,简称为“SA”)相连。上图右上角为各部分占硅芯片的比例。存储单元占50一55%,核(解码器、驱动器、读出放大器、相互连接部分)占25一30%,周边线路(Peripheral,控制线路和输出线路)占20%左右。在2018年的国际学会IEDM的技术讲座上,三星电子公布了其相关资料,上图出自其资料。(图片出自:pc.watch)

“

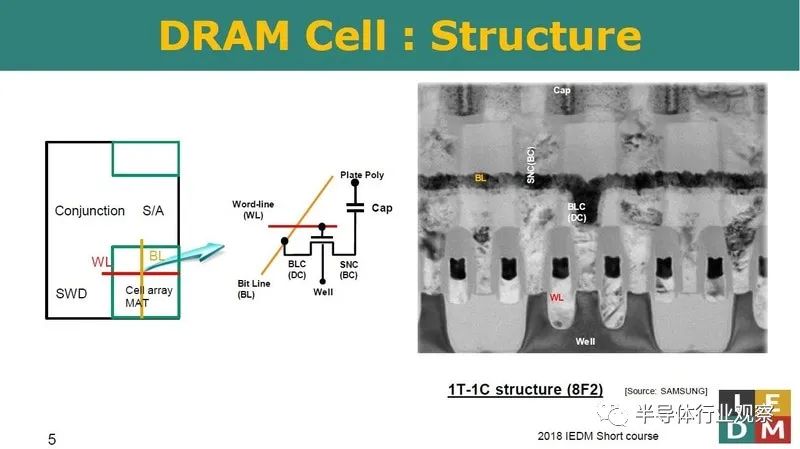

通过将电荷储存于电容,存储理论值

DRAM的存储单元由一个晶体管(简称为:“T”)和一个电容(简称为:“C”)构成。在存储半导体行业,普遍称之为“1T1C”。晶体管具有选择开关的作用,因此也被称为“选择晶体管”。读取/写入动作时,字线解码器和位线解码器选择的位线和字线的交叉点的“选择晶体管”成为“ON”状态。

存储单元的电容(在性能上与作为电子零部件的电容类似)主要存储电荷信号,也被称为“单元电容”。当电容存储一定容量的电荷后,存储单元的理论值为“高(或者1)”。相反,当存储的电荷不满时,存储单元的理论值为“低(或者0)”。

DRAM存储单元的线路事例(左图)、电子显微镜下观测到的存储单元断面图(右图)。左侧线路图下,选择晶体管(通常为n渠道MOSFET)的门极为字线(红色:WL)、源极为位线(黄色:WL)。选择晶体管的漏极(Drain)经由单元电容与平板(Plate)电极相连。在右侧的断面图中,红色部分(WL)为选择晶体管的门极(字线)、BLC为位线连接、SNC为存储节点连接(Storage Node Connect)。SNC上方与电容(照片中的Cap部分)相连。SNC文字左侧的黄色字“BL”为“位线”。(图片出自:pc.watch)

“

DRAM存储单元的基本动作和Refresh

在将数据写入DRAM时,利用解码器将指定位置的选择晶体管改为“ON状态”,同时,将读取的数据暂存于输入缓存区(Buffer),然后,利用读取放大器将数据转为电流、为单元电容充电。

充电后,随着电容的不断放电以及时间的流逝,写入的数据(电荷)会逐步消失。因此需要定期写入数据的动作。该动作被称为“Refresh”。2000年以前的DRAM而言,采用的是一个外接的存储控制器在适当的时间点实施“Refresh”。最近,大部分产品采用的是在产品内部实施“Refresh”。

读取数据时,把选择晶体管改为“ON”状态,单元电容的电荷以电流的形式流向“位线”。位线的电流利用读取放大器(S/A)以电压的形式增压,电压信号经由输出缓存区向外输出。

在读取工作中,需要注意的是单元电容的电荷可能会因为读取工作而丢失。读取放大器可以及时修复读取的数据(即重新写入)。

“

2000年后,DRAM存储容量增长不明显

2000年以前,尤其是上世纪70年代和80年代DRAM的存储容量增长极其明显。存储半导体行业曾有“三年四倍”的说法,即存储容量扩大了四倍的新一代DRAM会在三年后量产。主流用户虽然从20世纪70年代的Main-flame变成了80年代的Workstation和90年代的PC,但DRAM厂家并没有辜负“三年四倍”的惯例。

从国际学会ISSCC(每年二月份召开)上公布的硅芯片的概要来看DRAM的研发情况,如下,最初为最大存储容量,20世纪90年代初期,容量进步速度远超“三年四倍(甚至为1年1.59倍)”。1990年为16Mbit,在1995年为1Gbit,即“五年64倍(1年2.3倍)”。

然而,1995年以后,存储容量的增长就不再明显。1999年之前,一直保持着1Gbit的最大容量。后来,又徘徊于256Mbit和512Mbit、1Gbit、2Gbit、4Gbit。但却迟迟没有进入新一代的4Gbit。2014年和2016年公布了8Gbit的硅芯片,可以说终于从1Gbit进步了1.5个代际。其实,进步速度为“20年8倍”(1年1.11倍),可以说是DRAM研发历史上容量进步最慢的一次。

DRAM最大存储容量(单个硅芯片)(1990年一2014年)。此图为笔者汇总自国际学会ISSCC披露的数据。可以看出,1996年~2012年期间,容量进步不明显(年度扩大率为1.11倍)。(图片出自:pc.watch)

“

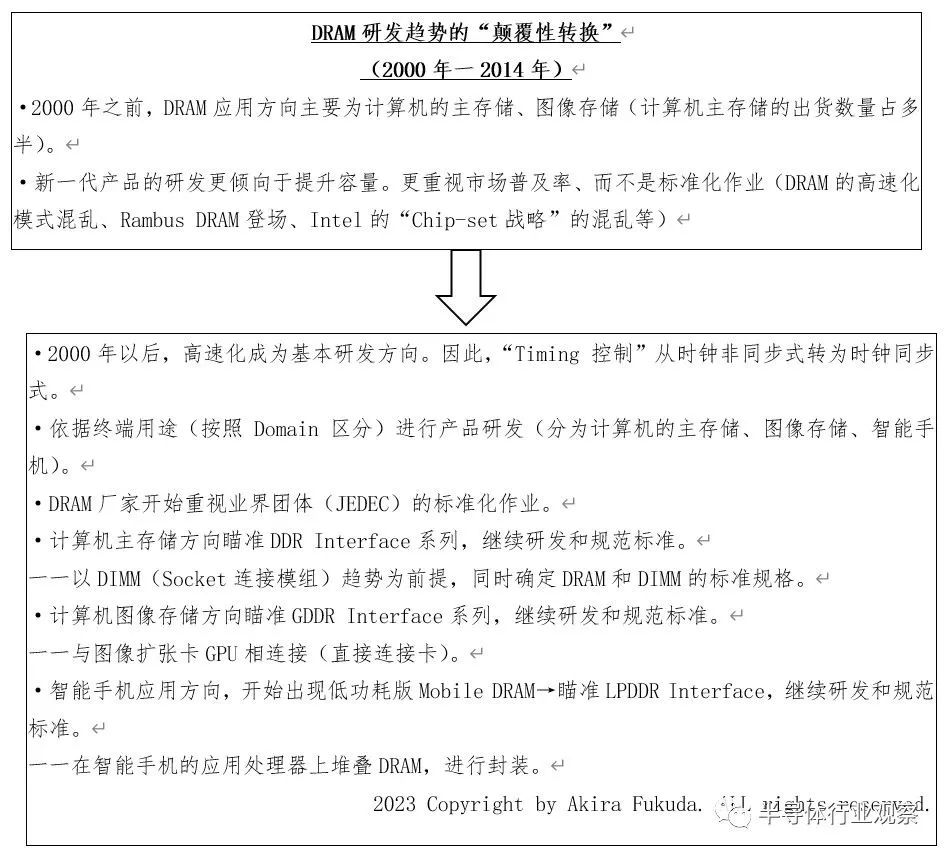

DRAM研发的“颠覆性转换”

1995年~2014年期间的20年中,DRAM研发又发生了什么呢?粗略来讲,研发方向发生了很大变化。甚至可以说是“颠覆性转换(Paradigm Shift)”,即DRAM的研发方不再是扩大容量,而是提升速度。

DRAM数据传输速度(单个输入/输出Pin)的推移表(2000年一2012年)。笔者汇总自国际学会ISSCC披露的数据。上述三个系列的年度容量扩大速度均超多1.11倍。(图片出自:pc.watch)

为了提升存储速度,采用“时钟(Clock)同步”的方式控制动作时间。最初,为了与传统的DRAM(Clock-less式非同步DRAM)区分,称之为“SDRAM(S:Synchronous)”。如今,大家看到“DRAM”一般就默认为“同步式”(或者不去刻意区分同步还是非同步)。严格来讲,DRAM(如DDR、LPDDR、GDDR等)应该被记为“SDRAM”,因此在企业的产品目录、学会论文中一般会记录为“SDRAM”。

可以看出,SDRAM的新一代标准式样是有意强调其速度之快而做成的。最初的SDRAM是以时钟速度输入/输出速度的。此时的时钟频率为133MHz。新一代SDRAM可以以两倍时钟速度输入/输出数据,即“DDR(Double Data Rate) SDRAM”。时钟频率高达200MHz,数据的输入/输出速度是时钟的两倍,即400MT/s的输入/输出Pin(此处T=Transfer,即传输次数,即一次传输接收/发送1bit,bit/秒)。

近年来,每一代DDR系列SDRAM的数据输入/输出速度都较前一代提升两倍。在国际学会ISSCC上公布的DDR系列SDRAM的数据传输速度如下,自2003年至2012年,9年内提升到4.4倍,即1.18倍/年。

Graphics DRAM(显存)也采用DDR,并积极提升传输速度,即G(Graphics)DDR、SGRAM(Synchronous Graphics RAM)。GDDR系列的SGRAM的传输速度正不断攀升。国际学会ISSCC上披露的GDDR系列SGRAM的数据传输速度如下,2004年至2010年期间的六年内,增长至4.4倍,即1.28倍/年。

随着智能手机的普及,开始研发低功耗版的SDRAM。最初被称为“Mobile DRAM”,后来基于“LP(Low Power)DDR SDRAM”的名称研发逐步步入正轨。2009年国际学会ISSCC上首次披露LPDDR系列的试做版硅芯片。当时的Hynix 半导体公司研发的1Gbit芯片的数据传输速度为1.066Gbps/pin。即在2012年之前,LPDDR系列的数据传输速度提升至1.5倍(1.14倍/年)。

DRAM研发方向出现“颠覆性转变”(2000年一2014年)。1995年一2004年(或至2014年)期间的10年(或20年)内,发生了诸多变化。(图片出自:pc.watch)

2000年以后的DRAM研发战略方向主要如下,高速化(通过导入时钟同步式的设计)、依据产品应用方向进行研发、依据应用方向确定封装(Packing 或Module)标准。NAND闪存是大容量的“主角”。2005年,在ISSCC上披露了NAND闪存存储密度超过DRAM的信息。可以说,如今已经步入了“NAND闪存容量大、DRAM速度高”的时代。

1. 引言

这几年主要做的都是视频+神经网络的工作,中间处理的数据量都是很大的。有时候涉及到多路多目的情况,就很容易出现带宽问题。

偏偏这个问题还很难查,之前上家是用的xilinix的方案,还是AMP的模式,一个裸核+一个linux,还有FPGA同步抢带宽,很多时候只能从函数耗时来进行分析,根本无法对带宽问题进行一个定量的计算。感觉很多都是靠直觉和经验,比如上个项目是4目的,用的MpSoc5,有ABCD功能,能稳定跑。这次项目也是4目,多加了一个EF功能,就不好说了。而且出了带宽问题是真的很难查,也找不到什么有效的工具来查,系统会出现各种神奇的bug,从逻辑角度完全无法分析和解释的,只能不停的通过做实验来测试。

这应该是之前项目最大的痛点了。功能都好做。但是老板为了省成本,玩命往便宜片子里加功能,比如7020跑多个神经网络,做CNN,TSR,seg都要做,arm这边也一堆功能,然后出了诡异问题就是嵌入式你们好好查。偏偏拿不出什么有效的数据来说服老板。全靠经验。“A公司也用的这个芯片,他们只能跑BCD功能,我们再加EFG确实压力太大了。”诸如此类,比较无力。这时候就看leader的抗压能力了,抗不住整个组就要坑。

最近在安霸见到一个新的小工具 DramStatictiscTools,十分简单,但是十分好用。我看SDK是2020.6月加入进来的,但是实际上整个CV2X的芯片都支持的,估计很早之前就进行相关的计划了。这可能就是自己做芯片和用别人芯片的不同吧。

CV2x芯片在内部加入了内存统计的功能,这个不再是上层软件层面的统计了,是芯片内Dram Controller的统计,这个东西我不知道对于芯片来说难不难做,但是对于视频芯片这种高带宽的应用,真的很实用。

芯片可以自己做一个在一段时间内,进行每一个Dram client的统计,包含request,burst,maskburst三项的统计。因为这个是Dram Controller底层的统计,可以说是最为精准的了。client包括 AXI,DMA,ENET,USB等一堆客户端。我们可以准确的拿到多少次请求,进行了多少次burst,其中有多少是maskburst。

2. Dram基础知识

这部分基础是新学的,不然这个统计表看不懂,连什么是burst都不知道。

2.1 Dram结构

抄了一张图(From 底部链接1).

从图中可以明显的看出,我们日常使用的内存条,其实是由一个个内存片组成的(图中的黑色方块)。

一个黑色方块是256M,8个组在一起就成2G。

黑色方块内部分为多个bank。

每个bank中间有r行c列个存储单元。

每个存储单元中间有n个电容和晶体管组合。

每组电容和晶体管结构如下,代表1位(1 bit)。

每个存储单元里有n组,即为n bit,它通常是8bit或者16bit。

其实内存个人类比理解就像表格,想像一下excel

内存 excel

8个bank 8个sheet

16384行 16384行

1024列 1024列

1个存储单元(cell) 1个格子

其中,1个存储单元就是一次内存读写的最小单位。

但是1个存储单元并不是只有一个电容和晶体管(1bit),它通常是8bit或者16bit,也就是,行列地址确定之后,可以读取8bit或者16bit(1个cell的数据)

2.2 一些基础名词理解

bank

burst

maskburst

prefetch

2.3 关键名词的理解

2.3.1 prefetch

因为统计表中有burst的数量,之前就很奇怪,为什么同样的case,比如拷贝1M的buffer,相同位数的DDR4和LPDDR4统计的数值不一样?为什么burst数量还和内存类型有关系?

认真查了一下,原来 一次burst是读一个存储单元,但是存储单元的位宽并不是芯片的位宽,而是芯片的位宽*prefetch的位数,所以每次burst的数据量还和prefetch的位数有关。

DDR1 采用2n prefetch,DDR2采用4n prefetch,DDR3、DDR4采用8n prefetch,LPDDR4是16n。

prefetch的作用是,在无法提升核心频率的情况下,通过prefetch同一时间读取多个内存单元,通过加线的方式并行传到IO换缓冲区,然后从缓冲区到Dram控制器的线数降下来,提高频率。

在核心颗粒的主频提升遇到瓶颈的情况下,这一技术成为了DDR更新换代的主流技术。

Prefetch简单的说就是在一个内核时钟周期同时寻址多个存储单元并将这些数据以并行的方式统一传输到IO Buffer中

2.3.2 burst

参考连接

DRAM 内存介绍

DDR扫盲——关于Prefetch与Burst的深入讨论

DDR1-3和GDDR1-5全解析

关于DDR的prefetch

DDR3和DDR4内存的区别是什么

一堆名字的解释

————————————————

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/tao475824827/article/details/109156185

DRAM的那些事儿

读完这篇文章,你可以回答什么?

-

DRAM的分类是怎么样的?

-

DRAM的组织架构是什么样子的?

-

DRAM的封装工艺有什么?

-

DRAM的插槽module有什么?

DRAM的分类

•DRAM (Dynamic random access memory) : 即动态随机存储器最为常见的系统内存,是很快要淘汰的产品。DRAM 只能将数据保持很短的时间。为了保持数据,DRAM 使用电容存储,所以 必须隔一段时间刷新(refresh)一 次,如果存储单元没有被刷新,存储的信息就会丢失。

•SDRAM (Synchronous DRAM) : 同步动态随机存取存储器,同步是指 Memory 工作需要步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不 丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。主要应用于PC外的产品上。

•DDR SDRAM (Double Data Rate SDRAM) :主要应用在PC上。SDRAM 从发展到现在已经经历了四代,分别是:

ØSDR SDRAM(Single Data Rate SDRAM)

ØDDR SDRAM(Double Data Rate SDRAM)

ØDDR2 SDRAM

ØDDR3 SDRAM

第一代与第二代 SDRAM 均采用单端(Single-Ended)时钟信号,第三代与第四代由于工作频率比较快,所以采用可降低干扰的差分时钟信号作为同步时钟。SDR SDRAM 的时钟频率就是数据存储的频率,第一代内存用时钟频率命名,如pc100,pc133 则表明时钟信号为 100 或 133MHz,数据读写速率也为 100 或 133MHz。

之后的第二,三,四代 DDR(Double Data Rate)内存则采用数据读写速率作为命名标准,并且在前面加上表示其 DDR 代数的符号,PC- 即 DDR,PC2=DDR2,PC3=DDR3。如PC2700 是 DDR333,其工作频率是333/2=166MHz,2700 表示带宽为 2.7G。

DDR 的读写频率从 DDR200 到 DDR400,DDR2从 DDR2-400 到 DDR2-800,DDR3 从 DDR3-800 到DDR3-1666。

很多人将 SDRAM 错误的理解为第一代也就是 SDR SDRAM,并且作为名词解释,皆属误导。SDR 不等于 SDRAM。

•RDRAM (Rambus DRAM) : 主要应用在PC上 ,比DDR 用得少。其内存规范是Intel与Rambus共同定制,旨在创造市面上最高速的内存产品。其内部RISC架构、高频率和高带宽的优势一度被认为是内存市场的新宠儿,Intel也对自己的Rambus DRAM充满信心,并寄希望于Rambus DRAM配合Pentium 4处理器,建立属于自己的王朝。但是Rambus最终并没有得到市场的认可,究其原因,就是因为Rambus内存高昂的售价以及“巨大”的发热量。加上Rambus DRAM必须安装两条才能够使用,这就大大提高了这种内存的使用门槛。最终,Rambus DRAM没有经受住市场的考验,被价格更低的DDR SDRAM踩在了脚下。

•LPDDR SDRAM (Low Power DDR SDRAM) : 具有功率小、体积小等特点。包括:

ØLPDDR SDRAM

ØLPDDR2 SDRAM

ØLPDDR3 SDRAM

ØLPDDR4 SDRAM

ØLPDDR5 SDRAM

ØLPDDR6 SDRAM

•GDDR SDRAM (Graphics DDR SDRAM) : 具有时钟频率高,热量少等特点。

ØGDDR :在市场上已经被淘汰了

ØGDDR2:多用于低端显卡产品,并采用BGA封装

ØGDDR3:低功耗,高频率和大单容量,BGA封装技术

ØGDDR4 :时序过长,相同频率的GDDR3显存性能优于使用GDDR4显存的产品

ØGDDR5:更高的带宽,更低的功耗,更高的性能

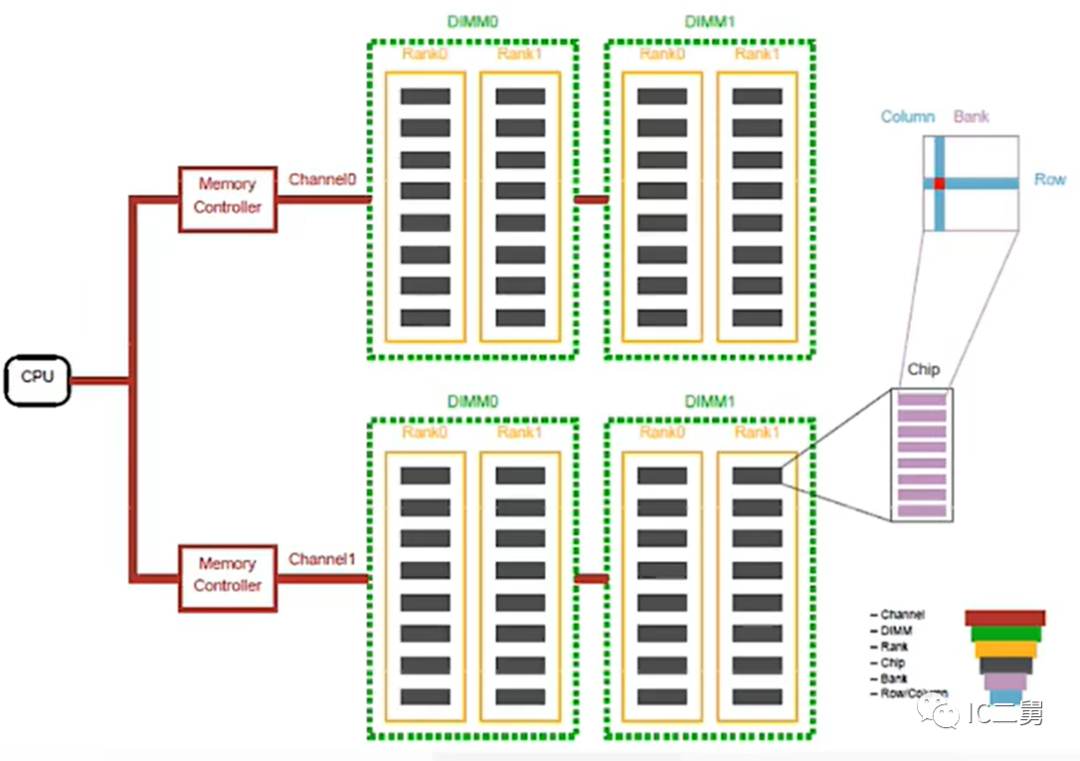

DRAM的组织架构

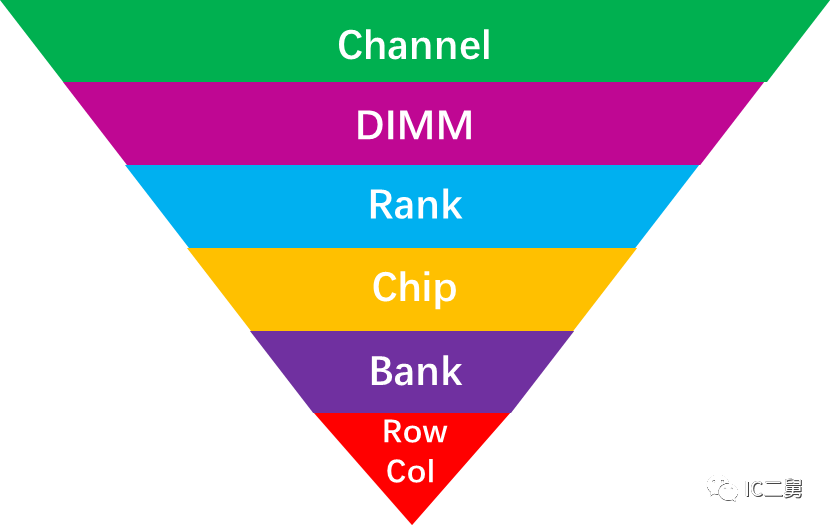

DRAM的等级分的比较清楚,从上到小分别是Channel-DIMM-Rank-Chip-(Die)-Bank group-Bank-Row/Column-Nbit memory cell,详细如下所示:

进一步简化如下:

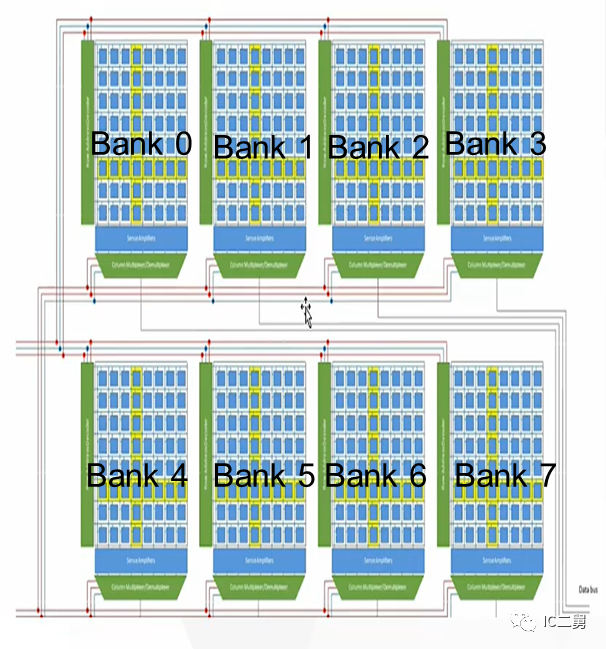

这种多通道结构可以提高DRAM的数据传输速率和带宽。例如Channel1部分,存储器控制器可以同时控制两个DIMM;一个DIMM有两个Rank,两个Rank的电连接方式不同。通过特定的地址总线可以选择一个Rank。对于Rank,一个Rank有多个Chip,这些Chip共享相同的信号来同时操作。下图是一个Chip上的Bank。

一个Bank表示一个内存数组。同一Chip中的多个Bank可以并行访问,也可以独立访问。多个Bank的读操作是独立进行的,但多个Bank共享I/O门控、刷新命令。下边这个图是细分到字线和位线所连接的各个Cell。

DRAM存储芯片的电路结构:

DRAM的封装工艺

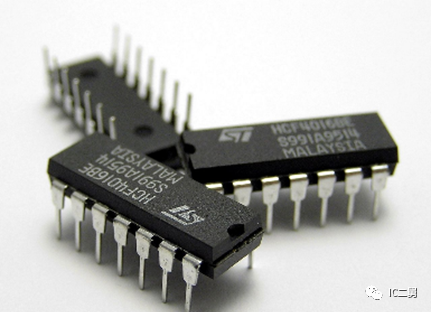

在整个发展的过程中,其封装工艺有很多,今天主要分享的是重要的四个节点,分别是:DIP(Dua Inline Package)、TSOP(Thin Small Outline Package)、BGA(Ball Grid Array)以及CSP(Chip Scale Package)。

DIP

(Dua Inline Package)

优点:易于更换、适用于PCB焊接以及便宜的价格

缺点:大尺寸、高频串扰以及高功率

应用:SDR SDRAM

TSOP

(Thin Small Outline Package)

优点:引脚尺寸小、低成本以及高可靠性

缺点:低速、焊接有限制

应用:DDR1 SDRAM

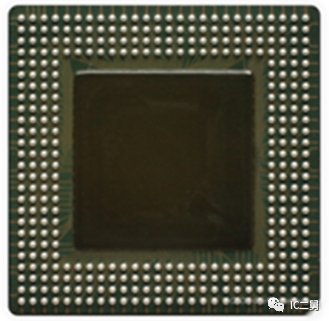

BGA

(Ball Grid Array)

优点:销钉厚度小、高容量以及更好的散热

应用:DDR2-3/LPDDR1-5 SDRAM、GDDR2-6 SDRAM

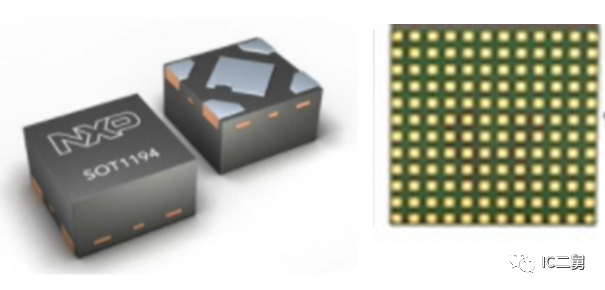

CSP

(Chip Scale Package)

优点:芯片面积利用率高、速度快以及抗干扰性好

缺点:复杂,成本大

应用:DDR4-5 SDRAM

DRAM的Module类型

DRAM的Module类型大概有两种:SIMM (Single in-line memory module)、DIMM (Dual in-line memory module)。二者的主要区别在于SIMM是单面的,而DIMM是双面的。

Reference

https://www.eefocus.com/article/417661.html

https://mb.zol.com.cn/344/3443858.html

https://product.pconline.com.cn/itbk/diy/graphics/1112/2628133.html

https://www.bilibili.com/video/BV14b4y1o7dw/?spm_id_from=333.999.0.0&vd_source=31517a1b641989be28521f673b04ee38

https://www.bilibili.com/video/BV1Y14y1f7bP/?spm_id_from=333.337.search-card.all.click&vd_source=31517a1b641989be28521f673b04ee38

https://www.docin.com/p-693400959.html

685

685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?