硬件课设选择了基于Nexys 4开发板的小车课题,也是想以此来锻炼自己并积攒一些有关于FPGA Verilog HDL方面的知识和经验。算是自己接触的第一个硬件工程吧,最终结果出来后自己还是很满意的,毕竟凝结了自己几周的心血。

好啦,话不多少,赶紧上代码上图,算是做一个记录点,自己以后回来翻到时会是怎样的感受呢。

(在设计过程中也参考了网络上许多大神的设计思想,在此致谢!)

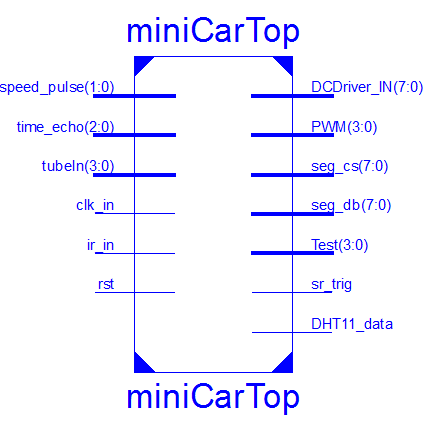

顶层模块设计与原件清单

顶层文件是在综合了各个子模块后综合得到的控制文件,顶层模块的设计切合了模块化设计思想,方便代码的更新升级,增加了可读性。首先让我们来看一下顶层模块的RTL视图。

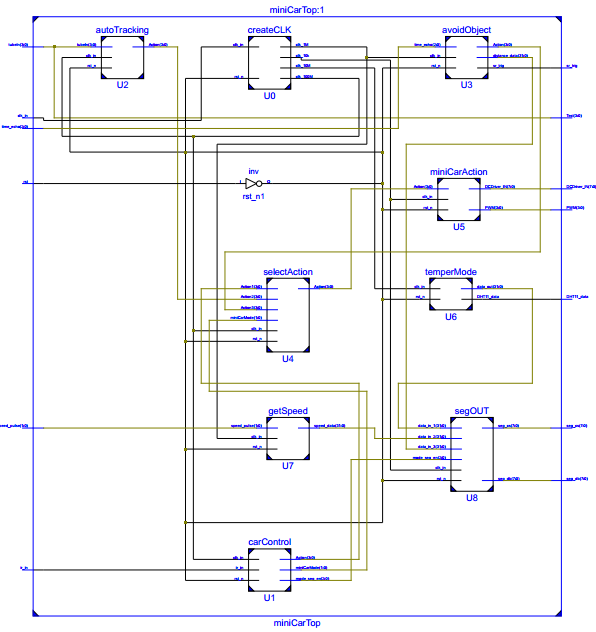

嗯,这是总体的,再看一个细化后的顶层模块。

由以上可以看出顶层模块内部的构成了,其主要由时钟产生模块U0(createCLK),红外遥控U1(carControl),自动循迹U2(autoTracking),避障测距U3(avoidObject),行为选择U4(selectAction),电机驱动U5(miniCarAction),温湿度测量U6(temperMode),速度测量U7(getSpeed),数码管显示U8(segOut)一共9个模块构成。

好,介绍完总结框架后,我们来看下顶层v文件的代码部分吧,说一下,我们设计中各个模块复位低有效,而顶层模块复位高有效,故对其进行了一个取反后来连接各个模块,参考时需要注意哦。

//

// Institutions: HUST-EI-TX1105

// Designers: Tong.Liu & Weitong.Liang

//

// Create Date: 24/06/2014

// Project Name: miniCar

// Module Name: miniCarTop

// Target Devices: NEXYS 4

// Tool versions: ISE 14.6

// Description: This is a top file of all mode.

//

module miniCarTop (

clk_in,

rst,

ir_in,

time_echo,

tubeIn,

DHT11_data,

speed_pulse,

sr_trig,

DCDriver_IN,

PWM,

ring_signal,

seg_cs,

seg_db,

Test

);

input clk_in; // global input clock

input rst; // global reset signal

input[3:0] tubeIn; <span style="white-space:pre"> </span>// Four tube signal for autoTracking

input ir_in; // HongWai control input signal(PPM)

input[2:0] time_echo; // Two echo signal from ultrasonic sensor

inout DHT11_data; // Inout signal for DHT-11 sensor

input[1:0] speed_pulse; // Two Speed pulse form speed sensor

output sr_trig; // Output trig signal for ultrasonic sensor

output[7:0] DCDriver_IN; // Output signal for L298N power mode IN1 ~ IN7

output[3:0] PWM; // Output signal for L298N power mode ENA ~ END

output ring_signal; <span style="white-space:pre"> </span>// Output signal for alarm / red led

output[7:0] seg_cs; // Output cs signal for 4-7 digital seg

output[7:0] seg_db; // Output db signal for 4-7 digital seg

wire rst_n;

assign rst_n = ~rst; // rst_n low effective

wire[3:0] Action; // miniCar Action for mode miniCarAction

wire[3:0] Action1; // miniCar Action for mode carConteol

wire[3:0] Action2; // miniCar Action for mode autoTracking

wire[3:0] Action3; // miniCar Action for mode avoidObject

// create the clock signal that all mode need

wire clk_100M;

wire clk_10M;

wire clk_1M;

wire clk_10k;

createCLK U0 (

.clk_in(clk_in),

.rst_n(rst_n),

.clk_100M(clk_100M),

.clk_10M(clk_10M),

.clk_1M(clk_1M),

.clk_10k(clk_10k)

);

// Use & Link all modes

wire[1:0] miniCarMode;

wire[2:0] mode_seg_en;

carControl U1 (

.clk_in(clk_100M),

.rst_n(rst_n),

.ir_in(ir_in),

.miniCarMode(miniCarMode),

.mode_seg_en(mode_seg_en),

.Action(Action1)

);

autoTracking U2 (

.clk_in(clk_100M),

.rst_n(rst_n),

.tubeIn(tubeIn),

.Action(Action2)

);

wire[31:0] distance_data;

avoidObject U3 (

.clk_in(clk_1M),

.rst_n(rst_n),

.time_echo(time_echo),

.sr_trig(sr_trig),

.distance_data(distance_data),

.Action(Action3)

);

selectAction U4 (

.clk_in(clk_100M),

.rst_n(rst_n),

.miniCarMode(miniCarMode),

.Action1(Action1),

.Action2(Action2),

.Action3(Action3),

.Action(Action)

);

miniCarAction U5 (

.clk_in(clk_10k),

.rst_n(rst_n),

.Action(Action),

.DCDriver_IN(DCDriver_IN),

.PWM(PWM)

);

wire[31:0] temper_data;

temperMode U6 (

.clk_in(clk_10M),

.rst_n(rst_n),

.DHT11_data(DHT11_data),

.data_out(temper_data),

.ring_signal_temper(ring_signal)

);

wire[31:0] speed_data;

getSpeed U7 (

.clk_in(clk_1M),

.rst_n(rst_n),

.speed_pulse(speed_pulse),

.speed_data(speed_data)

);

segOUT U8 (

.clk_in(clk_10k),

.rst_n(rst_n),

.mode_seg_en(mode_seg_en),

.data_in_1

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2031

2031

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?