本人windows10在vivado 2015.03下,编译综合都通过,在modelsim与vivado关联绝对成功的前提下,点击run simulation 一直处在这个状态,一直执行中,无法正常调用出来,终于查出问题原因。原因是我包含了一个不相关的文件`include "lcd_para.v",我的程序不需要这个文件了,当时忘记删掉了,所以现在删掉后就可以成功调用仿真了。

仍然在关联绝对成功的前提下,又出现了上述的问题

这一次TCL console中一直显示# Modifying D:\modeltech64_10.1c\xilinx_lib\modelsim.ini

# Modifying D:\modeltech64_10.1c\xilinx_lib\modelsim.ini然后就调不出来了,我以为是与xilinx有什么冲突,就去鼓捣xilinx软件了,结果不是那么回事,还把以前可以仿真的ram搞坏了,也是上述问题,就不报错,用vivado自带仿真器仿真通过,但是却调不出来,最后方法是

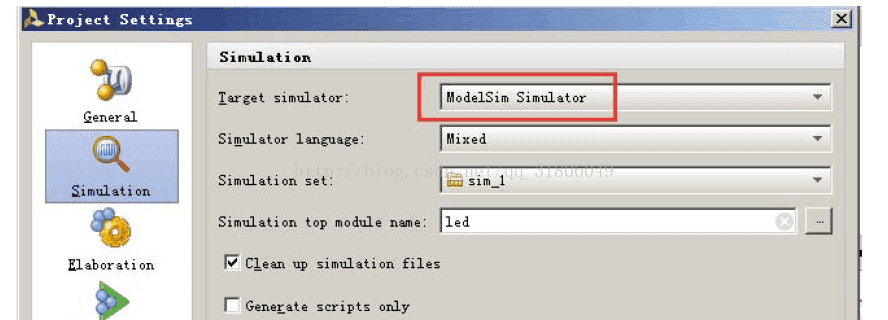

clean up simulation files前面没打勾,赶紧打钩后解决问题了。

1029

1029

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?