前段时间做了很多前期的工作,终于成功在板子上运行了自己的第一个FPGA工程,用一个10位的变量控制板载10位小灯按照二进制每次加一闪亮。周期是1S。

下面将步骤以及遇到的问题贴出来给同样初学FPGA的同学一点参考。

1,新建一个工程,名称叫做conuter_leds,选择存储路径,一班路径不要带空格,不要带中文字符,我的在C盘,选择相应的器件,其他默认设置就可以。

2,新建一个Verilog HDL file,conuter.v文件,注意文件名不能与工程名称一致,因为如果这个文件只是工程的一部分,如果这个文件与工程名一致的话编译的时候就会认为整个工程是以这个文件为中心的,会出错。键入以下代码:

module counter(clock,out);

input clock;

output [9:0]out;

reg [9:0]out;

integer i;

always@(posedge clock)

begin

if(i==50_000_000)

begin

out<=out+1;

i <=0;

end

else

begin

i <= i+1;

end

end

endmodule3,把上一步编写的VerilogHDL代码变成BSF文件,这就相当于封装成一个函数啦。点击File/Create/Update/Create Symbols from Current File,这样就把刚才编辑的文件创建了一个counter.bsf文件备用啦,存储路径就在工程根目录。

4,新建一个BDF文件File/New/Block Diagram/Schematic File,在这个文件空白处右键Insert/Symbol...,在Liberty框里找到project,选中counter,这就是咱们刚才生成的BSF文件啦,拖放到合适位置,然后再建立一个PLL核。

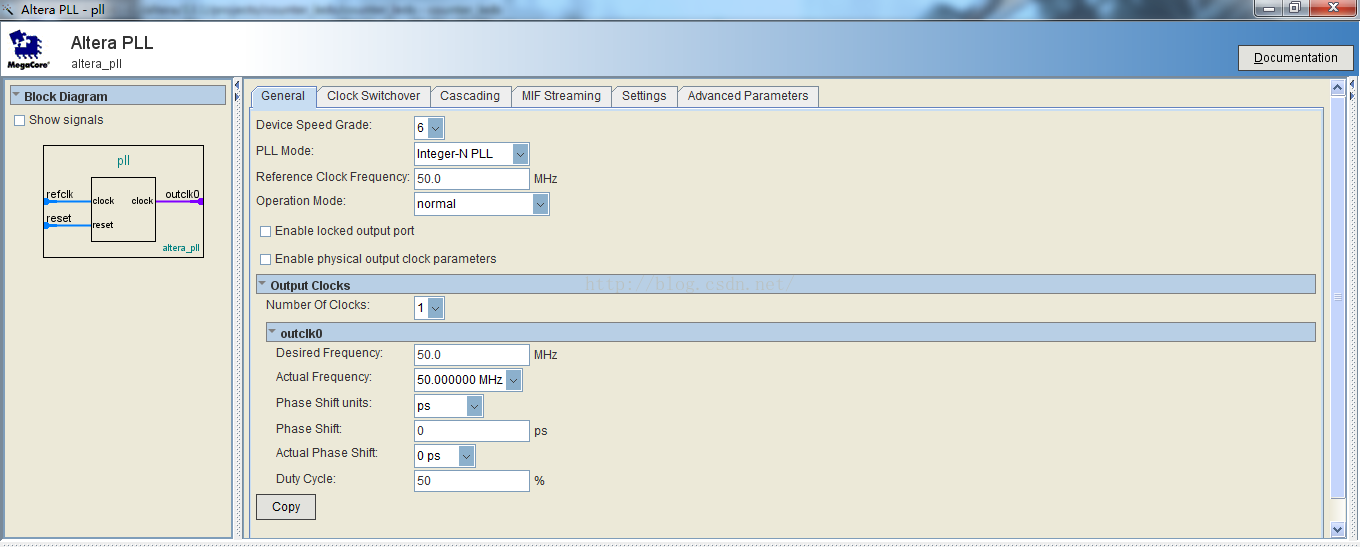

5,建立PLL核:空白处右键Insert/Symbol...,点击左下角的MegaWizard Plog-in Manager,点击Next,在搜索框搜索PLL,选择Altera PLL V13.1,选择右边输出文件类型(VerilogHDL),在路径后面键入名字pll.v(注意也不可以和工程名称一致),PLL核的设置如图:

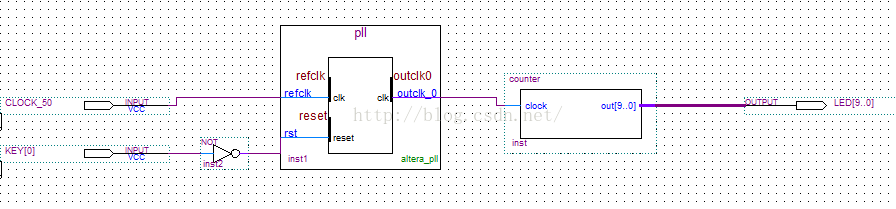

6,插入部件,包括输入输出端口和一个非门。方法右键/insert/Symbol../在窗口里面找到primitives/pin,分别放置input和output,非门在logic里面。

最后效果如图:

7,输入和输出引脚改名以及连线:改名直接在引脚上右键proprties就可以了。连线也很简单。

8,BDF文件保存,命名为counter_leds。这时候必须和工程名一致,因为这就是整个工程。

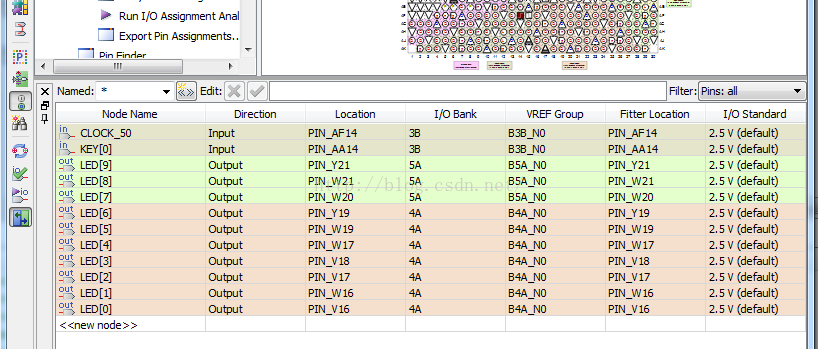

9,引脚匹配:Processing > Start > Start Analysis & Elaboration ,成功以后点击Assignments > PinPlanner,按照下图或者参照板子的用户手册进行引脚匹配(在Location一栏双击选择对应的引脚)

10,点击工具栏的箭头或者Processing/Starrt Complication进行全编译,完成以后就可以下载进板子啦,下载步骤请参见上一个博客。

效果:10个LED灯按照二进制加一依次点亮,频率1S。

【操作系统】Win8/64bit

【开发环境】Quartus ii13.1 Web edition

【开发板】DE1-SOC

【芯片】Cyclone V/5CSEMA5F31C6

【我是一辆59】

6900

6900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?