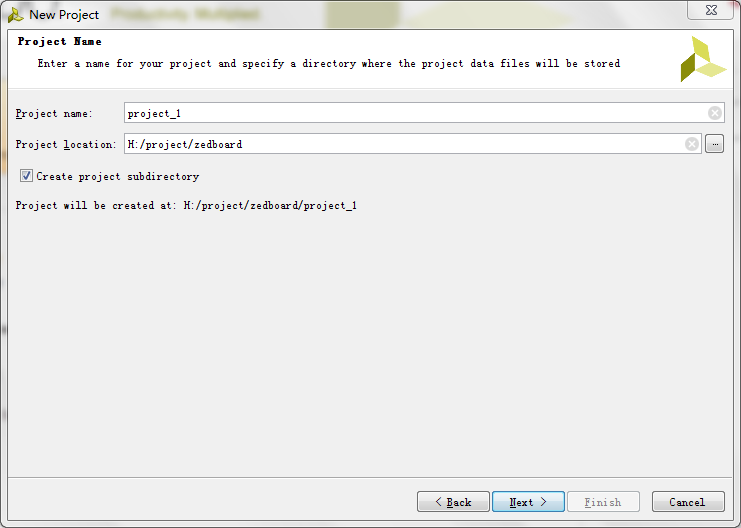

打开vivado,点击create New Project,

下边的建立子目录工程一定要勾选。点击下一步:

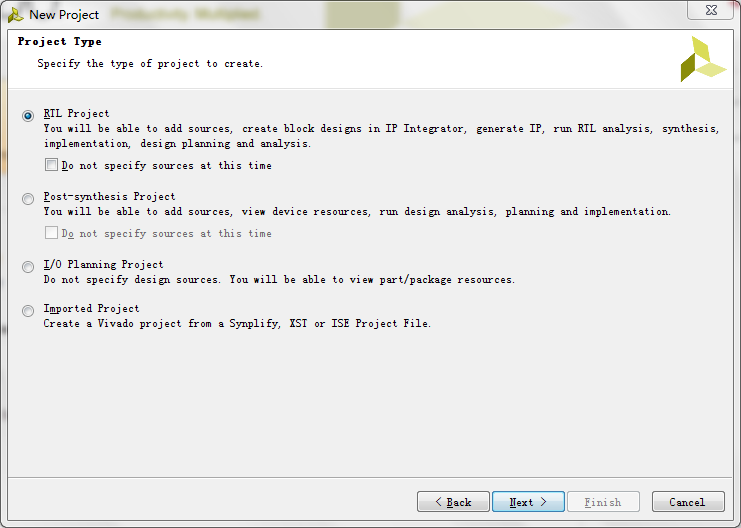

选择第一个,下方可选项不要勾选。点击下一步:

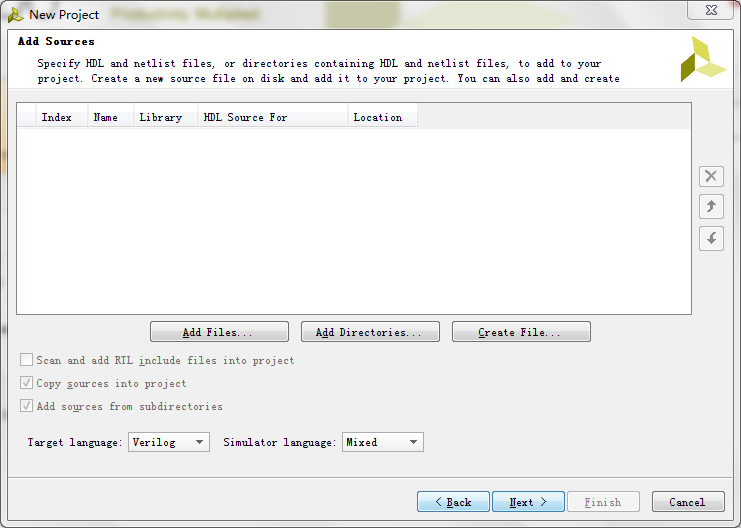

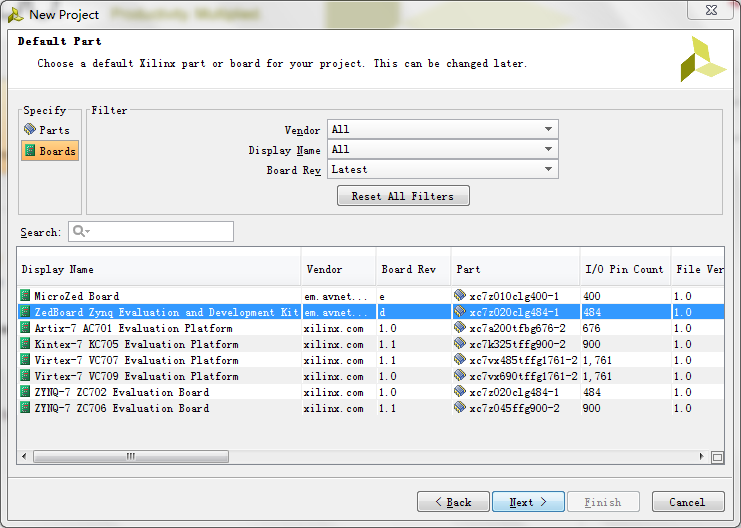

选择verilog语言,不添加文件,然后一直点击下一步:到了选板子的步骤,直接点击boards,

选择如图:

完成。

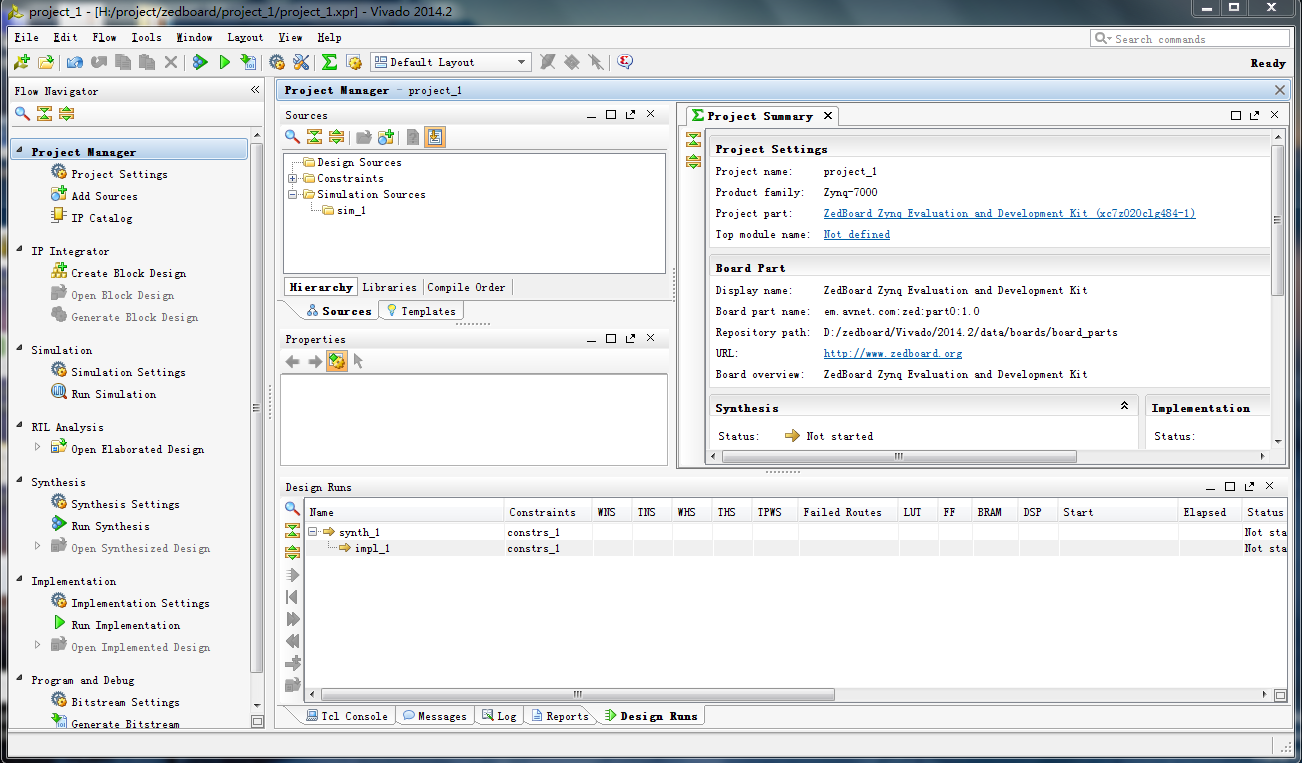

创建zynq嵌入式系统:

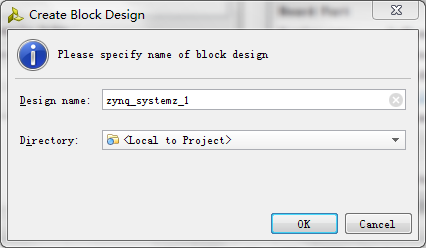

创建一个block Design ,在Flow Navigator区域展开IP Integrator,选择create Block Design

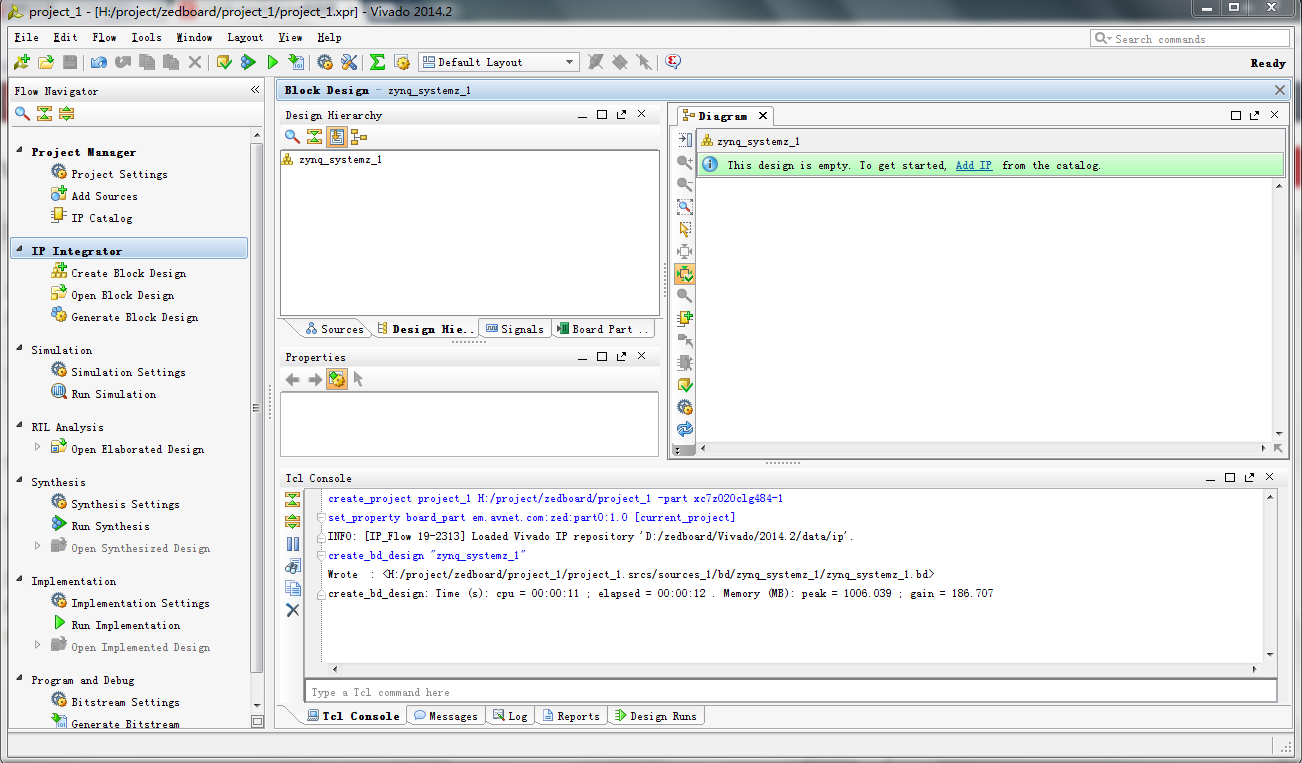

然后工作域将会打开ip Integrator 的图表画布,我们将在空白区域像画画一样构建自己的系统。这里操作的最小单位为IP核,xilinx提供的免费IP核可以直接添加使用,用户也可以自定义IP核。

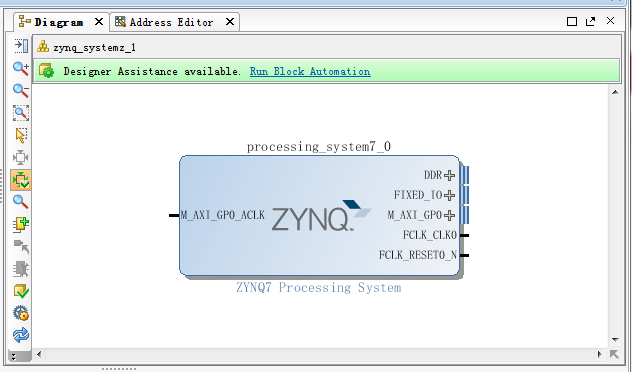

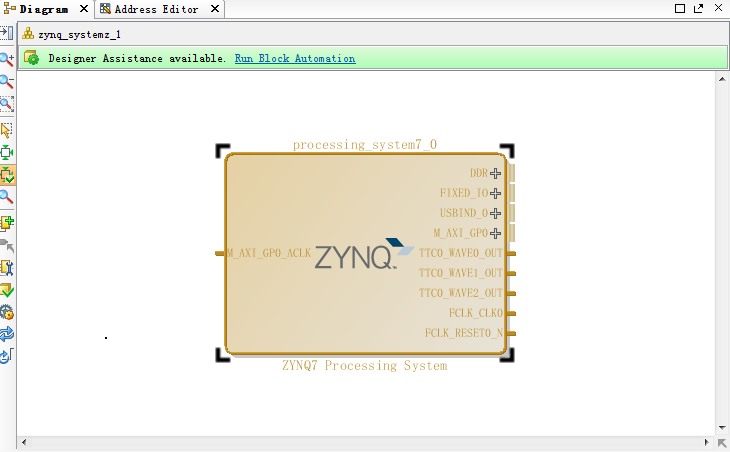

在空白板上右键点击Add IP ,在search中输入zynq ,在搜索结果中双击ZYNQ7 Processing System 添加PS端到IP核画布。

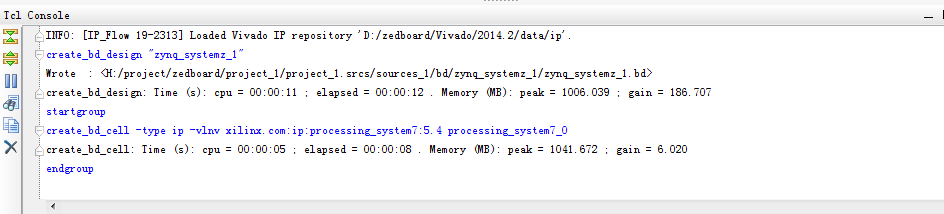

在TCl Console我们将会看到如下信息:

其实我们图形化界面所做操作,都会转化为TCL命令执行。

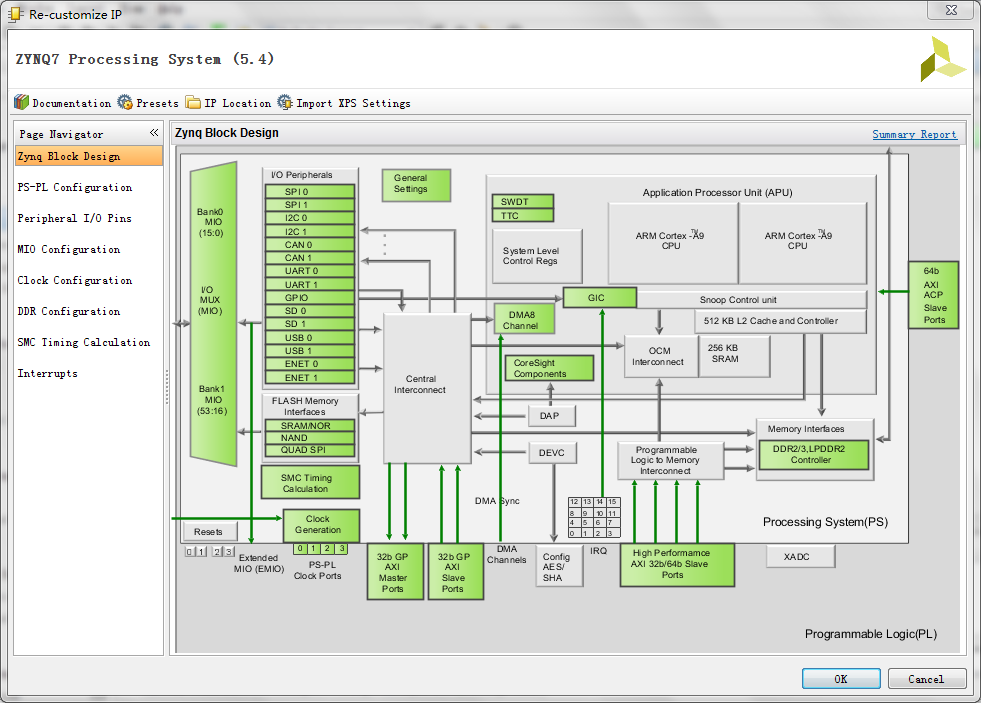

要使ps模块在zedboard中工作,还要对其进行配置,双击ps

点击Presets -> Zedboard ,使用vivado对zedboard提供的默认配置,点击ok

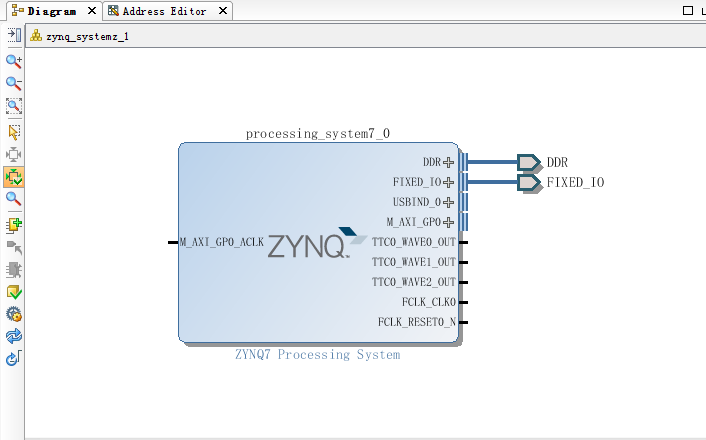

单击DDR接口,出现笔状时右键,选择 Make External ,FIXED_IO使用同样办法。

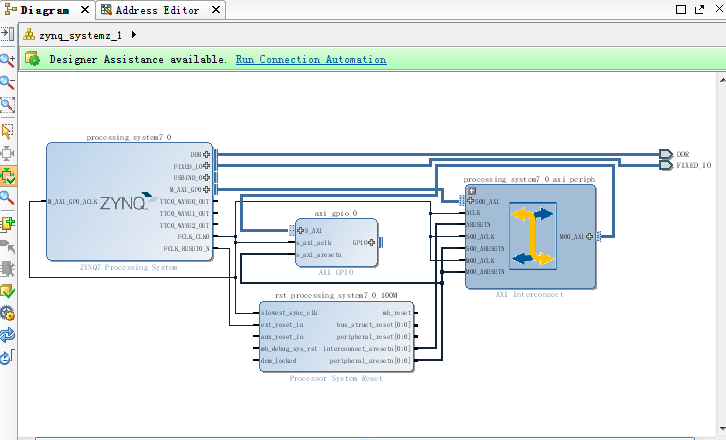

下面添加AXI GPIO IPcore到系统中。,右键单击空白处添加IP核,搜索栏输入GPIO,双击AXI GPIO 添加完成。

然后单击run connection automation 选择/axi_gpio_o/s_AXI,单击ok’有两个新IP核被自动添加了。

然后再单击run connection automation,Select Board Interface下选择leds_8bits.

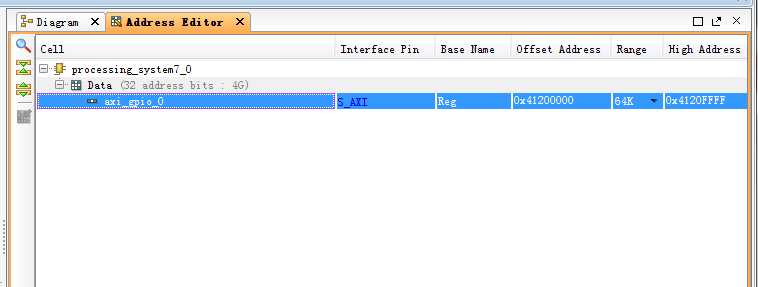

这样就基本配置完成,IP Integrator会自动为AXI总线上的逻辑设备分配地址空间,这样ARM就可以寻址到该设备。如图:

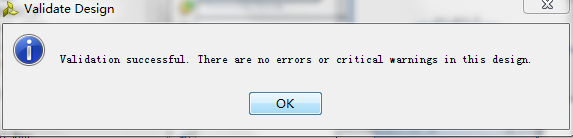

为AXI GPIO分配64k的地址空间,基地址为0x41200000,保存工程。在Diagram窗口左侧工具栏,选择Validate Dsign 按钮,检查设计有效性。

至此,IP子系统我们已经设计完成了!!!下面我们将设计完成Block Dsign生成可以综合的HDL设计文件。

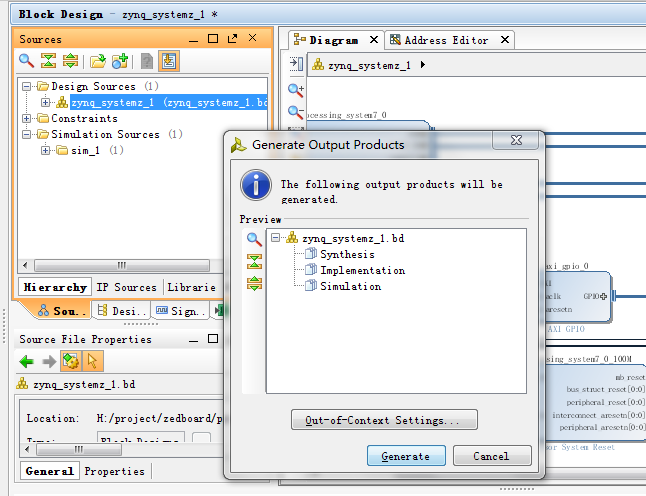

在Sources 窗口,右键zynq_system_1 选择Generate Output Products

单击generate,生成HDL源文件和相应端口的约束文件。再右击zynq_system_1,选择Create HDL Wrapper选型,单击ok’。这里vivado为IP子系统生成了一个顶层文件,使我们可以对系统进行综合、实现并生成比特流。

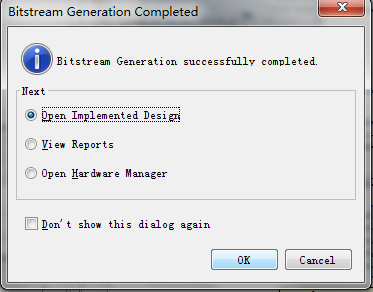

在Flow Navigator 中展开Program and debug ,单击generate Bitstream。单击ok

这一过程将持续很长时间,当完成后,会弹出一个对话框,选择open Implementation Design

将设计导入SDK,然后就可以对ARM编程,控制zedboard的led小灯了。

展开IP Integrator并单击 open Block Design 选择弹出的zynq_system_1.bd

执行file->export->export hardware for sdk 命令,弹出的对话框确保复选按钮被选上。

下一个博客将在sdk中完成对小灯的编程!这次博客结束!~~~好累!

7898

7898

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?