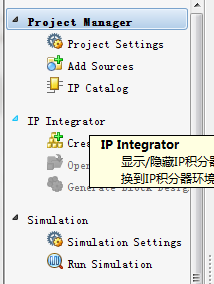

在Zedboard上单纯使用PL其实和FPGA开发流程一样,只不过是在vivado上。打开vivado14.2 新建一个工程 ,前两步的复选项都要选上,点击完成。

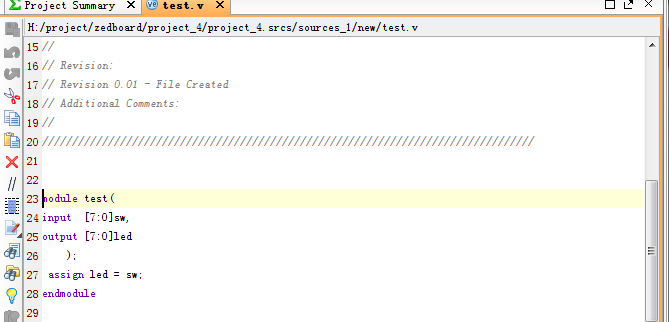

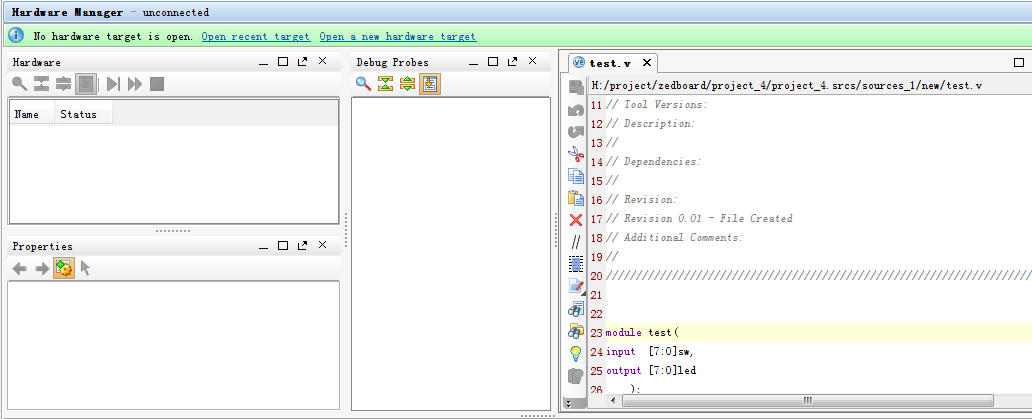

单击添加文件,命名为test.v ,用verilog语言编写下列代码:

目的是拨开开关,点亮对应的led灯。

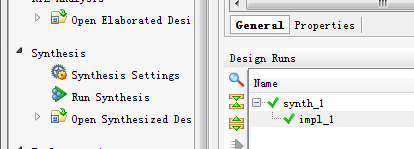

然后进行综合run synthesis ,

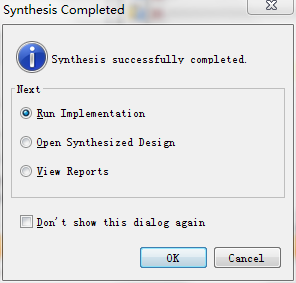

综合成功弹框会弹出,点击run Implementation ,也就是进行实现的过程。

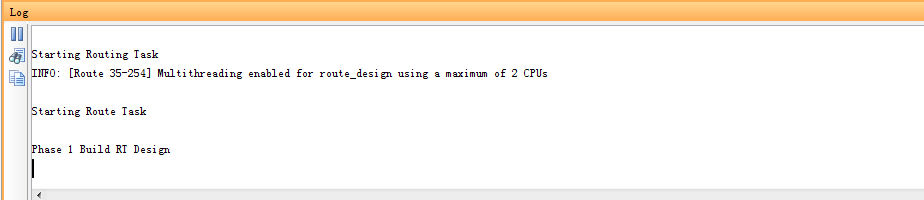

这是信息显示栏:

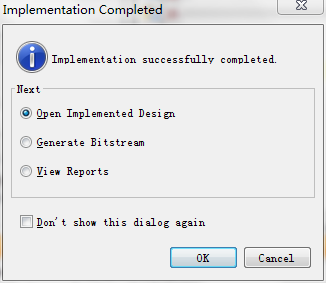

然后打开实现设计,点击ok

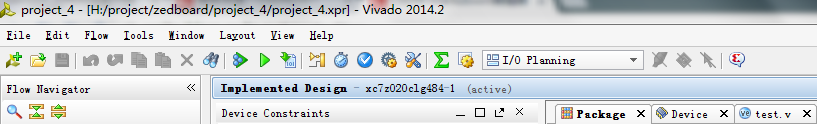

然后点击这里,改为i/oplaying

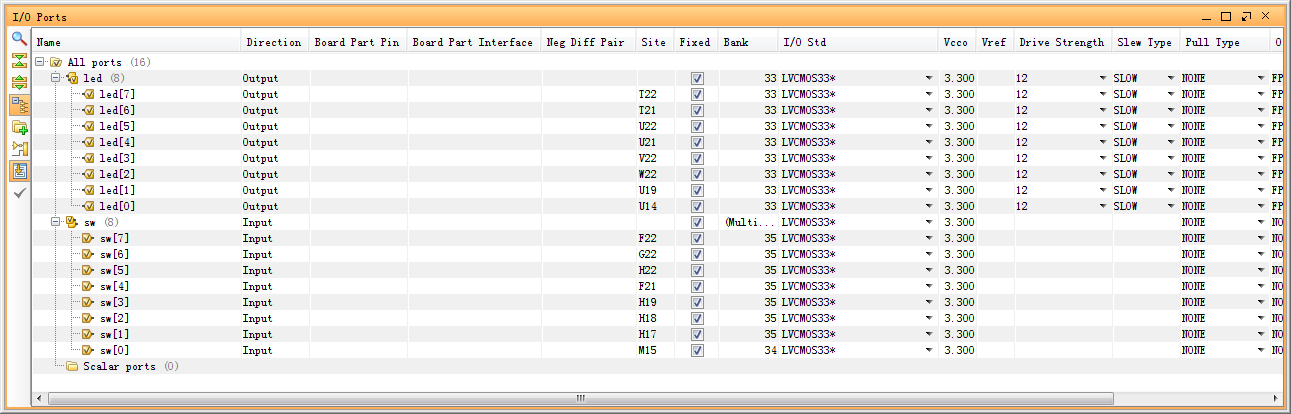

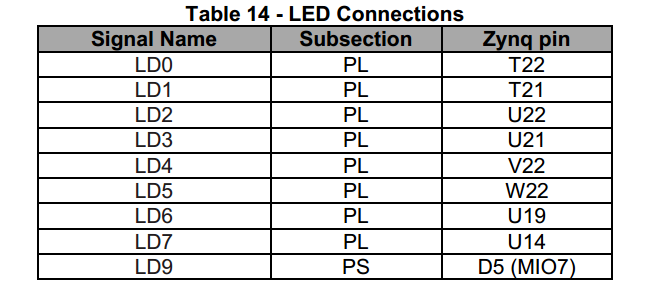

更改下方i/o引脚配置,配置为图中所示:

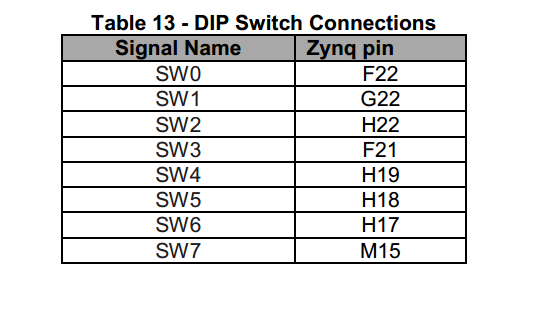

这个是根据xilinx公司提供的芯片硬件指南上给的参数配置的,这里贴出:

然后再运行实现

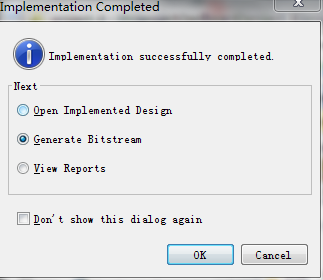

点击生成比特流。

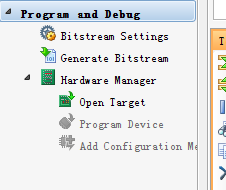

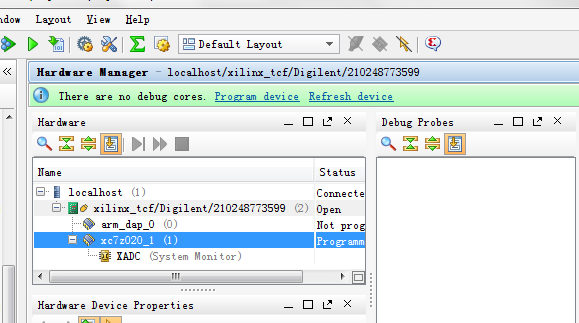

然后点击打开硬件:

如图:

连接Zedboard到pc,串口和JTAG口。

单击上图中窗口上边的提示,单击“打开最近的目标”。

然后右键该设备,选择program即可完成。

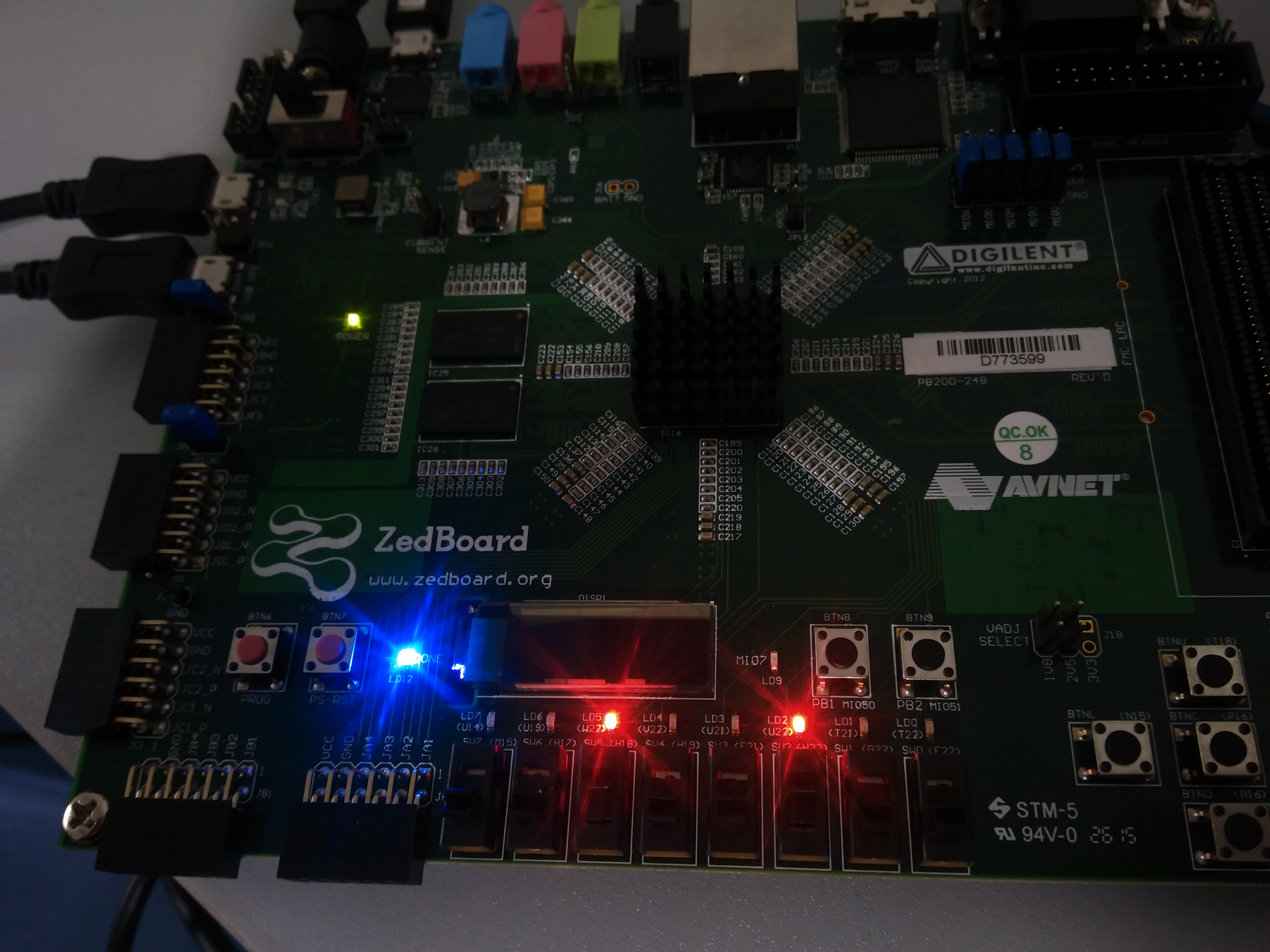

成功。

640

640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?