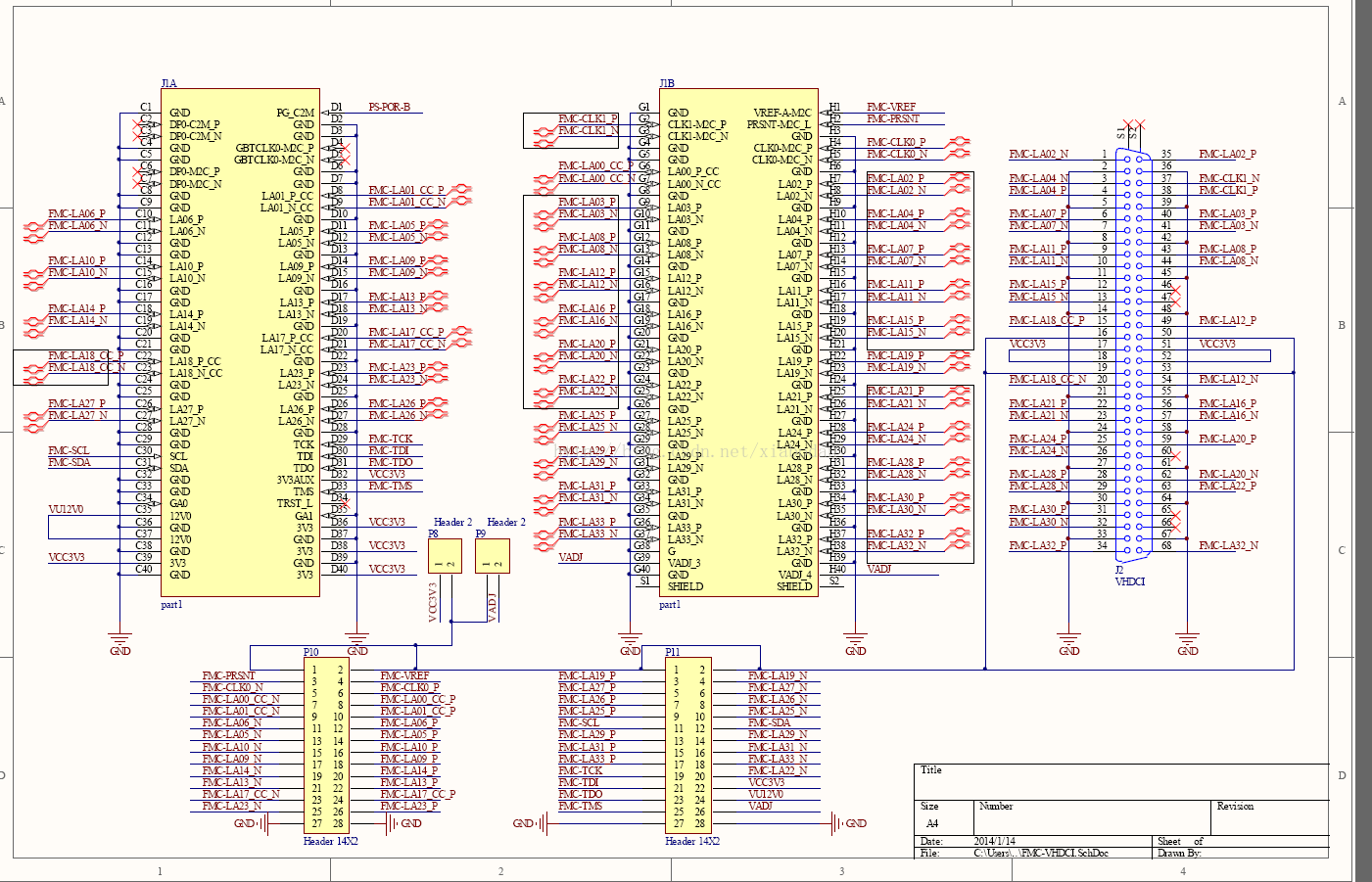

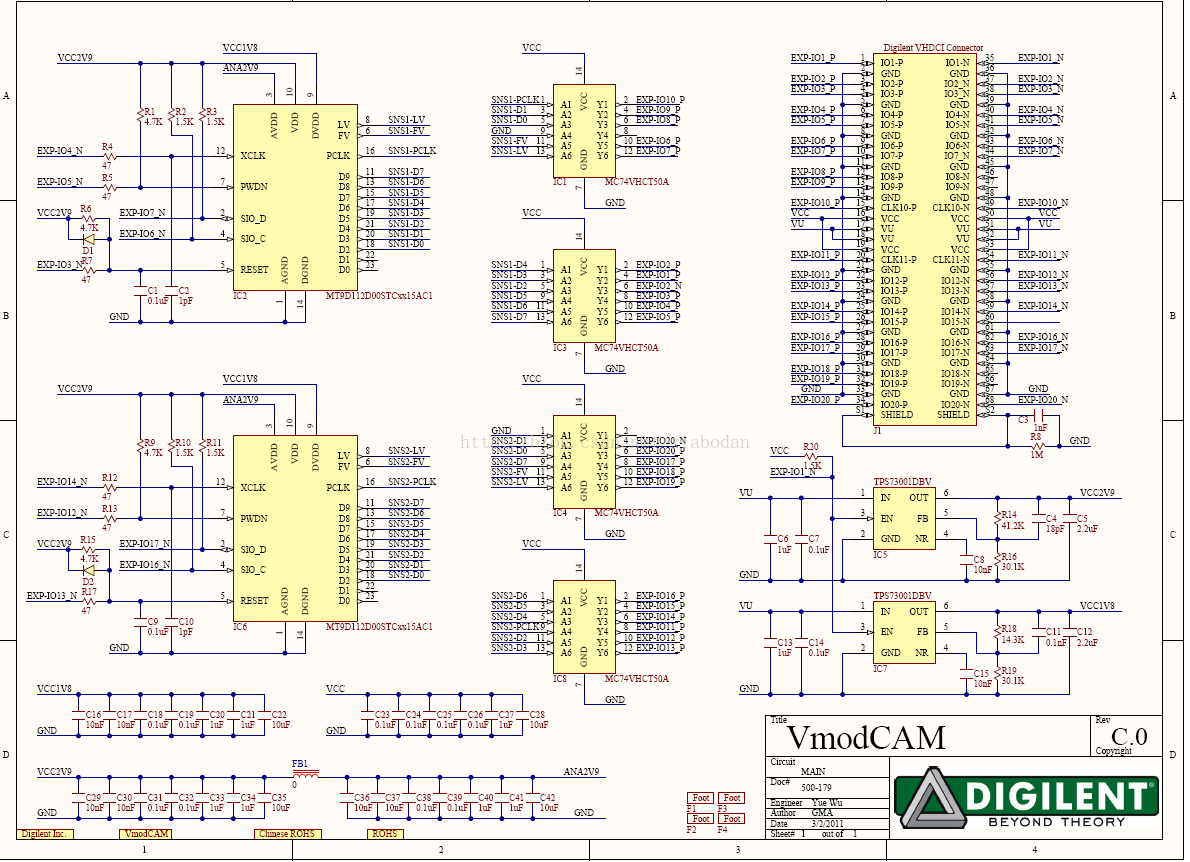

自己画了一块FMC-VHDCI四层板,外接VmodCAM,接口定义如下

#CAMA PIN CONSTRACT

NET "CAMA_D_I[7]" LOC = T17 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[6]" LOC = T16 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[5]" LOC = M21 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[4]" LOC = M22 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[3]" LOC = P18 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[2]" LOC = C19 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[1]" LOC = J17 | IOSTANDARD = LVCMOS33;

NET "CAMA_D_I[0]" LOC = J16 | IOSTANDARD = LVCMOS33;

NET "CAMA_FV_I" LOC = N17 | IOSTANDARD = LVCMOS33;

NET "CAMA_LV_I" LOC = N18 | IOSTANDARD = LVCMOS33;

NET "CAMA_PCLK_I" LOC = D20 | IOSTANDARD = LVCMOS33;NET "CAMA_PCLK_I" IN_TERM = UNTUNED_SPLIT_50;

NET "CAMA_MCLK_O" LOC = N22 | IOSTANDARD = LVCMOS33;

NET "CAMA_SDA" LOC = J22 | IOSTANDARD = I2C;

NET "CAMA_SCL" LOC = J21 | IOSTANDARD = I2C;

NET "CAMA_PWDN_O" LOC = P22 | IOSTANDARD = LVCMOS33;

NET "CAMA_RST_O" LOC = D18 | IOSTANDARD = LVCMOS33;NET "CAMA_RST_O" DRIVE = 24;

#CAM Board VCC2V9 VCC1V8 Enable

NET "CAMX_VDDEN_O" LOC= P17 | IOSTANDARD = LVCMOS33;

#CAMB PIN CONSTRACT

NET "CAMB_D_I[7]" LOC = A17 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[6]" LOC = A16 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[5]" LOC = A19 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[4]" LOC = A18 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[3]" LOC = E20 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[2]" LOC = E19 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[1]" LOC = B22 | IOSTANDARD = LVCMOS33;

NET "CAMB_D_I[0]" LOC = B21 | IOSTANDARD = LVCMOS33;

NET "CAMB_FV_I" LOC = C15 | IOSTANDARD = LVCMOS33;

NET "CAMB_LV_I" LOC = B15 | IOSTANDARD = LVCMOS33;

NET "CAMB_PCLK_I" LOC = C20 | IOSTANDARD = LVCMOS33;NET "CAMB_PCLK_I" IN_TERM = UNTUNED_SPLIT_50;

NET "CAMB_MCLK_O" LOC = G20 | IOSTANDARD = LVCMOS33;

NET "CAMB_SDA" LOC = G19 | IOSTANDARD = I2C;

NET "CAMB_SCL" LOC = G21 | IOSTANDARD = I2C;

NET "CAMB_PWDN_O" LOC = J20 | IOSTANDARD = LVCMOS33;

NET "CAMB_RST_O" LOC = K21 | IOSTANDARD = LVCMOS33;接下来开始写代码采集图像,处理,未完待续.......

如果上天真是要亡我,何不早点

--我们都是时间中的一枚符号,谁也没有决定自己命运的权利

本文详细介绍了如何自定义FMC-VHDCI四层板并对接VmodCAM,包括接口定义与配置,以及初步的图像采集过程。

本文详细介绍了如何自定义FMC-VHDCI四层板并对接VmodCAM,包括接口定义与配置,以及初步的图像采集过程。

615

615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?