与或非逻辑门实验

一、实验目的及实验环境

(1)了解Vivado软件的使用方法。

(2)了解与、或、非及三态门在FPGA中的用法。

(3)了解Verilog硬件描述语言的基本写法。

二、实验内容

用verilog语言实现相应的门逻辑电路

三、方案设计

1、与门逻辑电路的实现步骤:

(1)建立项目把verilog文件和约束文件添加到项目中

(2)之后点击左侧监视器里的Open Elaborated Design,等待数秒后可以看到逻辑电路,如下图

(3)按照下面顺序依次执行(每次执行都要等右上角的圈圈打勾后再开始下一步)综合,布线

(4)生成比特流,连接电路板

(5)拨动开关观察灯亮情况

2、使用SW5和SW6作为输入,以及使用LED7作为逻辑门的输出的步骤:

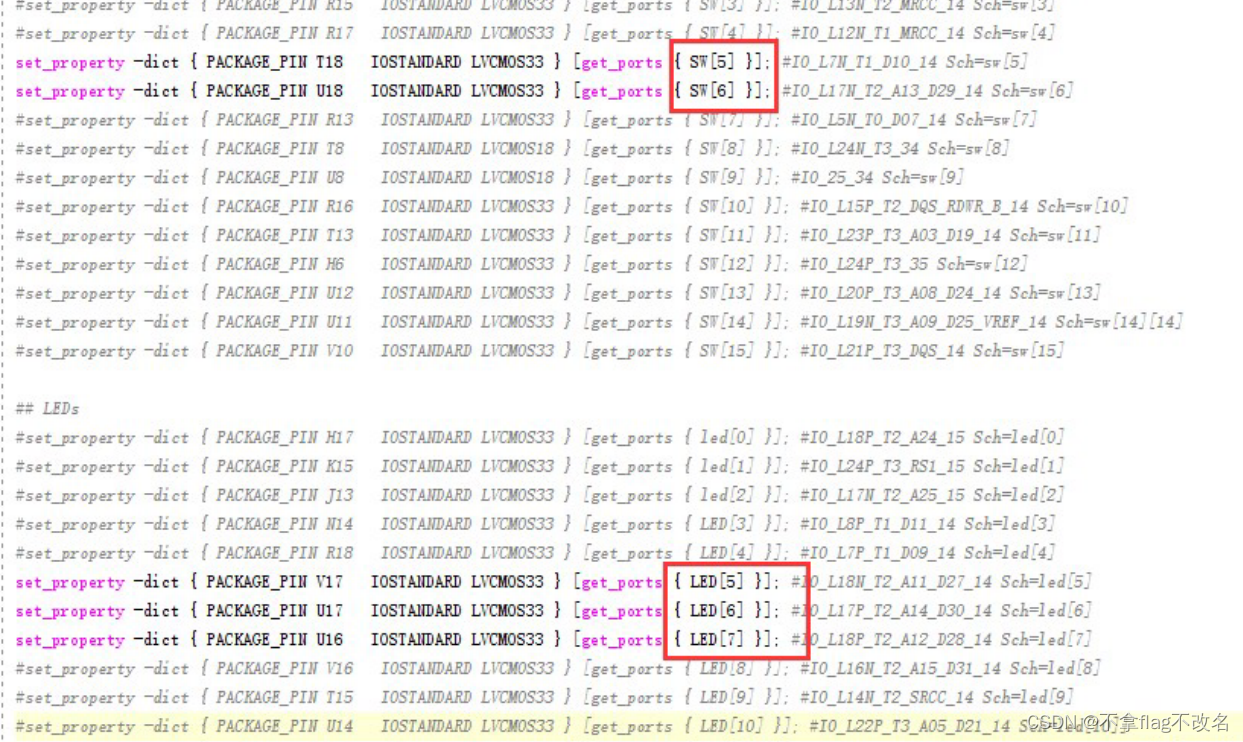

(1)修改约束文件如下

(2)步骤和1、相同,最终生成比特流之后拨动开关,来观察灯亮情况

3、或门的实现步骤:

(1)修改约束文件中的表达式为如下

(2)点击左侧监视器里的Open Elaborated Design,之后可以看到或门的逻辑图如下

(3)一直按照顺序执行,直到生成比特流文件烧入到电路板后,开始拨动开关来观察灯的情况

4、非门实现的步骤:

(1)修改表达式,一输入三输出

(2)点击左侧监视器里的Open Elaborated Design,之后可以得到非门的逻辑图

(3)运行结果图

1137

1137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?