三、高速缓冲存储器

1、某容量为256MB的存储器,由若干4M × 8位的DRAM芯片构成,则该DRAM芯片的地址引脚和数据引脚总数是多少?提示:注意 DRAM 的地址线是复用的。

4M需要22根地址线,地址线复用减半。所以需要地址线11根,数据线8根。

3.1概述

1.问题的提出

CPU和主存间存在速度差异,避免出现CPU“空等”现象

局部性原理:

空间局部性:在将来要用到的信息,可能与现在正在使用的信息在存储空间上是相近的。

时间局部性:在将来要用到的信息,可能是现在正在使用的信息。

2.Cache的工作原理

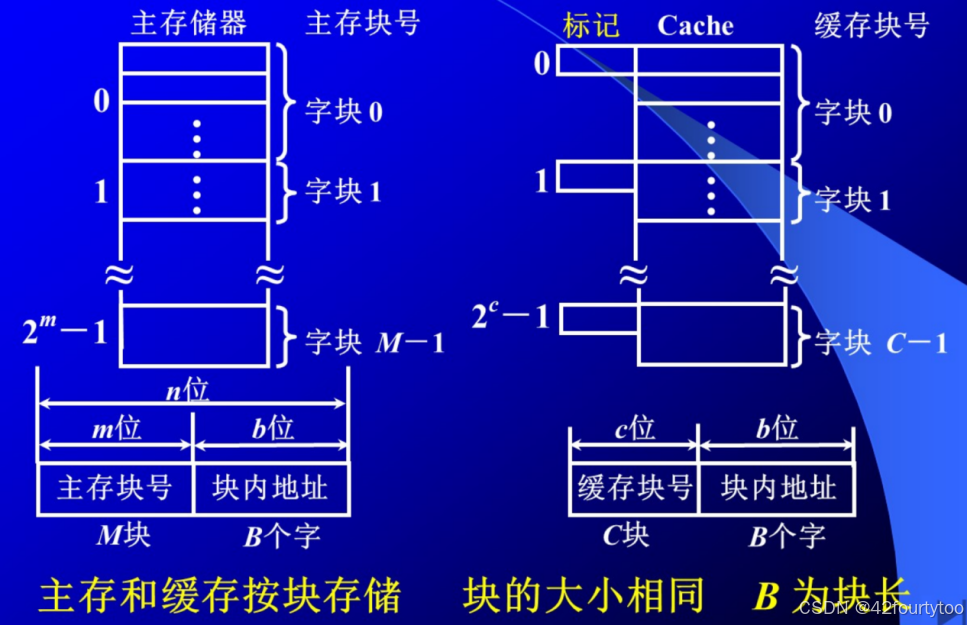

(1)主存和缓存的编址

主存,地址有n位,b位用于块内存储单元的编号,m位用于块号的编号

缓存,块内地址和主存相同,但块数较少,而且有标记用于标记对应主存的块号

缓存块长为4个16位的字,容量为4096字,主存容量为64K字,则缓存有[填空 1 ]块,主存有[填空 2 ] K块。

1024,16

(2)命中与未命中

缓存共有C块,主存共有M块,M>>C

命中:主存块已调入缓存,主存块与缓存块建立了对应关系

未命中:主存块未调入缓存,主存块与缓存块未建立对应关系

任何时刻都有一些主存块处在缓存块中。 CPU 欲读取主存某字时,有两种可能:一种是所需要的字已在缓存中,即可直接访问 cache( CPU 与 Cache 之间通常一次传送一个字);另一种是所需的字不在 Cache 内,此时需将该字所在的主存整个字块一次调人 cache 中( cache 与主存之间是字块传送)。如果主存块已调人缓存块,则称该主存块与缓存块建立了对应。

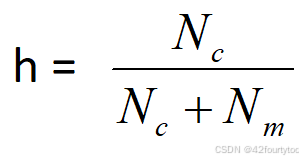

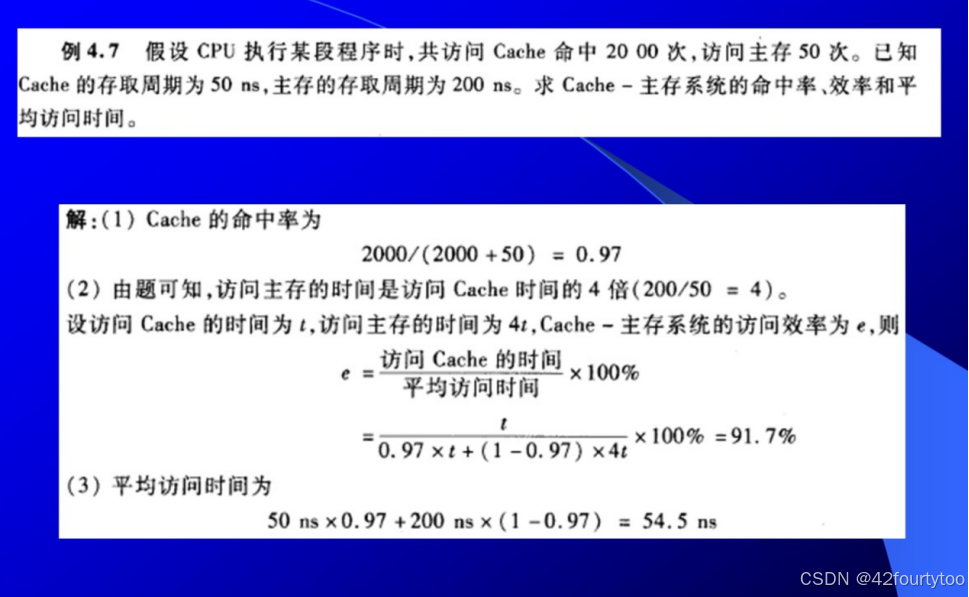

(3)Cache的命中率

CPU欲访问的信息在Cache中的比率。

命中率: ,Nc为访问Cache的总命中次数,Nm为访问主存的总次数。

,Nc为访问Cache的总命中次数,Nm为访问主存的总次数。

命中率与Cache的容量和块长有关。一般每块可取4~8个字。块长取一个存取周期内从主存中调出的信息长度。

如IBM 370 / 168,4体交叉,块长取4个存储字

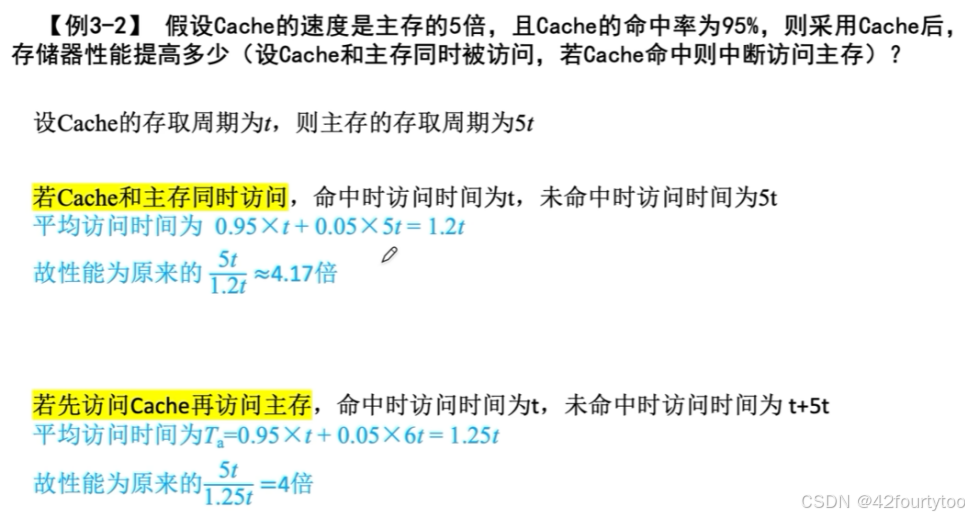

(4)Cache-主存系统的效率

效率e与命中率有关

平均访问时间 = h*tc +(1-h)*tm,tc是访问Cache的时间,tm是访问主存的时间。

e = 访问Cache的时间/平均访问时间*100%

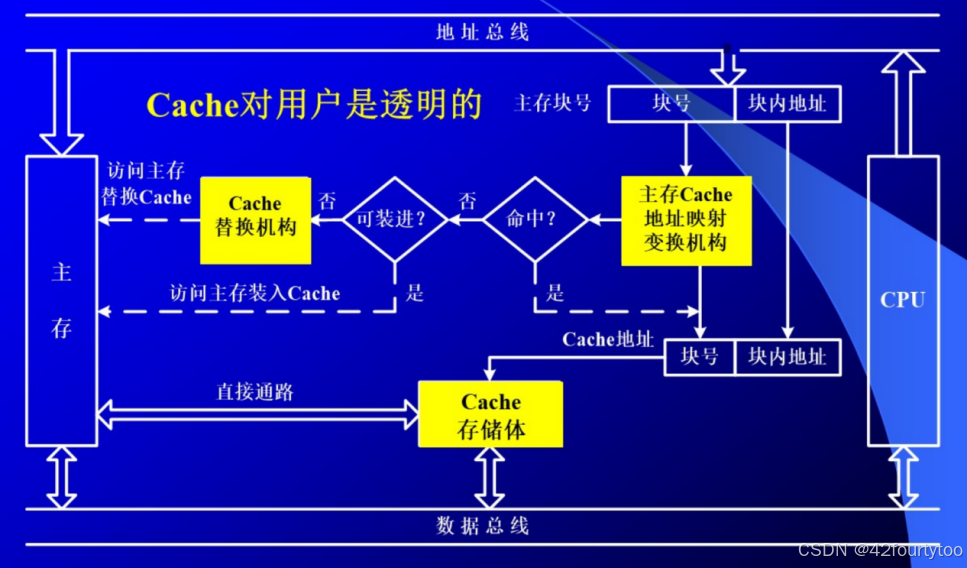

3.Cache的基本结构

CPU申请到总线后,开始发送地址;地址被拆解为块号和块内地址;块号到主存/Cache地址映射变换结构进行查找;如果命中,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1786

1786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?