-

设计任务和要求

[实验目的]

(1)掌握简易数字钟的工作原理。

(2)能熟练应用编码器、译码器、锁存器设计电路。

[实验内容]

问题描述:简易数字钟具有计时、暂停、复位、校准,闹钟的五大基本功能。数字钟在1Hz信号的作用下自动工作,每来一个时钟信号,秒增加1秒,当秒从59跳到00时,分钟增加1分,当分从59跳到00时,小时增加1小时。注意,小时的范围是从00~23时。

[实验方法及原理]

在Multisim上完成电路仿真,搭建实物电路完成电路设计

-

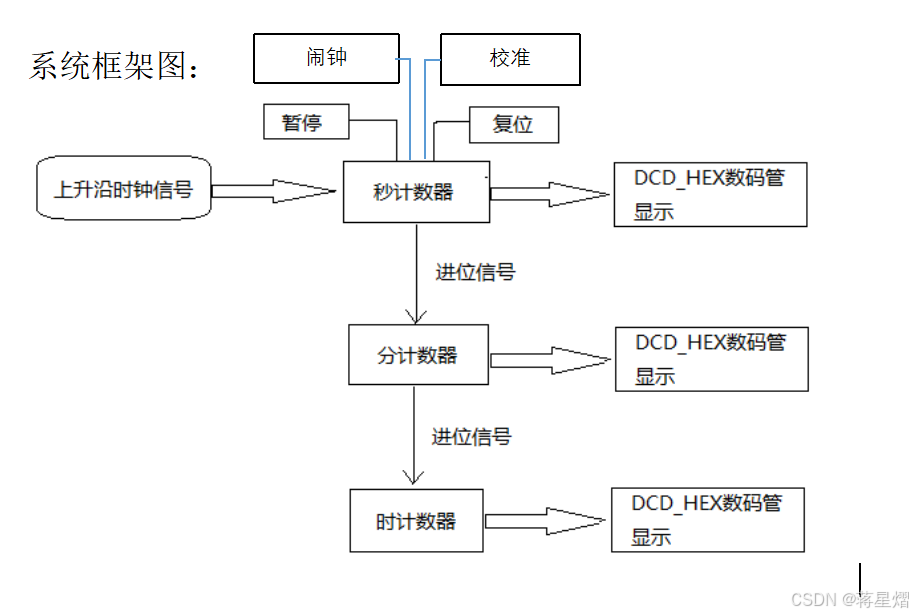

整体设计方案及系统框图

为了实现简易数字钟的功能,我们需要设计一个系统,该系统由以下几个关键部分组成:

- 计数器:计数器由秒计数器、分计数器和时计数器组成。秒和分计数器为60进制,时计数器为24进制。每个计数器都是一个独立的模块,负责记录各自的时间单位。

- 译码器和显示部分:译码器负责将计数器的二进制输出转换为适合数码管显示的十进制格式。显示部分则使用DCD_HEX数码管来显示时间。

- 控制部分:包括暂停和复位和校准和闹钟功能。暂停功能可以通过一个开关来实现,当开关处于某个状态时,数字钟停止计时。复位功能可以通过一个复位按钮来实现,按下按钮后,数字钟的时间重置为00:00:00。校准功能是通过给时计数器和分计数器分别单独加一个时钟信号,设置开关,首先将时钟暂停,当开关调到时钟信号时进行校准,调到另一端停止校准,接收低位信号,恢复计时功能。闹钟功能是当达到所设定的时间时蜂鸣器响起。

-

各单元电路的设计方案及原理说明

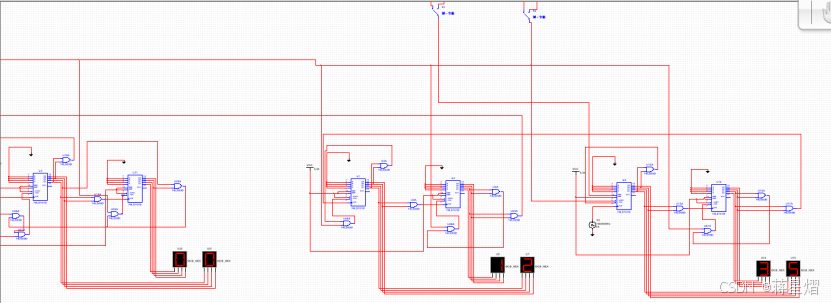

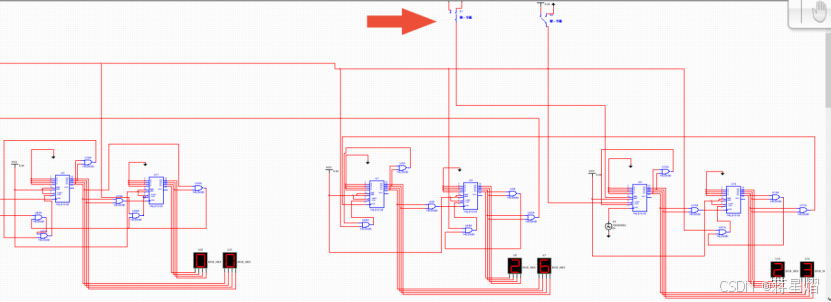

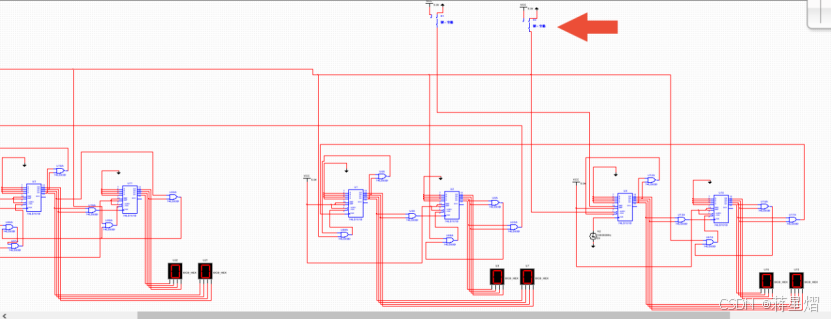

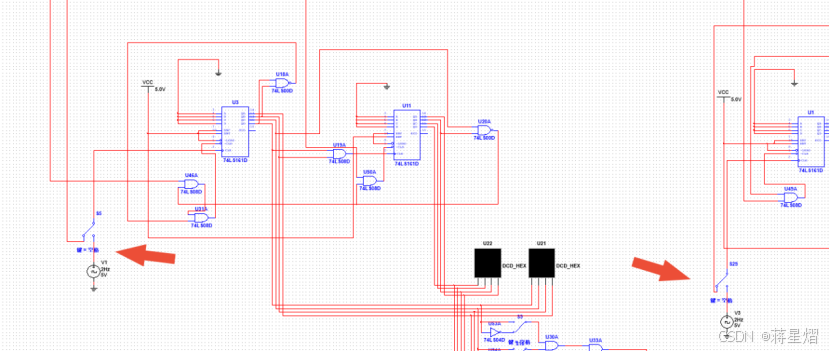

计数器:这里分秒都使用两个74ls161级联实现异步计数器,将1010的两个1输出信号连接到个位数芯片的CLR非端,使得个位数到达信号时异步清零,ENT端接VCC,输入信号0134全部接地,CP端接时钟信号。这里ENP端单独接单刀双掷开关用来实现

暂停功能,1时计数,0时保持。LOAD非端接另一控制开关实现该位数复位。输入信号连接到十位计数器的CP端作为时钟信号,输出信号‘110’时作为输入信号输入至CLR非端清零,当开关接0时也清零,两个清零信号用与门连接。将‘110’信号输出至分计数器的个位数时钟信号端,其他地方与秒计数器相似。

分计数器的时进位信号连接到时计数器的CP端作为时钟信号,时计数器是24进制,个位数有三个清零信号,一个是满10清零,一个是满24清零,一个是复位功能清零,三个用与门连接起来至CLR非端,对于十位数端,清零信号为24清零和复位功能清零,同样与起来输出CLR非端。总结起来就是清零信号的相与异步清零,进位信号输出到更高级。

暂停功能:通过控制秒计数器的个位数端达到暂停效果,当ENP端为1是开始计数,当为0时保持暂停,用开关控制。

复位功能:通过开关控制对于每一位上的数字都要清零,这里适合选用异步复位,将复位信号0和原先的清零信号相与,实现并发控制,不影响原先的清零信号,且复位信号0优先级高。

校准功能:校准功能是通过给时计数器和分计数器分别单独加一个时钟信号,设置开关,首先将时钟暂停,当开关调到时钟信号时进行校准,调到另一端停止校准,接收低位信号,恢复计时功能。

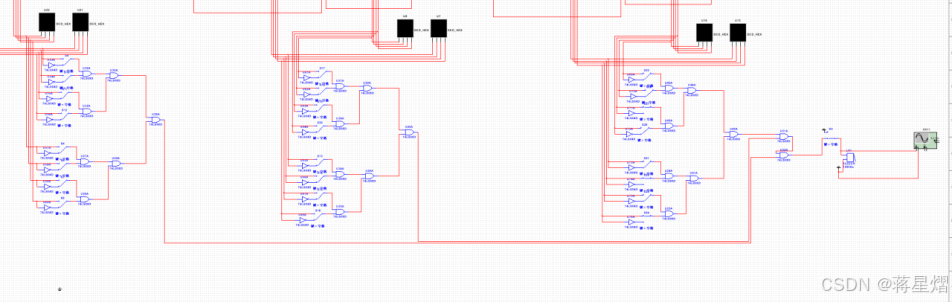

闹钟功能:该功能首先需要设定好闹钟值,当接受信号达到该值时蜂鸣器响起。需要将每一位上的所有二进制信号传给蜂鸣器,每一个二进制输出信号都要设置反相器,即非门,和单刀双掷开关。举例:

9的二进制为1001,设置9时闹钟则将两个0位信号调到非门一端,两个1信号在输出信号端。通过设置秒分时的预定值,即可唤起蜂鸣器。

-

调试过程及结果分析

该简易时钟有四个基本功能:

1.计时:

2.暂停:

3.复位:

4.校准:

5.闹钟:

-

附录(元器件清单)

| 74ls161 | 计数器芯片 |

| 74ls08 | 与门 |

| 74ls04 | 非门 |

| 74ls00 | 与非门 |

| CLOCK_VOLTAGE | 1HZ时钟信号 |

| VCC | 电源 |

| GROUD | 地 |

| DCD_HEX | 数码管 |

| SPDT | 单刀双掷开关 |

multisim电路:

在我的资源里

1426

1426

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?