PTX作为英伟达GPU的底层语言,既是性能优化的利器,也是打破生态垄断的突破口。其“类汇编”特性赋予开发者对硬件的极致控制权,但高昂的开发成本与生态依赖仍制约其普及。随着AI技术的介入和开源生态的成熟,PTX或将成为下一代算力竞争的关键战场。

一、PTX的技术定位与核心特性

-

中间指令集的角色

PTX(Parallel Thread Execution)是英伟达GPU架构中的中间指令集架构,介于高级编程语言(如CUDA C++)和底层机器码(SASS)之间。它类似于传统计算机体系中的汇编语言,但抽象层级略高于直接操作硬件的机器码,主要用于实现跨GPU架构的兼容性。 -

接近汇编的运行层级

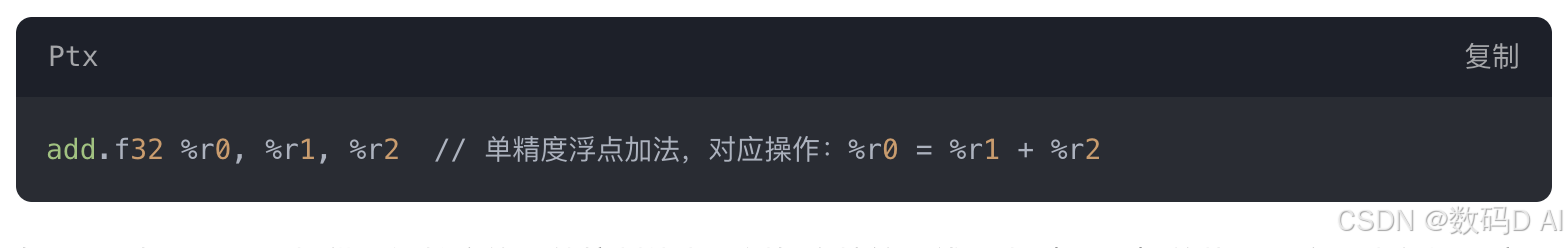

- PTX以“虚拟ISA(指令集架构)”形式存在,允许开发者进行寄存器分配、线程调度等底层硬件操作,其代码结构与汇编语言高度相似。例如,一条典型的PTX指令如下:

- 与CUDA相比,PTX提供更细粒度的硬件控制能力,例如直接管理线程束(Warp)的执行顺序,优化指令流水线。

- PTX以“虚拟ISA(指令集架构)”形式存在,允许开发者进行寄存器分配、线程调度等底层硬件操作,其代码结构与汇编语言高度相似。例如,一条典型的PTX指令如下:

二、PTX的编译流程与硬件交互

- 从CUDA到机器码的转换过程

- 阶段1:CUDA代码通过编译器(如

nvcc)生成PTX中间代码,这一层保留了对不同GPU架构的兼容性。 - 阶段2:GPU驱动程序将PTX动态编译为特定架构的SASS机器码(如H100/A100的指令集),实现硬件级优化。

- 阶段1:CUDA代码通过编译器(如

- 硬件指令的直接映射

PTX指令直接对应GPU硬件单元的操作,例如:ld.global指令触发全局内存加载,由内存控制器执行;mad.f32指令调用浮点乘加单元(FMA),减少运算延迟。

三、PTX的核心应用场景

- 极致性能优化

- DeepSeek的实践:通过直接编写PTX代码,将英伟达H800 GPU的132个流式多处理器(SM)中的20个专用于通信任务,突破硬件通信瓶颈。

- 量化计算加速:在金融高频交易等领域,PTX级优化可将延迟降低至纳秒级,例如通过

vadd指令实现向量化数据并行。

- 跨架构兼容性探索

PTX的中间层特性为国产GPU(如华为昇腾)提供移植可能性。例如,DeepSeek通过PTX积累的优化经验可迁移至其他架构,降低对CUDA生态的依赖。

四、PTX的挑战与局限性

- 开发与维护成本高

- PTX编程需手动管理内存、寄存器等硬件资源,开发复杂度远超CUDA。

- 代码移植性差:针对某代GPU(如H100)优化的PTX代码,可能无法直接适配新架构(如Blackwell)。

- 生态依赖的困境

PTX仍依附于英伟达技术栈,未完全脱离CUDA工具链。例如,PTX代码需依赖英伟达驱动程序编译为SASS,难以直接运行于AMD/国产GPU。

五、未来趋势:PTX与AI的协同进化

-

AI辅助生成PTX代码

DeepSeek-R1等模型已展示自动生成优化代码的能力,未来可能通过强化学习实现PTX指令的自动化编排。 -

开源生态的扩展

通过开源PTX优化工具链(如MIT许可证项目),推动跨厂商硬件适配,削弱CUDA的垄断地位。

PTX相比汇编语言的核心优势

PTX的核心优势在于在底层硬件控制与开发效率之间取得平衡:既支持寄存器分配、线程调度等细粒度优化,又能依托CUDA生态降低开发门槛。相比之下,直接编写GPU汇编语言虽能榨取极限性能,但需牺牲可移植性、工具链支持和开发效率,仅适用于特定场景(如高频量化交易或DeepSeek级的技术攻坚)。

PTX(Parallel Thread Execution)作为NVIDIA GPU架构中的中间指令集,相比直接编写GPU汇编语言(如SASS),在开发效率、可移植性、性能优化等方面具有显著优势:

一、抽象层级与开发效率

- 更高层级的编程接口

PTX提供了类似汇编的底层控制能力,但通过指令集抽象简化了硬件操作。例如:- PTX支持显式的线程块(Block)和网格(Grid)定义,而汇编需手动管理线程调度。

- 开发者可直接使用

ld.global(全局内存加载)等高级指令,无需处理底层内存地址计算。

- 与CUDA工具链的无缝集成

PTX兼容CUDA编译器(如NVCC),支持从CUDA代码自动生成PTX中间表示,开发者可复用CUDA生态的调试工具和数学库。而直接编写汇编需完全脱离CUDA生态,开发成本极高。

二、跨架构兼容性与可移植性

-

硬件无关性设计

PTX作为中间表示语言,可在不同代际的NVIDIA GPU上运行(如H100到A100),代码只需重新编译为目标架构的SASS指令。汇编代码则与具体GPU型号绑定,更换硬件需完全重写。 -

动态适配硬件特性

例如,PTX的warp.sync指令可自动适配不同GPU的Warp大小(32或64线程),而汇编需针对不同架构手动调整线程同步逻辑。

三、性能优化与资源控制

- 细粒度优化的灵活性

PTX允许直接控制寄存器分配、线程调度等关键参数:- DeepSeek通过PTX将H800 GPU的20个SM专用于通信任务,实现硬件资源的最优分配。

- 可定制化流水线算法,减少L2缓存争用,相比CUDA提升10倍硬件利用率。

- 性能与开发成本的平衡

虽然PTX编程复杂度高于CUDA,但其仍保留了一定的抽象能力。例如:- PTX支持向量化指令(如

vadd.f32),单条指令可完成多数据并行计算,而汇编需显式展开循环。 - 开发者可通过PTX实现90%的硬件极限性能,而汇编优化仅能额外提升2-3%,但维护成本翻倍。

- PTX支持向量化指令(如

四、生态与工具支持

-

调试与性能分析工具

NVIDIA Nsight等工具支持PTX级别的性能剖析(如指令吞吐量、寄存器占用分析),而汇编调试需依赖第三方逆向工程工具。 -

混合编程模式

开发者可混合使用CUDA和PTX代码,例如:- 用CUDA实现算法框架,对关键路径插入PTX优化代码。

- DeepSeek 99%的代码由高级框架生成,仅1%核心计算模块采用PTX手动优化。

885

885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?