实验报告一 半加器及全加器构成及测试

| 姓名 | 学号 | ||

| 专业 | 年级 |

一、实验目标

掌握加法器的工作原理,具备简单电路的设计能力,为其设计复杂硬件电路打下基础有助于掌握计算机及相关的工程基础和专业基础知识,并能运用于计算问题的表达、证明和建模,从而支撑本专业学科基础实践能力、专业核心能力的培养。

二、实验要求

熟悉本项目相关的研究方法,完成半加器以及全加器方面的实验内容,分析、解释实验结果,形成结论,达到能解决特定的计算机软硬件问题的分析与建模方面问题的要求,培养应用系统开发的能力。

三、实验内容

(一)什么是半加器和全加器?各自有何特点?

一、半加器

半加器是一个两输入两输出的逻辑组合电路。特点:1.结构简单:只需一个异或门即可实现。2.功能单一:仅能实现两个一位二进制数相加,不考虑来自低位的进位。

- 全加器

全加器是一个三输入两输出的逻辑组合电路。特点:1.考虑进位:能处理来自低位的进位,实现三个一位二进制相加。

全加器和半加器的比较:

| 输入个数 | 输出个数 | 是否考虑来自低的进位 | 实现几位数相加 | |

| 半加器 | 2 | 2 | 否 | 2 |

| 全加器 | 3 | 2 | 是 | 3 |

(二)根据组合逻辑电路设计步骤,设计半加器和全加器,并在Logisim中仿真。

一、半加器的设计和仿真

1.输入与输出:

输入:有两个输入分别为被加数A和加数B。

输出:有两个输出分别为本位和S和向高位的进位C。

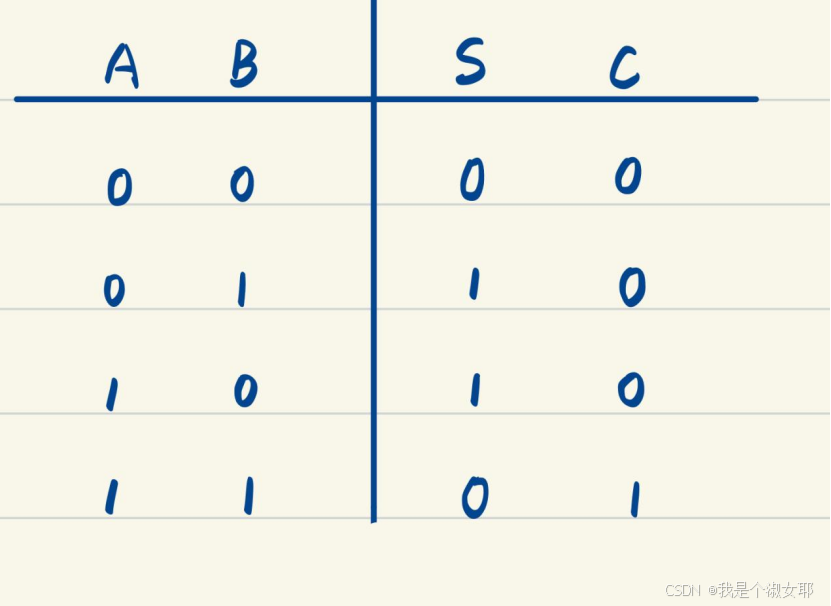

2.真值表:

3.最简与或表达式:

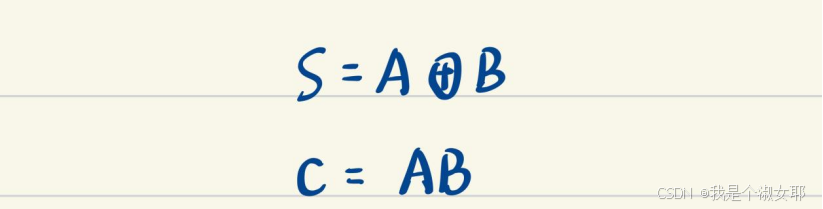

(4)电路图

图(a)半加器的电路结构

5.仿真结果:

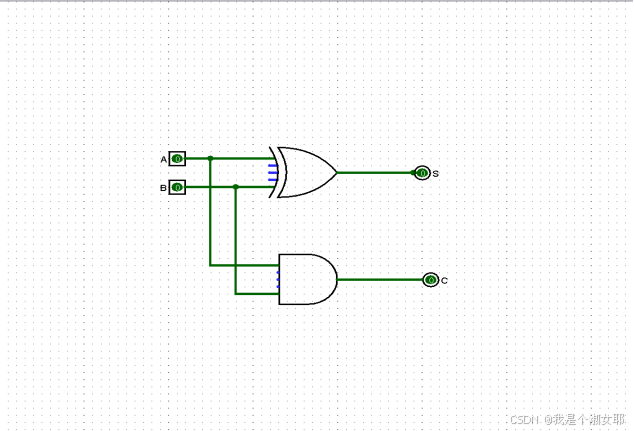

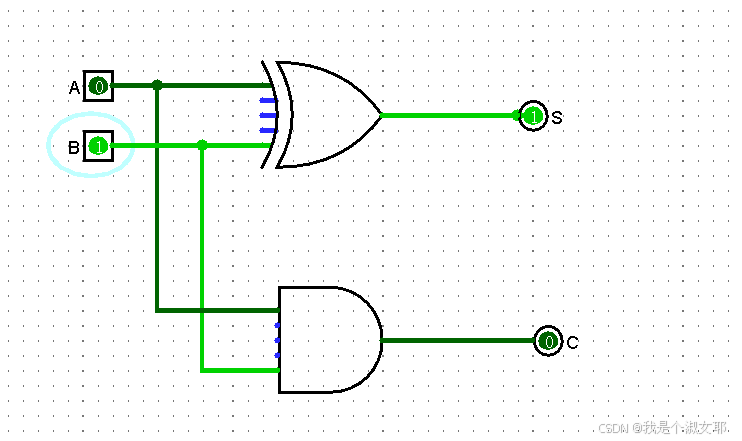

- 当输入端A=0,B=0时,相加后本位和为0,向高位的进位为0,因此输出端S=0,C=0。

图(b) 当A=0,B=0时半加器的电路结果

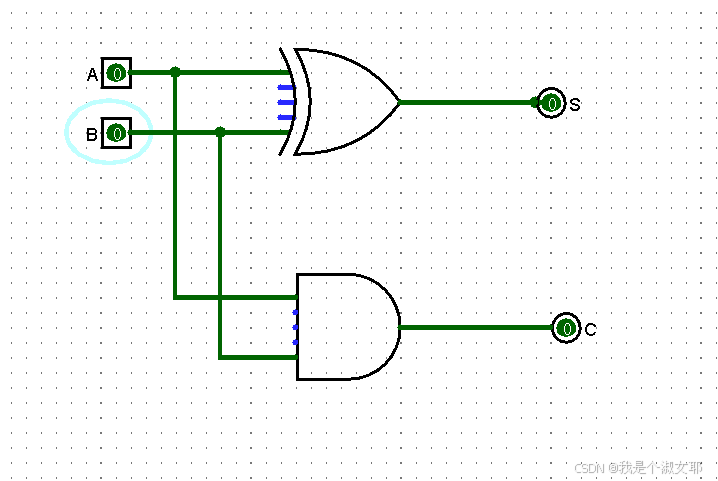

2.当输入端A=0,B=1时,相加后本位和为1,向高位的进位为0,因此输出端S=1,C=0。

图(c) 当A=0,B=1时半加器的电路结果

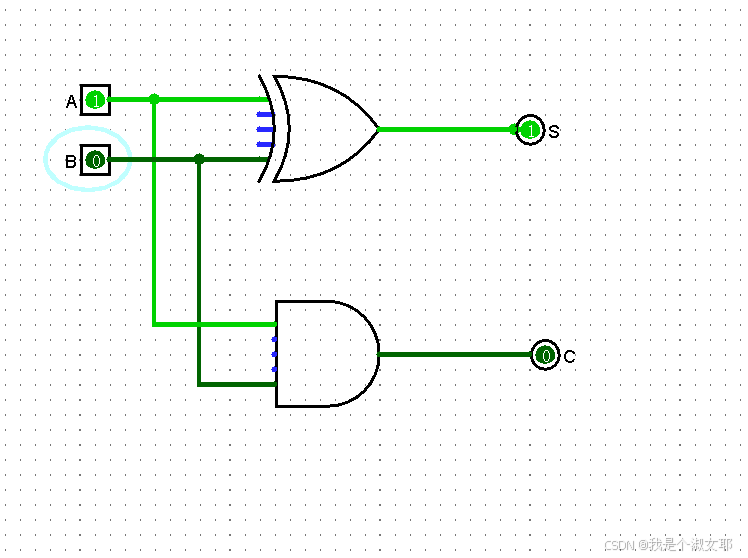

3.当输入端A=1,B=0时,相加后本位和为1,向高位的进位为0,因此输出端S=1,C=0。

图(d) 当A=1,B=0时半加器的电路结果

4.当输入端A=1,B=1时,相加后本位和为0,向高位的进位为1,因此输出端S=0,C=1。

图(e)当A=1,B=1时半加器的电路结果

二、全加器的设计和仿真

- 输入与输出:

- .输入:有三个输入分别为被加数A,加数B,以及来自低位的进位Cin。

- 输出:有两个输出分别为本位和S以及向高位的进位Cout。

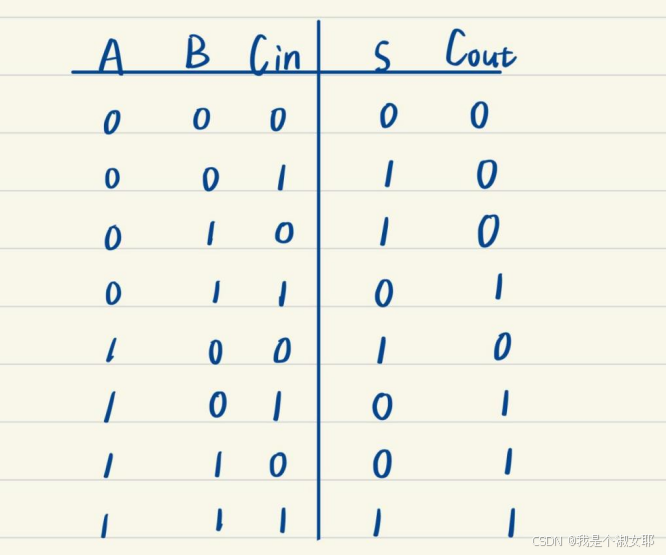

- 真值表:

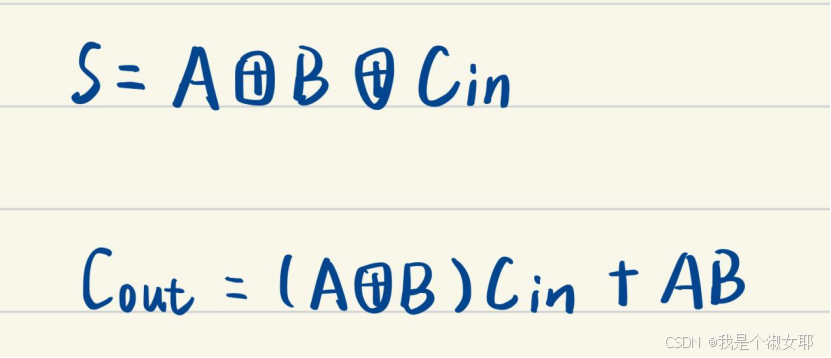

3.最简与或表达式:

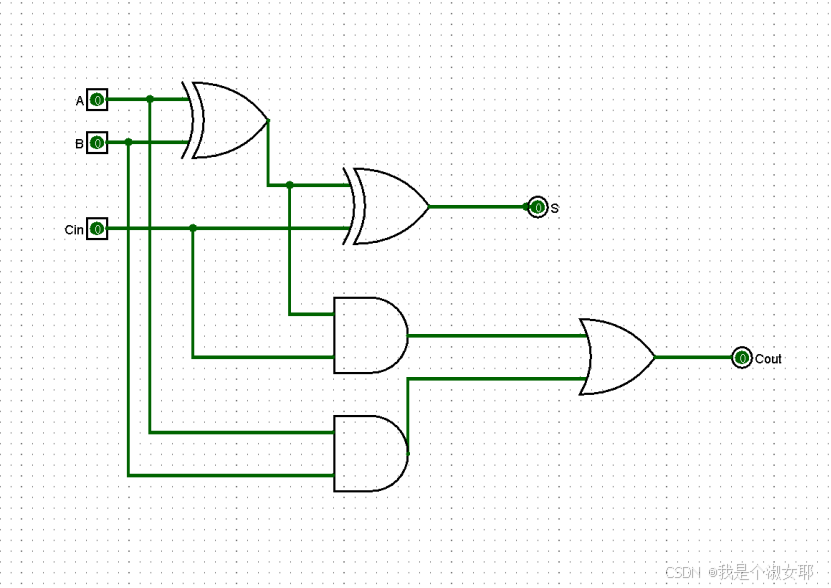

4.电路图:

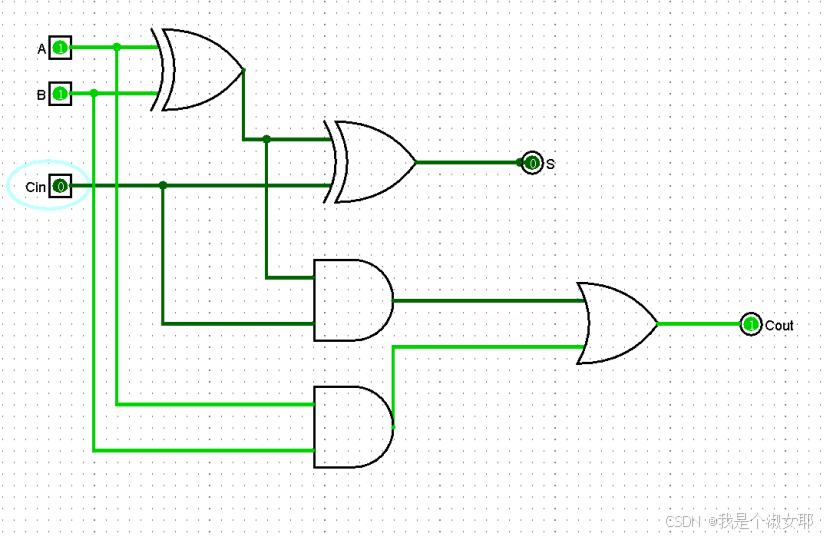

图(f)全加器的电路结构

5.仿真结果:

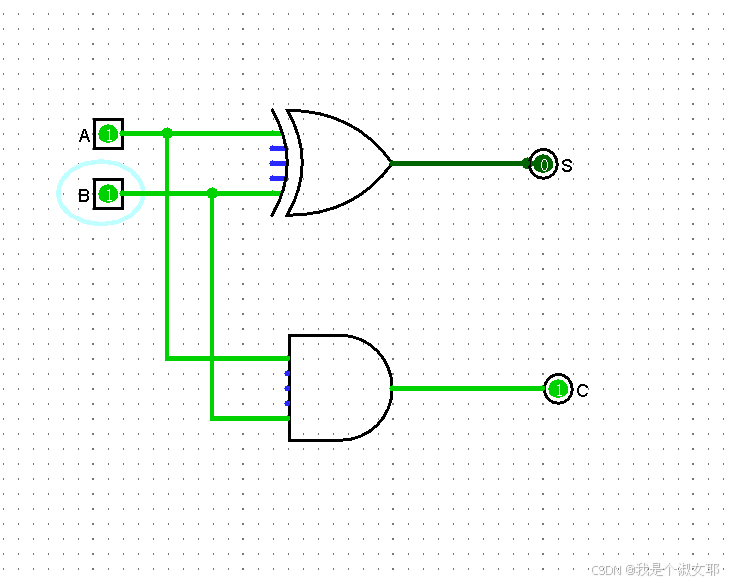

- 当输入端A=0,B=0,Cin=0时相加后本位和为0向高位的进位为0,因此输出端S=0,Cout=0。

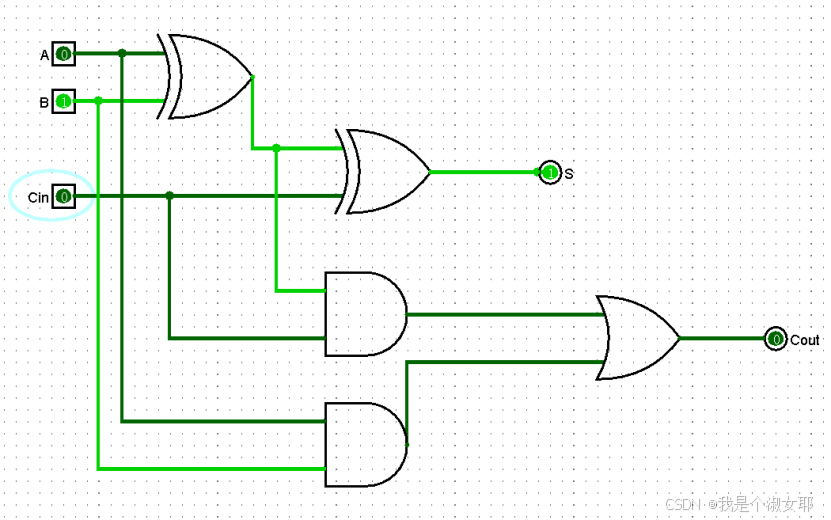

图(g)当A=0,B=0,Cin=0时全加器的电路结果

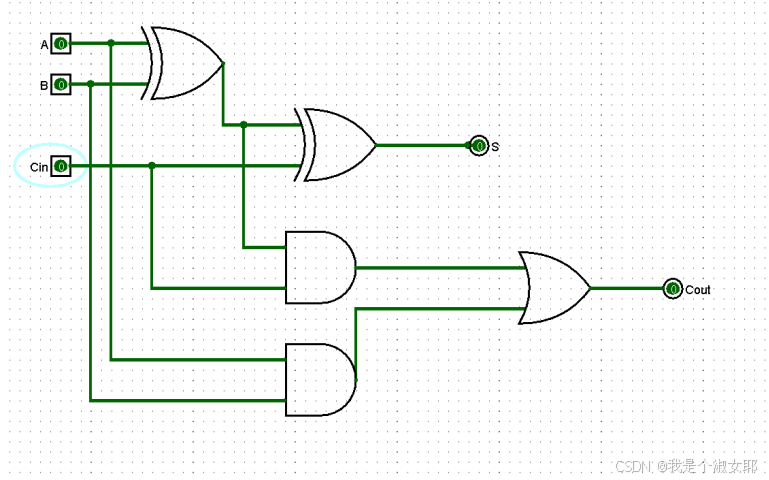

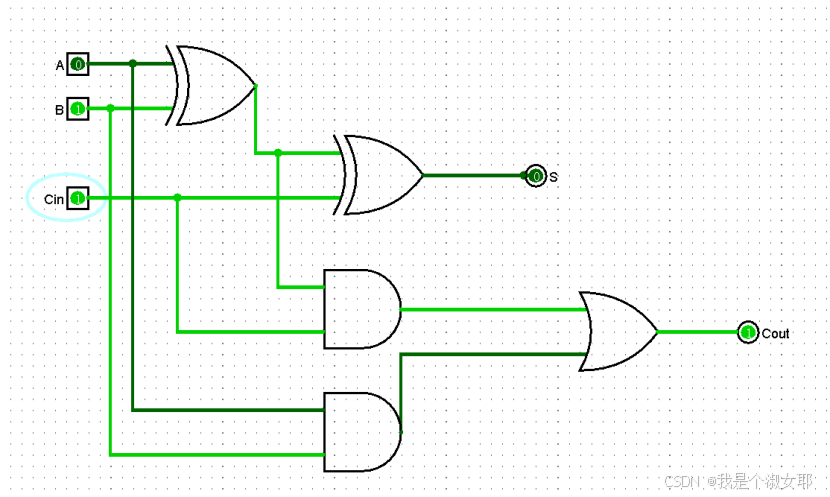

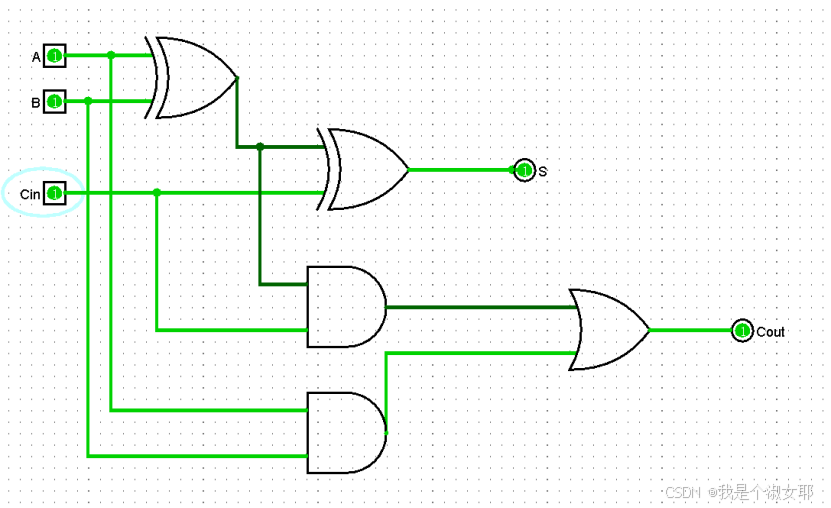

2.当输入端A=0,B=0,Cin=1时相加后本位和为1向高位的进位为0,因此输出端S=1,Cout=0。

图(h)当A=0,B=0,Cin=1时全加器的电路结果

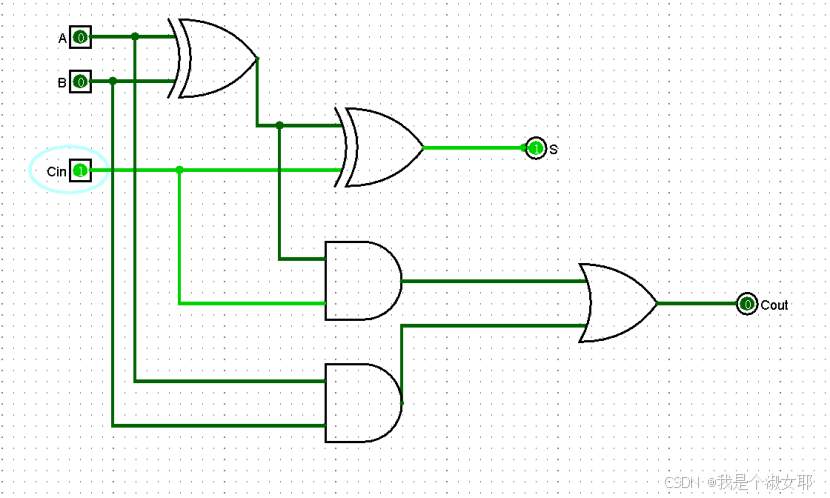

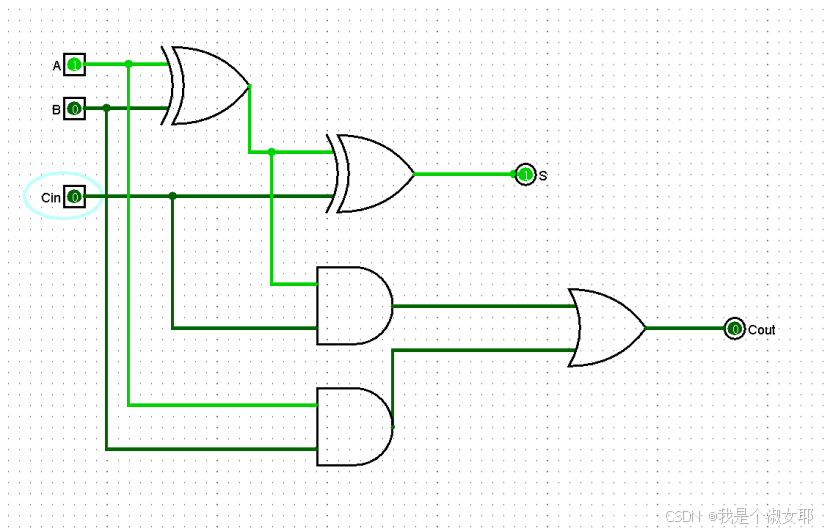

3.当输入端A=0,B=1,Cin=0时相加后本位和为1向高位的进位为0,因此输出端S=1,Cout=0。

图(j)当A=0,B=1,Cin=0时全加器的电路结果

4.当输入端A=0,B=1,Cin=1时相加后本位和为0向高位的进位为1,因此输出端S=0,Cout=1。

图(h)当A=0,B=1,Cin=1时全加器的电路结果

5.当输入端A=1,B=0,Cin=0时相加后本位和为1向高位的进位为0,因此输出端S=1,Cout=0。

图(I)当A=1,B=0,Cin=0时全加器的电路结果

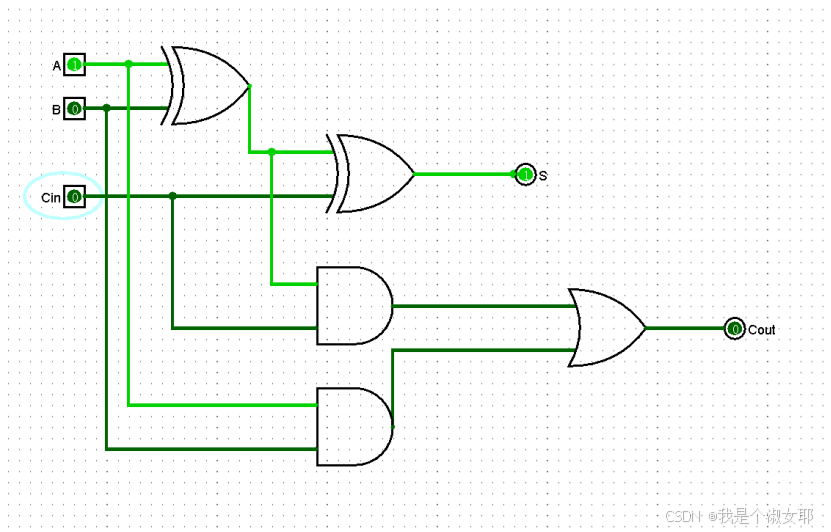

6.当输入端A=1,B=0,Cin=1时相加后本位和为0向高位的进位为1,因此输出端S=0,Cout=1。

图(l)当A=1,B=0,Cin=0时全加器的电路结果

7.当输入端A=1,B=1,Cin=0时相加后本位和为0向高位的进位为1,因此输出端S=0,Cout=1。

图(m)当A=1,B=1,Cin=0时全加器的电路结果

8.当输入端A=1,B=1,Cin=0时相加后本位和为0向高位的进位为1,因此输出端S=0,Cout=1。

图(n)当A=1,B=1,Cin=1时全加器的电路结果

三、如何利用半加器和全加器设计一个串行加法器,能实现两个四位二进制数的加法。

-

设计思路:

-

首先明确半加器和全加器的功能。半加器只能实现来自本位的两个数字的相加,不考虑来自低位的进位,产生本位和进位位;而全加器不仅可以实现来自本位的两个数字相加,还可以考虑到来自低位的进位,产生本位和进位位。

-

设计串行加法器的整体结构。由于全加器有考虑来自低位进位的这一特性,该串行加法器可以由多个加法器串联而成,接收来自低位的进位并产生本位和先前的进位,但是最低位相加时没有来自低位的进位,同时半加器不考虑来自低位的进位,因此最低位的相加可用半加器实现。

-

具体实现。最低位的相加用半加器实现,将最低位的两个数字作为半加器A,B的输入,产生本位S和向高位的进位C,然后将进位位C接入加法器作为Cin端的输入,再将本位的两个数字作为全加器A,B的输入,产生本位S和进位位Cout,同理每个加法器进位输入来自低位的进位输出,往后再接入两个全加器,最后输出最后一个全加器的进位位然后依次输出每个加法器的本位,即可得到两个四位二进制数相加的结果。

-

2.模拟两个四位二进制1010和0011的相加。

(1)最低位0,和1相加,产生的本位和为1,向高位的进位为0。

(2)接受来自低位的进位0和本位的1,1两数字相加,产生的本位和为0,向高位的进位为1。

(3)接受来自低位的进位1和本位的0,0两数字相加,产生的本位和为1,向高位的进位为0。

(4)接受来自低位的进位0和本位的1,0两数字相加,产生的本位和为1,向高位的进位为0。

(5)最后输出最后一个加法器,得到结果01101。

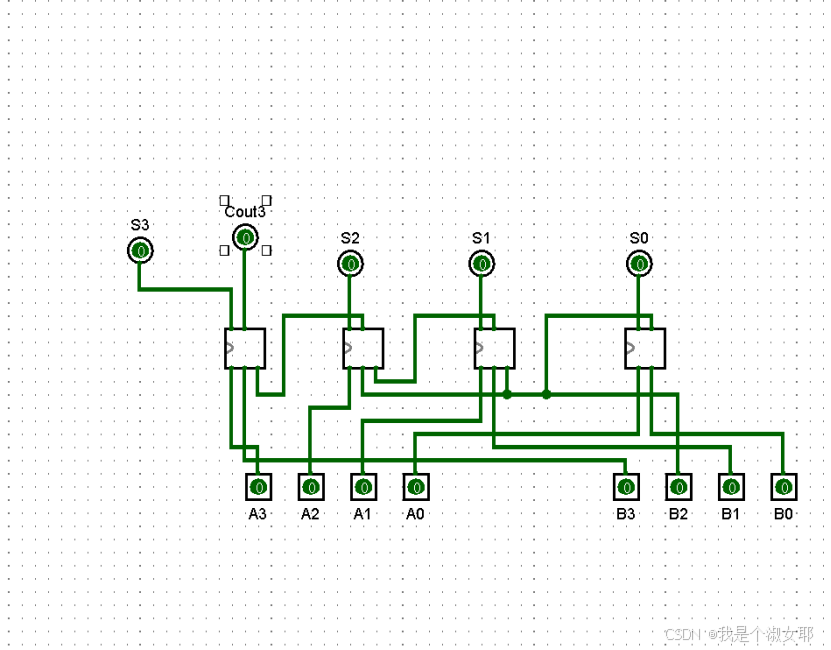

3.逻辑电路图:

图(p)四位二进制数相加的串行加法器

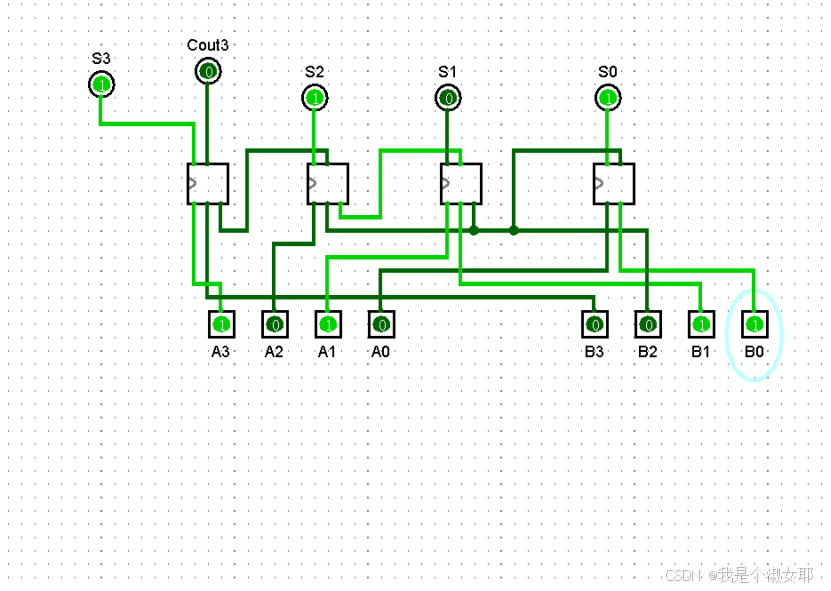

4..验证理论结果

图(t)两四位二进制1010和0011通过串行加法器相加的结果

5.结论:

由图(t)可知1010和0011通过串行加法器的相加结果为01100,与模拟的理论值相同,由此可知该串行加法器可实现两个四位二进制数的相加。

总结:

通过本次实验对半加器和全加器的原理有了更深入的理解,从原理分析到真正表再到仿真电路,让我能更好的了解到半加器和全加器的特点以及区别,半加器仅实现一位二进制的相加,全加器可以实现三位二进制相加,半加器不考虑低位进位以及全加器考虑低位进位这一特性设计了一个串行加法器可以实现四位二进制数的相加,由此可以知道通过串联全加器和半加器可以实现更多位二进制数的相加。

4790

4790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?