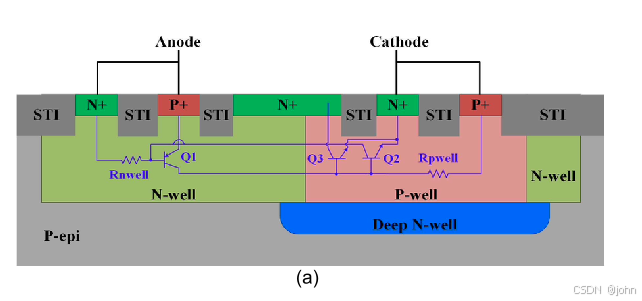

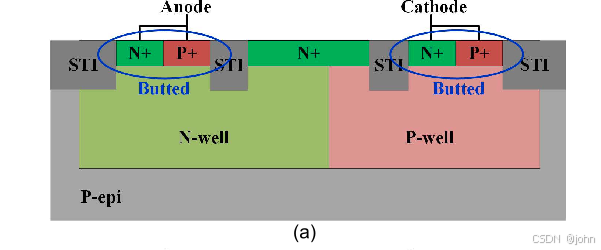

这是传统的MLSCR的结构,其中MLSCR和LSCR的不同在于器件中间有无N+区,并且其触发电压较LSCR要小。

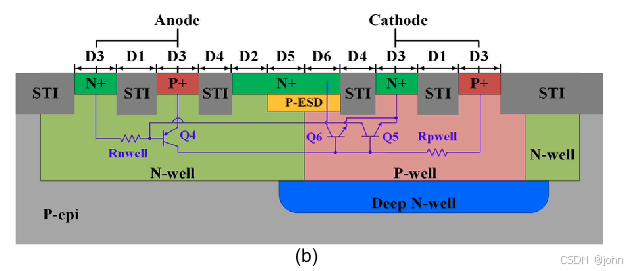

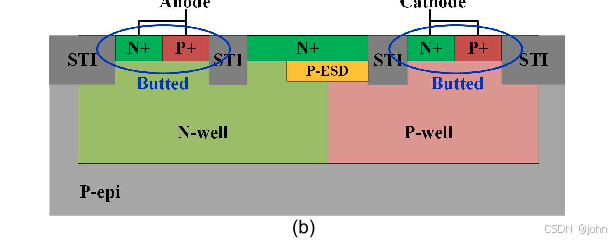

这是文章提出的MLSCR的改型,其明显不同在于在中间N+区下面加上了一层称为P-ESD的P型区域,由于P-ESD区域的掺杂浓度较P阱更大,于是这个器件的雪崩击穿电压要小于传统的MLSCR,从而其击穿电压更小。

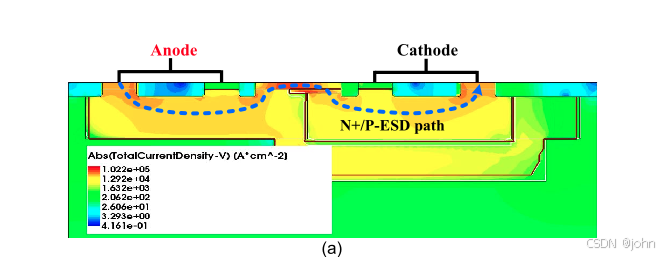

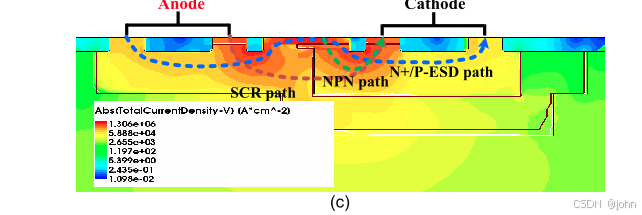

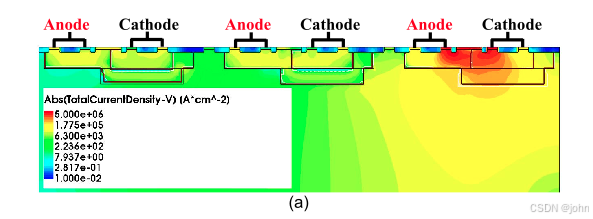

这是器件在反向PN结发生雪崩击穿时的内部电流分布,颜色和电流密度大小的关系可以按照左下的标识进行判断,可以发现N+/P-ESD结处的电流密度最大,这也是雪崩击穿发生的地方。

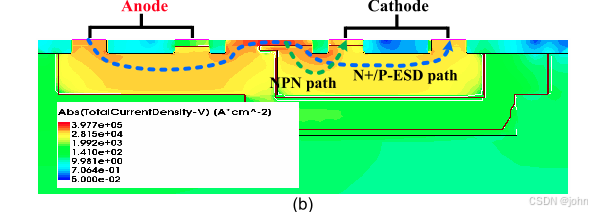

这是器件中寄生晶体管NPN开启时的电流分布,其电流流向由图中绿色箭头表示,而反偏二极管电流路径由蓝色箭头表示。

这是SCR路径开始后的电流密度分布,其中SCR路径由红色箭头表示。

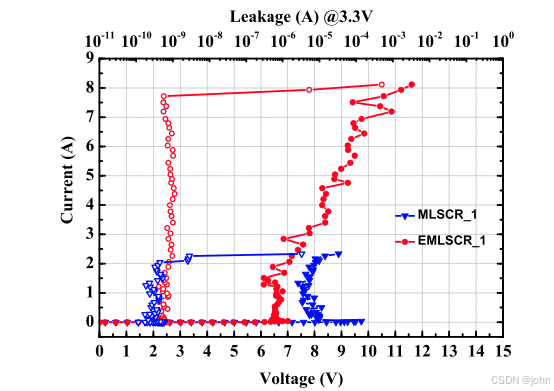

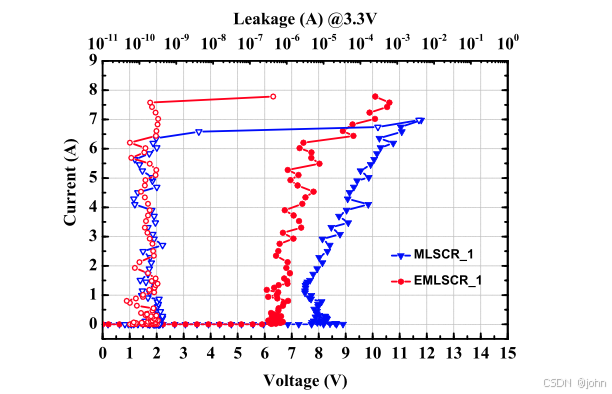

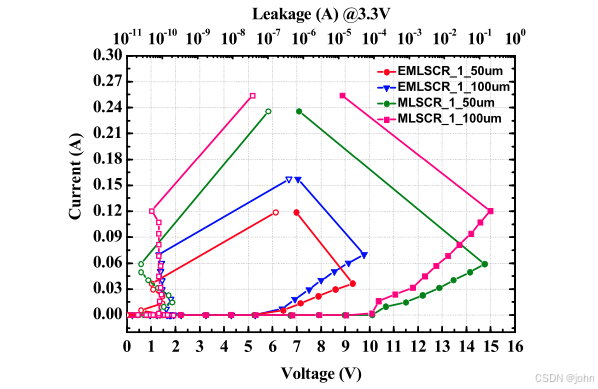

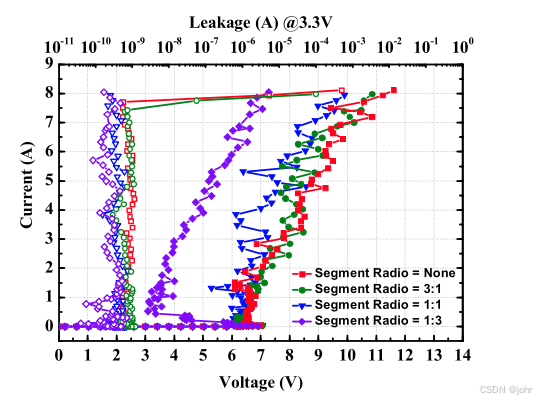

这是对MLSCR和EMLSCR器件进行TLP测试得到的IV曲线,可以看到EMLSCR器件的触发电压有了明显的下降,但是MLSCR的实效电流却出现反常,这个问题后面会涉及到。

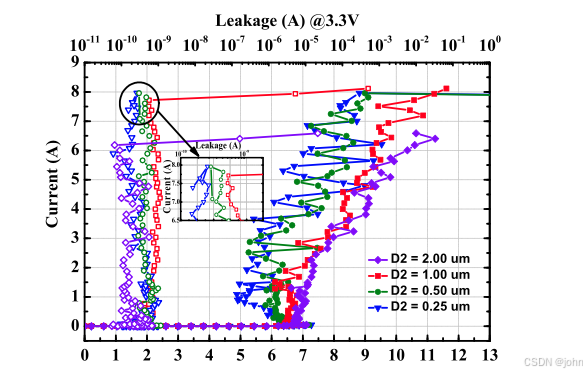

这是对器件的参数D2进行调整后对器件性能造成的影响,可以看到当D2逐渐减小时,其失效电流有所增加。

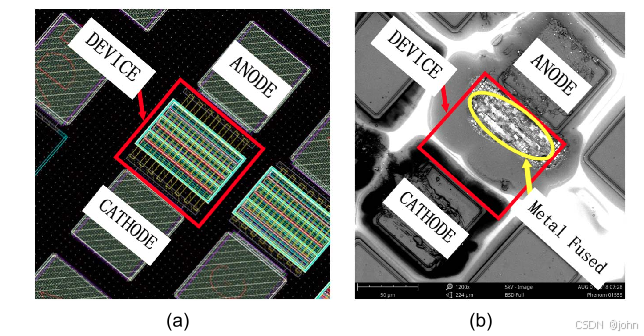

这张图是由于失效电流过大,将金属互连线熔断的图片,也说明了线宽的不足。

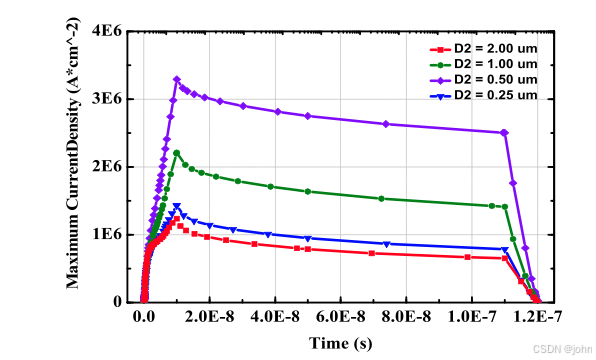

这是对不同D2的器件进行TLP模拟下的最大电流密度的对比,比较符合测试数据。

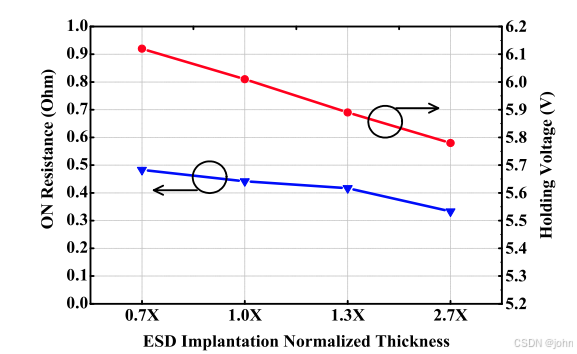

这是对P-ESD层的厚度进行调整后,测得的器件导通电阻和维持电压的变化情况,可以看到随着P-ESD层的厚度逐渐增大,其导通电阻和维持电压都有一定的下降。

这是使用改进的TLP测试方法下的MLSCR和EMLSCR器件的IV曲线,可以看到MLSCR器件的实效电流恢复正常了。这是因为原来器件被设计成了叉指结构,当TLP冲击来临时,会存在电流导通不均匀的问题,从而导致了仅有部分的SCR结构被开启,从而失效电流下降。而改进的TLP测试方法的波形有更小的上升时间,从而在单位时间内产生更多的能量,可以将能量平均地分布在不同的SCR结构中,从而实现大部分器件的开启。

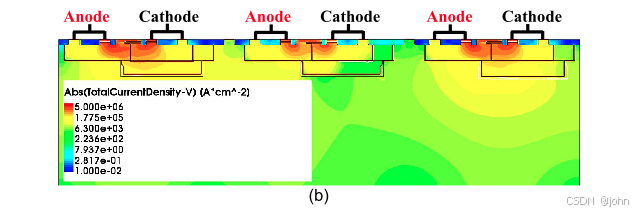

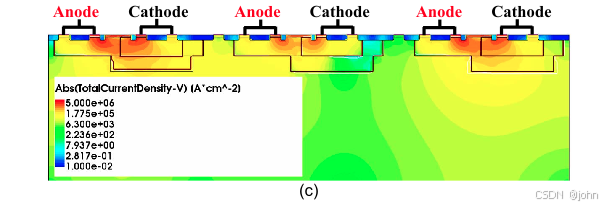

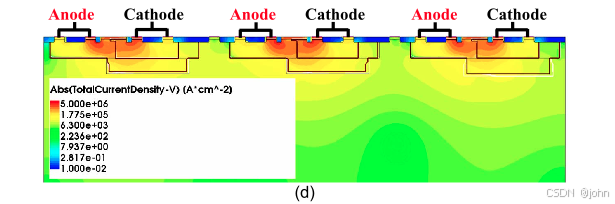

ab图分别是在传统TLP下两种器件的电流导通状态,cd图分别为改进TLP下两种器件的电流导通状态。

这是另一种应用于高压领域的结构,因为其有着更高的维持电压,能防止拴锁现象。

通过对于这种结构进行器件TLP测试,发现其失效电流过低。

如图所示不管是MLSCR还是EMLSCR,其失效电流都很低。其原因在于阱电阻过低,从而无法触发寄生晶体管的开启。

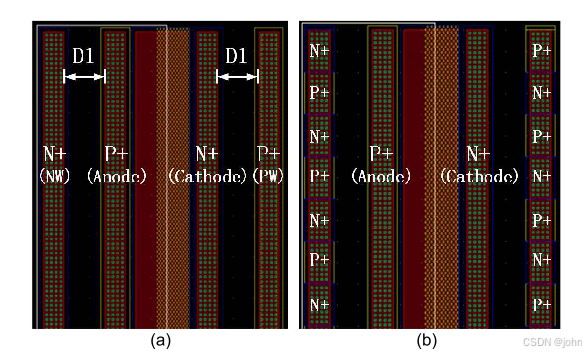

论文中提出了两种提高阱电阻的方法,其一是改变D1的长度,其二是改变器件的拓扑结构,改为交替式的N+和P+的分布。

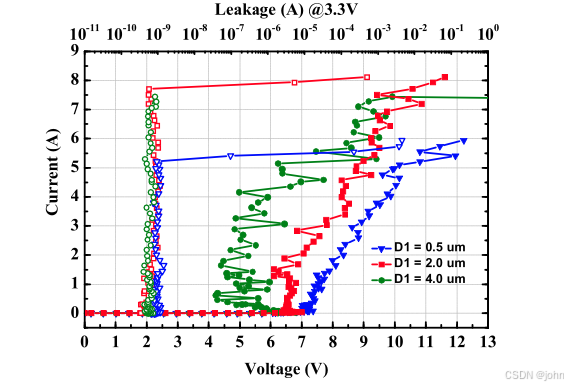

这是D1参数的不同对器件性能的影响。

这是拓扑结构中N+和P+占比对器件性能的影响。

总结:

这是一篇于2019年发表在IEEE TRANSACTIONS ON ELECTRON DEVICES上的文章,标题为An Enhanced MLSCR Structure Suitable for ESD Protection in Advanced Epitaxial CMOS Technology。文章的亮点在于提出了一种新的器件结构,用于提高SCR器件的ESD性能,其触发电压有明显的降低以及失效电流也有一定的提升。并通过实际制造的器件对器件的参数不同进行研究,得到参数对器件性能的影响。在这个过程中发现了器件的多叉指带来的电流导通不均匀问题,并利用改良的TLP测试对这个猜想进行验证。同时在对另一种结构的研究中发现了阱电阻过低的问题,并提出了改善阱电阻的方法,并利用测试对方法进行验证。总的来说,该文章为进一步探索更加合适当下ESD需求的SCR器件的结构做出了一定的贡献。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?