四路智力抢答器

1.电路设计前言

智力抢答器是在各类竞赛中经常用到的一种数字电路,使用抢答器可以快速精准地分辨出获得优先答题权的选手,搭配抢答计时、答题计时等功能可以有效把控竞赛的进行节奏。其电路构成中用到了触发器、缤码器、显示译码器等典型的数字电路单元,是对数字电路结构、逻辑等的综合运用。本文利用MLilisim软件,模仿真实应用场景,使用按键式开关进行抢答,完成对具备抢答计时和答题计时功能的4路智力抢答器电路的设计与仿真。

2.设计要求

电路设计需要围绕电路的功能考虑,所以在开始设计前,要明确本电路应具备的功能。

(1)主持人控制开关按下后,显示器清零,断开后开启抢答模式,抢答时长为20s,如果超时,本轮作废。

(2)每个选手对应一个按键开关,在抢答模式按下后抢答,抢到的选手号能直接在显示器上展示出来。

(3)一旦有选手抢到后,其他选手即使按下按钮也无法影响显示器上的数字显示。

(4)完成一轮抢答后,主持人开关按下,再次清零。

(5)在倒计时达到八秒时开始发出提示音

(6)每位成员有一个计分器,从预置的10分开始,由裁判控制是否加分或者减分。

为实现上述功能要求,将整个电路分为抢答电路主模块、抢答倒计时模块和和计分模块3个功能模块。进行分别设计在组合。

3.设计目的

掌握数字电路基本原理:

通过设计和实现抢答器电路,我们深入理解了数字电路的基本概念、原理和组成,特别是触发器、编码器、显示译码器等数字电路单元的功能和应用。

理解时序逻辑电路设计:

在抢答器的设计中,我们使用了时序逻辑电路,通过控制时钟信号和触发器的状态来实现抢答和计时的功能。这使我们掌握了时序逻辑电路的设计方法和原理。

熟悉电子仿真软件的使用:

通过利用Multisim等电子仿真软件,我们学会了如何使用这些工具进行电路设计和仿真,验证了电路设计的正确性,并了解了仿真软件在电子电路设计中的重要作用。

提升系统设计和综合应用能力:

智力抢答器的设计涉及到多个功能模块的整合,通过设计和组合各个模块,我们提升了系统设计和综合应用的能力,学会了如何根据功能需求进行系统整体设计和模块划分。

培养问题解决和创新能力:

在实验过程中,我们遇到了各种问题和挑战,如何有效地解决这些问题,以及如何通过创新来实现设计目标,锻炼了我们的问题解决能力和创新能力。

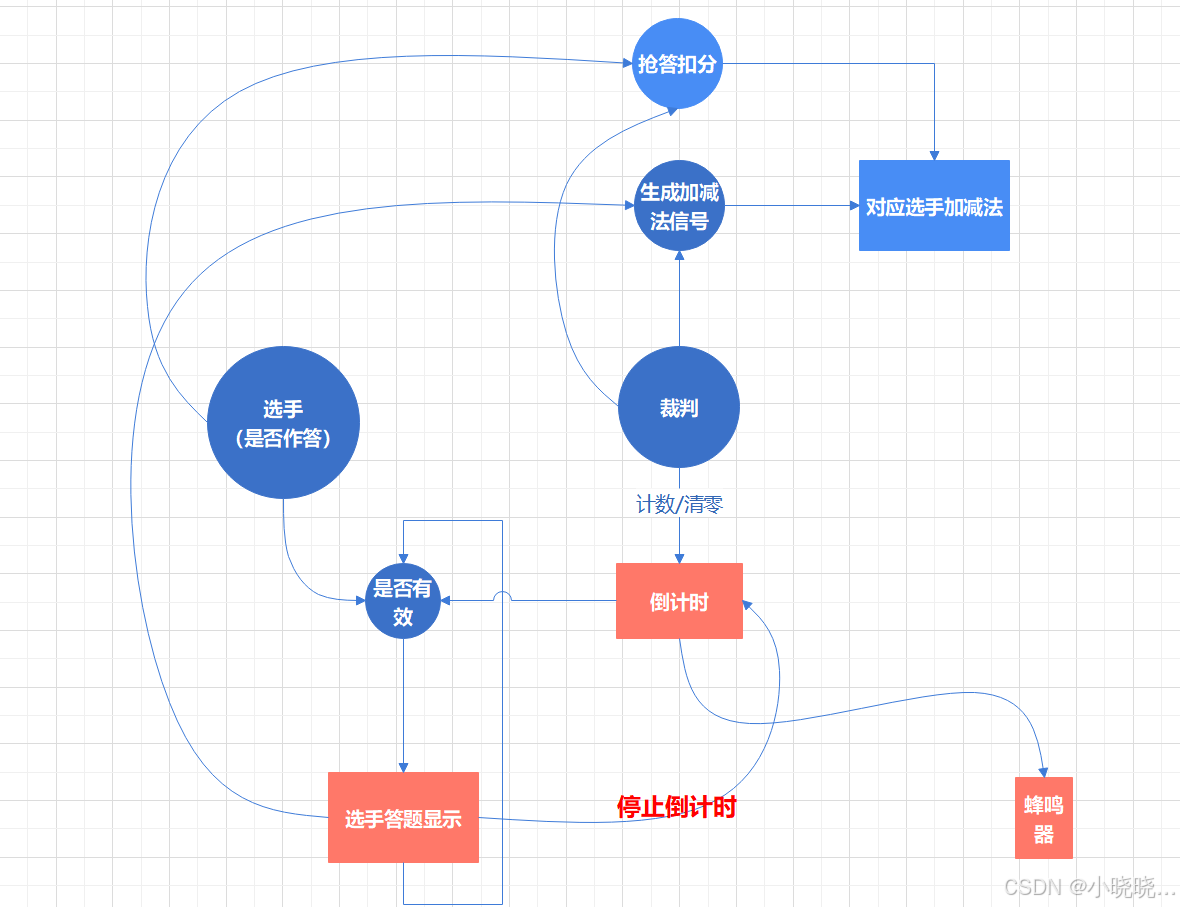

1.4设计思路

2.1抢答电路主模块

2.1设计思路

选手按下开关后,其他选手即使再按下开关也不会起作用,即只有最先抢到的选手信号被锁存,其他选手信号无法传输。基于这种考虑,在抢答电路主模块中,必须要有一个锁存器电路,实现信号锁存。

主模块电路中的核心结构是锁存器和编码器部分。本文以4个选手参赛的4路抢答器为例进行设计,选择了4输入D锁存器74LS175,和数码管进行显示所选选手 。当选手多于四位时,在4输入D锁存器74LS175后搭配优先编码器74LS148,显示译码芯片74LS48连接构成抢答电路主模块

74LS175芯片时钟上开沿触发,当时钟上升沿到来时,就可让D传递至Qi,而根据电路功能要求,一旦接收到任意一个信号后,其他信号就不能再传递,即当某一个Q接收到信号后,该芯片就应停止工作,拒绝接收其他信号,根据功能表可知,在CLK作用下,芯片就能接收信号,所以,当任意一个Q接收到信号后,就应能使CLK信号无法进入芯片时钟端。

这里可以通过一个组合逻辑来实现,。当按钮未按下时,所有Q均为0,所有的QN都是1,此时或非门U6输出为1,所以,U23输出的就是时钟信号CLK,此时,,所有的D信号部能传送到a端,而当某个选手按下按钮后,就产生了一个1信号,并在CLK的作用下,传送至相应的Q端,如2号选手按下按钮,2D=1,从而使唤2Q=1,此时或非门U6输出为0,从而导致与非门U3输出0,芯片CLK端接收到的就是0,而无法接收函数发生器提供的时钟信号,所以,芯片处于保持状态,无法传输其他数据。也就是2号选手产生的信号已被锁存在触发器中。

另外,为确保每轮结束后都重新开始,在抢答模块中还应设置一个主持人开关,连接到D锁存器的清零端,当主持人开关按下后,D锁存输出全部置为0,选手需要重新开始抢答。

2.2实现电路

3.1抢答倒计时模块

3.1要求分析

设置抢答倒计时模块是为了确保选手必须在规定时间内完成抢答,而不是无休止地准备,实现对竞赛过程的时间把控。本设计案例要求如下。

(1)主持人控制开关按下后,倒计时显示器显示9,开关断开后,开启抢答模式,倒计时显示器上开始倒计时。

(2)若20s内,没有选手抢答,则倒计时至0就停止。该轮结束,主持人需要重新按下控制开关,清零后再次开始。

(3)若20s内,有选手抢答,则在选手抢到的同时,计时就停止。待选手答题完成后,主持人需要重新按下控制开关,清零后再次开始。

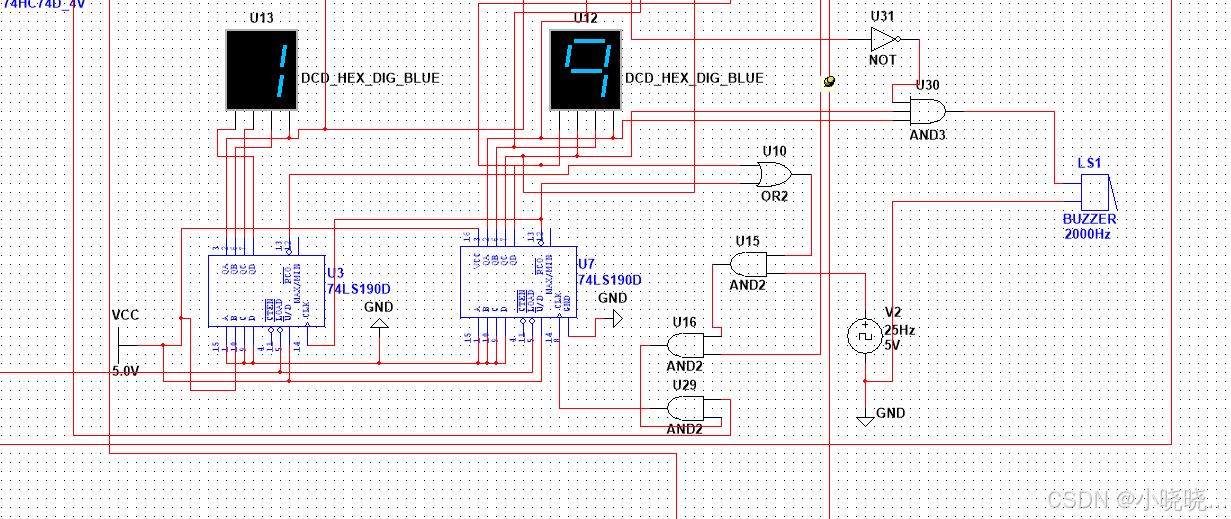

实现倒计时功能,需减法计数功能的计数器芯片,本设计中选择可逆计数器74LS190,要想该芯片从20开始倒计时,在正式开始前,主持人应该按下开关,让芯片置20,同时74ls190芯片U/D端口接1进行减法计数。的当主持人宣布抢答开始时,再次按下开关,芯片即进入倒计时模式。这里考虑到主持人开关使用的是按钮开关,故利用D触发器实现信号翻转功能,当主持人按一次按钮开关时实现置数,再按一次开关开始倒计时。

若20s内无选手抢答,则倒计时至0应该停止,即不能让计数器重新回到99继续倒计时。根据74LS190的功能手册,要进行倒计时,应将时钟信号加至CPD端口,同时U/D端口接高电平,LD和CT端口分别接低电平和高电平。所以如果想让计数停止,可以利用芯片的倒计时时钟端CPD,当计数倒数至0后,产生停止计数信号,阻止时钟信号进入CPD,本设计中采用与门来实现时钟信号封锁的功能。停止计数的信号可以由计数器的Q输出端实现,当计数置0时,4个输出都为O,封锁时钟信号控制与门,或者也可以利用该芯片的借位输出端。根据芯片手册可知,当芯片倒数至0时,借位输出端产生低电平,同样可以满足功能要求。此外,若有选手抢答,不论此时倒计时是什么数字,都必须立刻停止。即当有任一选手抢答时,应将抢答信号同时传递至抢答倒计时模块,使唤时钟信号控制与门输出为0,实现封锁时钟信号,停止计数的效果。

3.2实现电路

4.1计分模块

4.2要求分析

智力抢答计分模块是为了更好的进行排名和直观的展现选手的实力水平,加分减分最后由裁判决定所以由一对多进行操作,加分减分可以由74ls190芯片进行实现,将74ls190芯片中的U/D分别接1或者0即可实现,加分和减分的目的,具体要求如下:

- 一个按钮控制加分,一个按钮控制减分,并且每个按钮控制4个参赛选手。

- 四名参加选手的初始分数为10分。

- 当有选手在未倒计时时进行抢答,则扣1 分。

计分74ls190的cp时钟端口接的入按钮的两段或门这样实现,每按一次按钮就会有一个计分的脉冲传递到74ls190进行加减分

要实现两个按钮分别对应0和1控制74ls190的加减法,当按钮未触发时,初始给按钮接0.并且分别接入jk触发器中,这样当按钮未触发时按钮一直保持上一个状态即封锁了上一个状态,当连接j端口的按钮触发时,此时jk触发器输出1,并且锁定。直到连接k端口的按钮被触发才会转到0。

4.3问题与解决方法

问题1:但是转化加分,加分模式的信号进过jk触发器会比进行加分减分的信号慢到U/D端口,这样当进行加分减分转化模式时会进行上个模式的

解决:在脉冲信号加一个D寄存器调整脉冲到达cp端口时间

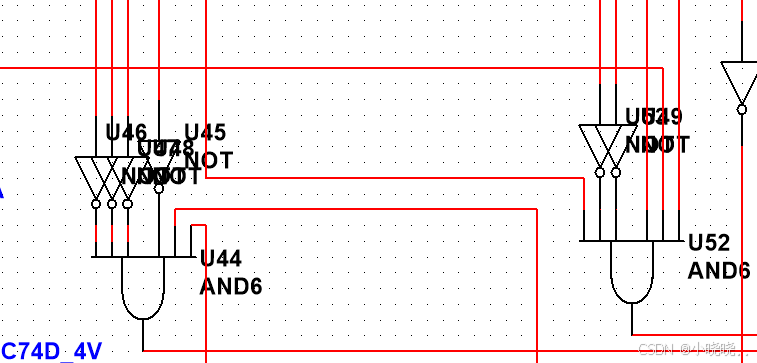

问题二:因为计分是十进制中的两位,十位的加减需要个位进行判断。

解决:根据分析当个位变0,且加减模式为加法,这样可以判断为十位应当加1当个位为9且加减模式为减分,此时十位应当减1.但是74ls190判断的是当前即Qn时刻的状态)(因为有时钟的影响此时判断会将Qn和Qn+1一起判断时刻),但是设计思路中判断的是Qn+1的状态。此时在在十位74ls190芯片的cp端口连接一个D触发器控制当判断时,个位已处于Qn状态。

4.4判断电路

3228

3228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?