【设计目的与主要内容】一、双极型晶体管工艺流程设计 目的: 1.学会根据工艺和电学参数要求设计双极型晶体管结构(有埋层) 2.学习设计一个双极型晶体管的工艺流程 3.学会使用TCAD实现所设计的双极型晶体 要求:

输出;

二、双极型晶体管性能仿真分析 目的: 学会使用器件仿真软件仿真双极型晶体管的电学特性曲线和提取电学参数。

要求:

|

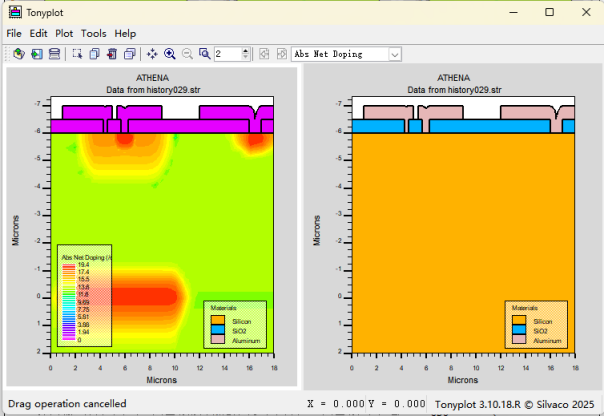

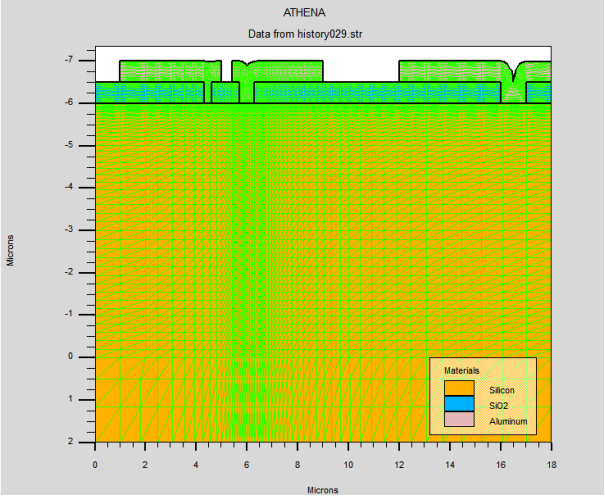

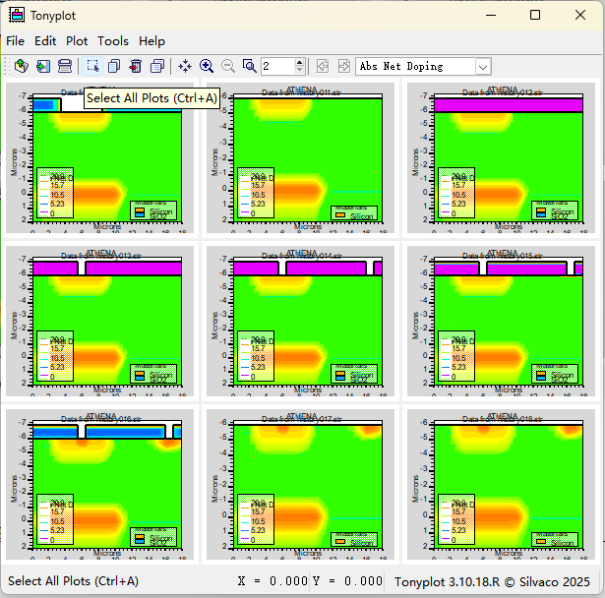

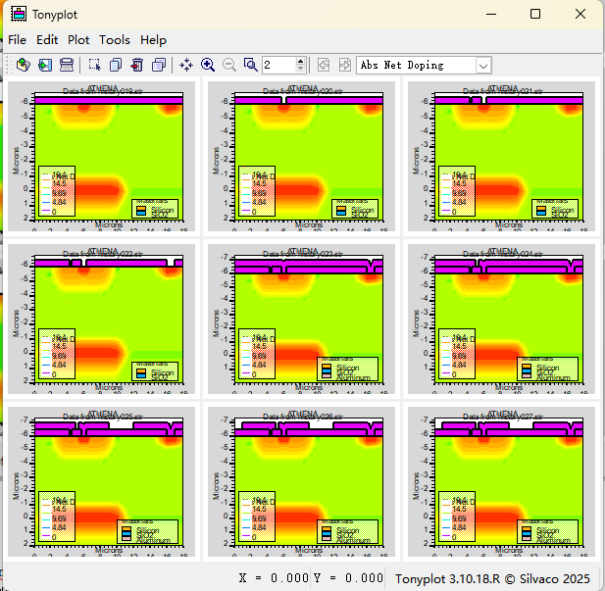

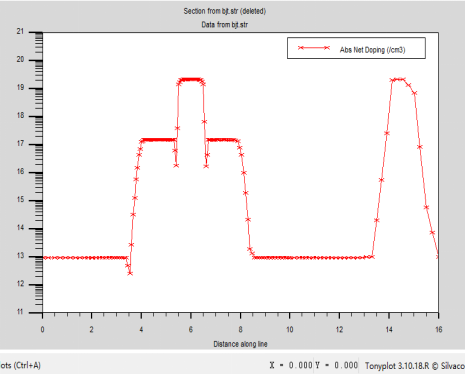

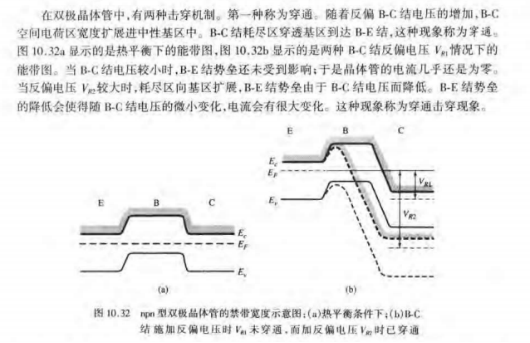

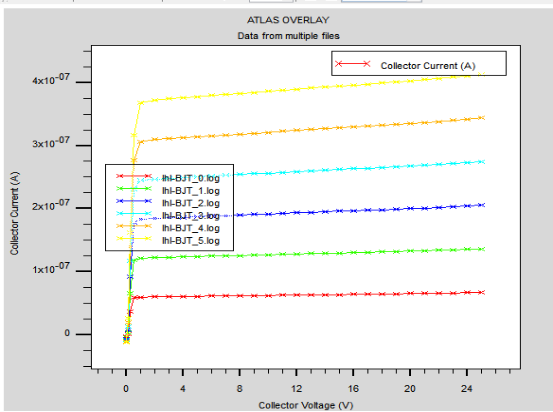

【器件结构、设计原理及设计流程】总设计流程 一、使用athena构建一个含有N+埋层的npn双极性晶体管 二、仿真输出特性曲线(共基极接法,能体现击穿特性)共基极击穿电压 (尽量接近) 三、仿真输出特性曲线(共发射极接法,考察基区宽度调制效应)共基极直流电流短路增益β>=30 四、仿真输出放大工作状态时,双极型晶体管的电势电场分布,及能带。 最终得到的器件结构(显示掺杂与不显示掺杂) 结构分析:基本工艺:采用高阻p型硅作为衬底,在表面热生长一层厚氧化层(0.5~1um)并在其上面开窗口,进行高浓度的n型杂质(通常使用扩散系数小的砷或锑作为杂质以尽量减小外延生长以及其后各种高温过程引起的杂质再分布)扩散,形成n+理层。埋层的主要目的是在集电区和上端的集电极接触之间形成低阻通道,以减小集电极串联电阻。接着在埋层上外延生长低浓度的n型层,外延层的厚度和掺杂浓度是决定晶体管耐压和结电容等器件性能的重要参数。经常是通过硅的局部氧化(LocalOxidationofSilicon,简称LOCOS)工艺形成SiO2墙,使之与n+理层相接来实现。横向氧化物隔离不仅可以缩小器件尺寸,而且能减小寄生电容,这是因为SiO2的相对介电常数为3.9,比Si的11.7小。 器件结构设计流程及每一步输出器件结构和对应的原理 在deckbuild-preference-history中勾选Athena,可以保存每一步工艺后得到的结构文件。关键工艺输出的结果如下: 一、网格划分 设计原理 ①line x loc=0.00 spac=1语句中location表示网格划线的位置,space表示相邻两次划线之间的距离。 ②器件的EBC结分布在x=6周围,代码在结处网格做了加密处理。 ③需要注意的是网格划分的space应该是后续刻蚀外延等工艺的公因数,不然由于该处网格精度不够刻蚀的结果会和定义的有偏差。 ④网格定义之后通过init silicon c.boron=1.0e13 orientation=100 two.d,初始化二维衬底。

二、制作埋氧化层: 设计原理 ①在athena仿真中不需要实际工艺中的涂胶光刻等步骤,淀积sio2刻蚀就可以充当掩膜,再使用etch语句刻蚀出需要掺杂的窗口。 ②掺杂有两种方式,第一种是扩散,time,temp参数分别表示扩散的时间和温度,时间和温度越久,扩散形成的结也越大,boron=9e17表示掺杂的元素是硼浓度是9e17(单位 );另一种是离子注入,dose表示掺杂浓度(单位 ③靠后的工艺尽量少用扩散以免对前面的掺杂造成影响。 ④epitaxy定义外延,可以定义外延的衬底和掺杂,以及外延层中的网格密度。 三、制作三极管基区,发射区 设计原理 ①上面提到外延层中可以重新定义y方向的网格密度,增加取点,由于一次外延只能加密一处网格,这里外延的6um分两次进行,第一次加密n+埋层和衬底接触部分目的是为了后面cutline图像坡度在此处更清晰,第二次在ydy=0.2也就是基区周围进行加密。这样只有关键位置网格精细,其他位置粗糙避免了不必要的计算。 ②然后分别淀积-刻蚀-掺杂,制作基区和发射结,以及集电极与电极接触部分的欧姆接触。

四、淀积al,制作电极(颜色偏黄可能是tonyplot软件问题) ①etch 在sio2上刻蚀出电极接口 ②再通过deposit alumin thick =0.5淀积2um厚度的al ③再次etch将各个电极独立分开 ④electrode name =emitter x=6 y=-6.2定义电极位置,名称,参数的xy指到了一块金属,Athena就会把指到的这整块金属定义成电极。

五、电学仿真 (1)仿真共基极击穿特性

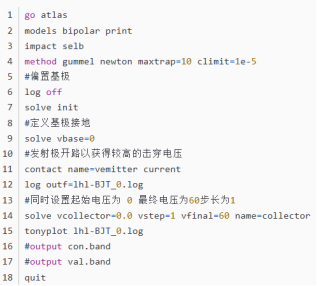

仿真击穿特性曲线步骤: (解之前可以通过initfile导入结构文件) ①器件结构开始要定义使用的模型,点开command看到这些模型包括迁移率模型,复合模型,态密度模型,碰撞电离模型,隧穿模型,能量输运模型等等,不同的模型对应不同的计算公式,考虑或不考虑某些非理想因素等等,这些公式在atlas用户手册第三章有详细记载,这里使用系统自带的bjt模型。 ②击穿特性曲线也就是BC结发生雪崩击穿,强电场下载流子和晶格原子碰撞还需要引入碰撞电离模型。 ③定义数值求解,有gummel,block,newton三种,一般使用牛顿迭代法,通过不断带入计算结果得到逼近的解值。 ④solve init后给每个电极加电压,因为共基极解法,这里给基极接地。Contact通过定义发射极电流控制定义发射极开路,这样避免了发射极电压的叠加可以获得更高的击穿电压。定义电极开路还可以接一大电阻或者从结构文件中删去该电极。 ⑤定义好各个电极电压之后,开始解电压。Log outfile设置将解的结果保存在命名的.log文件里。solve vcollector=0.0 vstep=1 vfinal=60 name=collector设置集电极起始电压为 0 最终电压为60步长为1 。 ⑥quit退出atlas

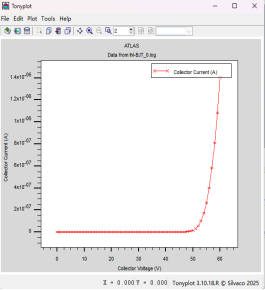

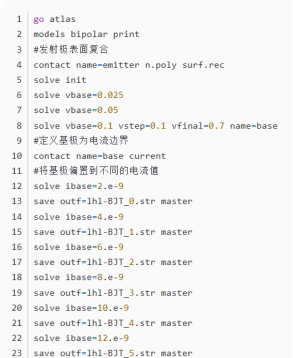

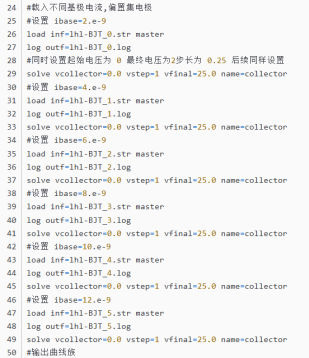

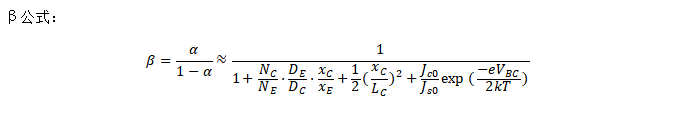

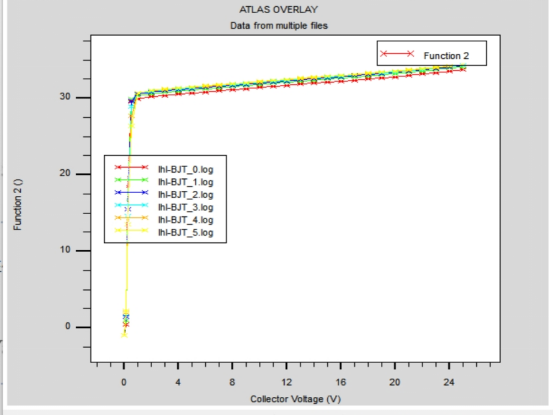

仿真共射极输出特性曲线步骤: ①定义模型BJTmodel,定义数值求解 ②solve init开始解,将基极偏置到0.7v,直接从一个初始状态跳到大电压值可能导致求解器无法收敛,先解两个步进小的电压。然后将基极定义为电流控制。方便观察IC随IB的变化,IC=βIB。 ③将基极偏置到不同的电流值,即对应六条不同曲线,保存到.master文件里。 ④分别打开上面保存的.master文件,在不同的IB下解出出IC-VC曲线,保存曲线。solve vcollector=0.0 vstep=1 vfinal=25.0 name=collector。vcollector=0.0 设置起始电压为 0 , vfinal=25.0设置最终电压为25,vstep=1设置步长为 1 ,name=collecto设置电极名称。log outf=lhl-BJT_0.log设置分别保存在lhl-BJT_5.log的log文件里。 ⑤用tonyplot的overlay功能把这些曲线显示在一张图上,最后得到下面的曲线族 六、保存放大工作状态下的结构文件 deckbuild输出的str文件在Tonyplot-Display-contours中能显示的量有下面三个层次①solve init之前保存的str文件,只能显示少量参数。②solve init之后输出的str文件可以保存更多参数。③solve init后生成的结构文件,保存的contours仍然有限,使用output语句可以指定更多的量储存在.str文件中。 使用solve ibase=1.e-8 solve vcollector=2将电极偏置到放大模式的工作状态,保存此时的结构文件。 |

【器件仿真数据与分析】

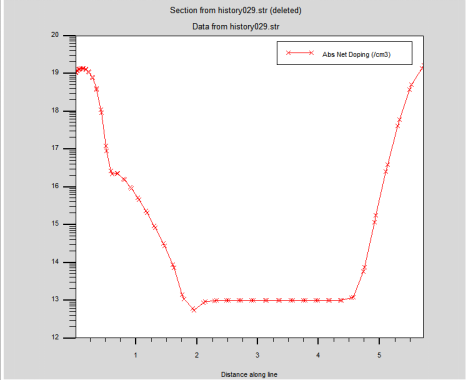

A基区掺杂浓度峰值1016 ~1017cm-3 B发射区掺杂浓度峰值约

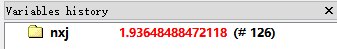

使用extract name ="nxj" xj silicon mat.occno =1 x.val=6 junc.occno=2一句可以提取BC结结深。参数 x.val=6表示在x=6处从上往下, junc.occno=2表示提取从上往下数第二个结的结深。提取到的结深如下:

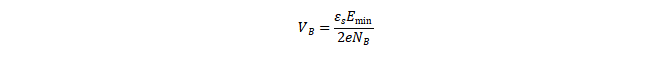

三、共基极击穿特性曲线曲线,以及击穿电 根据半导体器件物理中雪崩击穿电压公式: 其中 另外,理论上IC-VC曲线在击穿前斜率都几乎是0,如果IC-VC曲线一开始斜率就很大,可能是EB结发生了穿通击穿。这主要是基区宽度太小导致的,可能是发射结注入过深了。

得到上面的输出特性曲线和电流增益经过了调校,最初的输出特性曲线只有在低电压的时候有理想输出特性曲线的样子,电压加大之后工作区斜率很大β很小。 ①增大电流增益β 基极电流IB会影响电流增益的值,器件结构如果没有问题,β达不到要求,就可能是因为大注入效应/复合效应的影响。调节解的IB到合适区间范围内就能得到100-200的β值。 ②减小基区宽度调制 增大基区和集电区掺杂可以减小基区宽度调制,曲线更接近理想情况。首先BC结耗尽区宽度随掺杂增大降低,对基区的调制作用减小,曲线在放大区一段更加平缓;EB结由于内建电势差V正比于ln(NBNC),增大NBNC,集电区寄生串联电阻下降,基区电阻降低,电流集边效应会弱,同时增大了BC结内建电势差,器件更容易进入工作区(BC结更容易反偏),曲线在饱和区一段更加陡峭,但发射极和集电极掺杂浓度之比减小,β也会减小,折中分析得到上面的曲线,β恰好满足要求(课设要求β>30) 基区宽度调制 做输出特性曲线的反向延长线,与vc轴负半轴交于一点,交点坐标绝对值就是厄利电压: 理想情况下输出特性曲线默认中性基区宽度 xb 为恒定值。然而,实际上基区宽度是 B - C 结电压的函数,因为随着电压的变化,B - C 结空间电荷区会扩展进基区。随着 B - C 结反偏电压的增加,B - C 结空间电荷区宽度增加,使得 xb减小。中性基区宽度的变化使得集电极电流发生变化。这种效应称为基区宽度调制效应;又称为厄利(Early)效应。理想情况下,集电极电流与B - C结电压无关,所以曲线斜率为零;于是晶体管的输出电导为零。然而,基区宽度调制效应,或是厄利效应,使曲线斜率和输出电导不为零。如果集电极电流特性曲线反向延长使集电极电流为零,那么曲线与电压轴相交于一点,该点被定义为厄利电压。它是描述晶体管特性时的一个共有参数。厄尔利电压的典型值在100~300V之间。 反向延长线计算得到输出特性曲线中厄利电压值在200v左右。

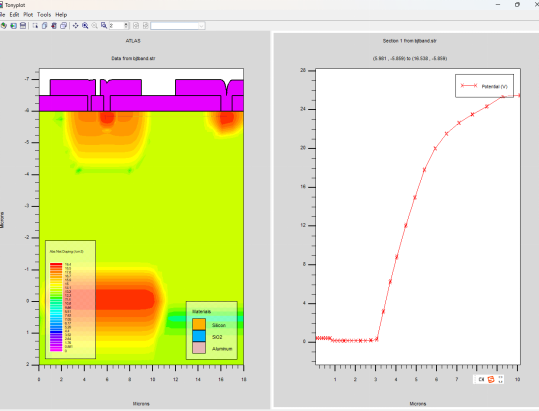

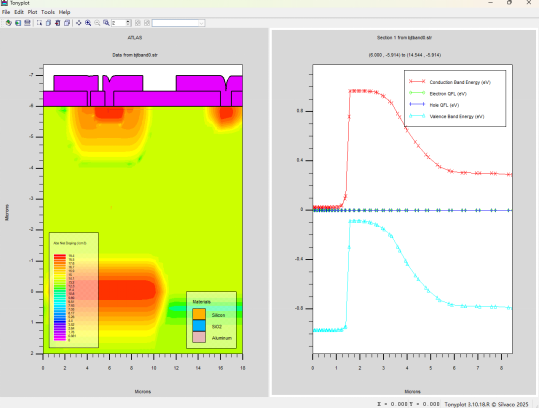

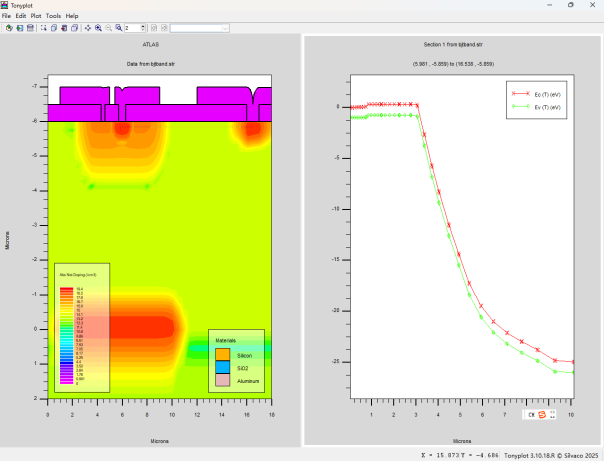

四、电势电场分布,及能带 输出的电场电势、能带如下:

图①是电场分布,理论上,在未加电压之前,Cutline field 后应观察到①②两处电场尖峰,第一处是由于发射区基区的n+p结,由于掺杂浓度大,泊松方程求电势一阶导后场强更大,斜率也更大,方向沿Y轴正方向;第二处是由于基区和集电区的pn结,由于基区和集电区掺杂浓度都不是很高,所以电场强度更低,斜率也更小,方向沿Y轴负方向。 加正向偏压后Vce=20v,远远大于由于p型半导体和n型半导体费米能级差形成的一两个电子伏特的空间电荷区势垒,这时候看到BC结电场峰值远远大于EC结,势垒高度、电势差也远远大于EB结电场峰值出现在两个冶金结处。但EB结耗尽区宽度应小于BC结,这是由于耗尽区宽度xd与掺杂浓度成反比,与反向电压和内建电势差之和成正比。 图②是电势分布,电势是泊松方程求两次积分,与下图电子能带图符号相反,趋势相同,正向偏压后Vce=25v,远远大于由于p型半导体和n型半导体费米能级差形成的一两个电子伏特的空间电荷区势垒,EB结在加正电压后内建电势差降低,BC结加反向电压后内建电势差升高,由于发射结和集电结本身就有ln(NE/NC)的内建电势差,即使加上偏压,集电结电势差仍旧很大。 图③是平衡时刻能带图,包括电子空穴费米能级,平衡时刻,电子准费米能级和空穴准费米能级相等,集电极重掺杂,费米能级进入了导带,所以可在前面的bjt模型之后中引入fermi stastic。 图④是工作在放大状态时能带图,加正向偏压以后,EB结正偏,势垒高度降低,BC结反偏势垒高度增大,而且通过能带图可以看到,电压大部分降落在BC结上,这是由于BC结耗尽宽度大于BE结耗尽区宽度,由于耗尽区相较于pn结两侧的中性区载流子浓度很小,电阻很大,承受了大部分电压,而且由于发射极重掺杂,EB结耗尽区中的载流子浓度也比BC结多得多,这样使得EC结耗尽区在单位电压下得到的电流也比BC结大,发射区的电子通过发射极注入到基区渡越基区之后像滑滑梯一样从集电区下来。

代码

|

(尽量接近)

(尽量接近)

),energy表示离子注入的能量,能量越大离子注入的越深, gauss tilt=0 rotation=0表示离子注入的角度和注入机的转速, tilt=7可以减小沟道效应。

),energy表示离子注入的能量,能量越大离子注入的越深, gauss tilt=0 rotation=0表示离子注入的角度和注入机的转速, tilt=7可以减小沟道效应。

Nd和NB都可以指pn结轻掺杂一侧的掺杂浓度,因此得到BC结的结深越大,得到的击穿电压也就越大。

Nd和NB都可以指pn结轻掺杂一侧的掺杂浓度,因此得到BC结的结深越大,得到的击穿电压也就越大。

在tonyplot-display-function中定义function2是collector current / base current,再在display中将y轴变量更改为定义的function2。得到的输出特性曲线以及β见下图。

在tonyplot-display-function中定义function2是collector current / base current,再在display中将y轴变量更改为定义的function2。得到的输出特性曲线以及β见下图。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?