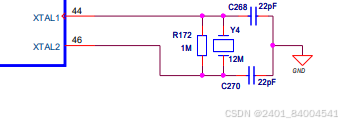

1、有源和无源晶振

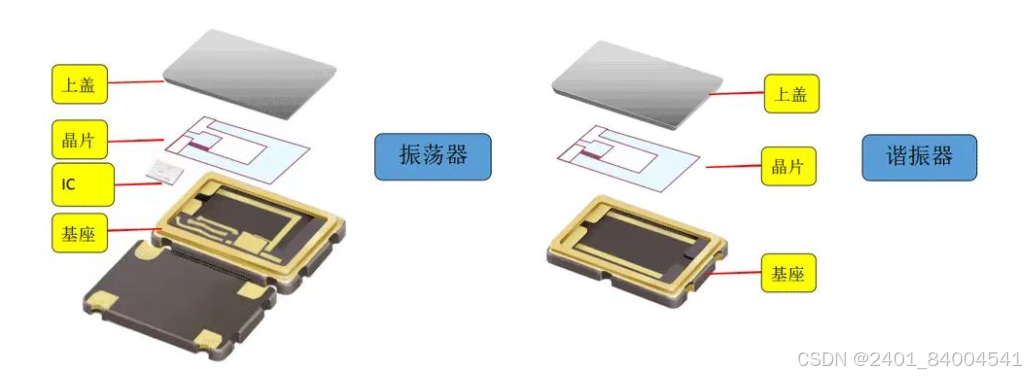

1.1 无源晶振与有源晶振内部构造对比:

无源晶振,英文为Crystal,中文全称为石英晶体谐振器(图右),而有源晶振英文则叫做Oscillator,中文全称为石英晶体振荡器(图左)。

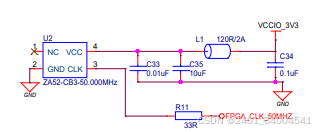

1.2 无源晶振与有源晶振应用电路对比:

左边为有源晶振电路,右为无源晶振电路。

1.3 无源晶振与有源晶振区tips:

1、2个引脚为无源晶振

2、4个引脚以上为有源晶振

3、4个引脚外形无法区分有源和无源晶振,但可通过应用电路来判断,需要外接电源为有源晶振(上图所示),有源晶振需外接电源直接输出CLK时钟信号;无源晶振不需电源,但需要注意匹配合适的负载电容CL。

需要注意的是无源晶振在电路设计中无方向性,有源晶振的引脚有方向,方向不对会损坏晶振。

有源晶振的应用电路外接电源除3.3V,还可接1.8、2.8、5V等,具体使用情况要看晶振的手册。

1.4 无源晶振负载电容(CL)与匹配电容(C1、C2)计算:

1. 负载电容(CL)是什么?

负载电容(CL)是指晶振在工作时看到的等效电容,决定了晶振的共振频率。通常由晶振厂家给出,比如 CL = 12pF。

2. 匹配电容(C1、C2)是什么?

匹配电容(C1、C2)是振荡电路中接到晶振两端(XTAL1 和 XTAL2)并对地的电容,用于调整负载电容,确保晶振工作在指定频率。

3.计算匹配电容(C1、C2)

C1 和 C2 不是直接等于 CL,而是与电路的寄生电容(Cp)有关:

CL=

C1 = C2 =

- CL:晶振的负载电容(由晶振厂家提供,如 12pF)。

- Cp:PCB 走线、封装焊盘、IC 输入端的寄生电容(通常 3pF~5pF)。

- C1、C2:匹配电容,需要计算后选择合适的标准值。

示例 :STM32 单片机使用 8MHz 晶振

- 晶振参数:8MHz, CL = 12pF

- PCB 及 MCU 寄生电容:假设 Cp ≈ 5pF

- 计算 C1 和 C2: C1=C2=2*(12pF−5pF)=14pF

- 选择电容:使用标准值 15pF(最接近计算值)

2、晶振震荡模式

震荡模式主要有基频(Fundamental)和泛音(Harmonic)两种:

2.1 基频模式(Fundamental Mode)

定义:晶振以其物理结构的固有频率振荡。

适用频率范围:一般用于低频晶振(如 1MHz~30MHz)。

为什么选基频模式?

MCU 通常使用 1MHz~50MHz 以内的晶振,且电路设计一般以基频模式运行,保证稳定性和兼容性。

2.2 泛音模式(Harmonic Mode)

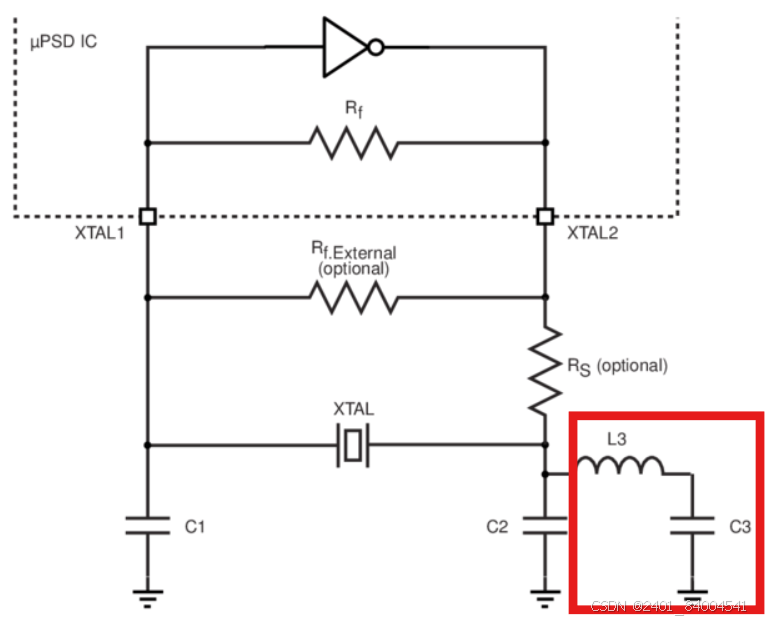

定义:晶振工作在基频的高次谐波(如 3 倍、5 倍、7 倍等)。一般晶振资料不会注明Harmonic Mode,一般情况下,在高频应用(>50MHz),通常采用三次或五次泛音晶振,并用 LC 电路确保正确工作。

适用频率范围:适用于高频晶振(如 50MHz 以上)。

为什么选泛音模式?

直接制造 90MHz 的基频晶振难度高、成本高,利用 30MHz 晶振的三次泛音(90MHz)可以降低成本,同时提高可制造性。

需要注意泛音和基频不能通用,基频需要接入适当的电容就可以工作,而泛音晶体则需要电感与电容配合使用才可振出泛音频率。如果没有额外的电路选择正确的泛音模式,晶振会默认工作在基频

计算方法:

- 选定目标泛音频率 fn

- 计算 LC 回路的谐振频率:

例子:

- 选择合适的电感 L 和电容 C,使其谐振在 100MHz。(如 100MHz 的 3 次泛音,基频是 33.33MHz)。

- 例如,如果 L = 10nH,那么 C 约为 2.53pF: fn=≈

100MHz

3、晶振输出模式(Frequency Output Mode)

无源晶振无输出驱动能力,仅提供振荡元件,所以不分输出模式;有源晶振内部集成振荡电路,直接输出时钟信号,分以下几种:

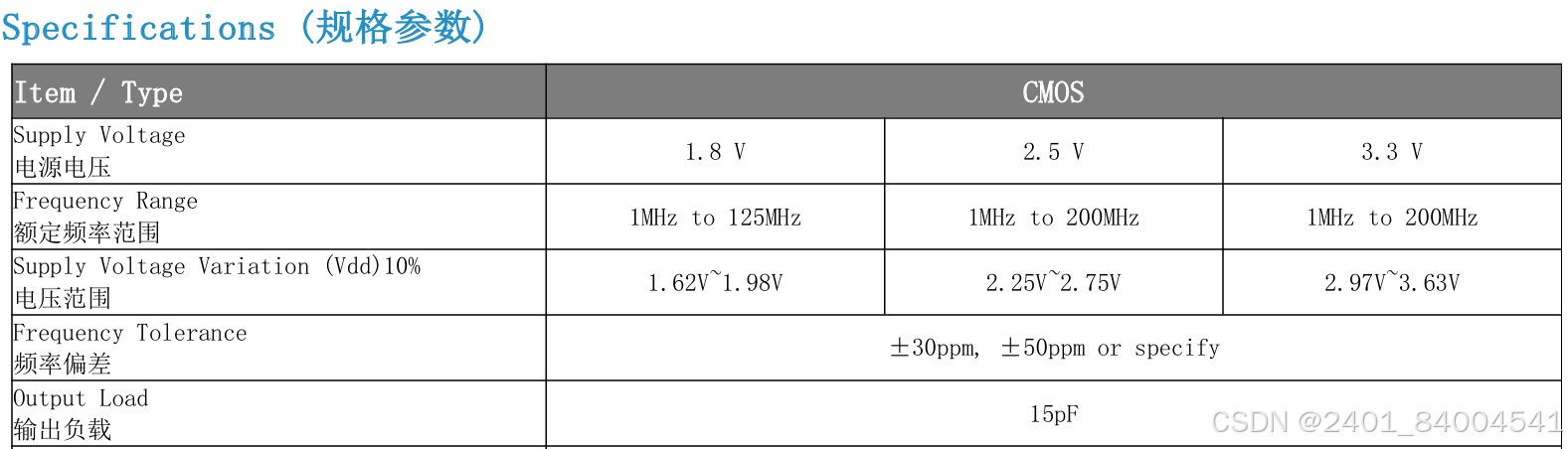

① CMOS 输出

特点:方波输出,适合大多数数字电路。

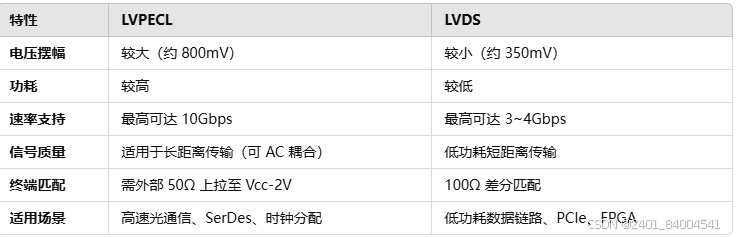

② LVPECL(低压正射极耦合逻辑)

特点:适用于高速数据通信(如光通信)。

应用场景

1、光通信:SONET/SDH、光模块(SFP、QSFP)

2、SerDes(串行器/解串器):千兆以太网(GbE)、光纤信号处理

3、高性能计算(HPC):超级计算机、服务器

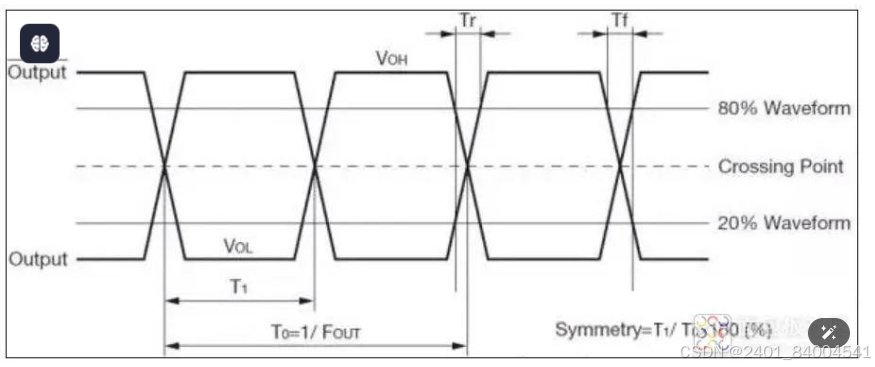

③ LVDS(低压差分信号)

特点:功耗低,适用于高频数据通信,如 PCIe、SerDes。

应用场景

1、FPGA/ASIC 设计:FPGA 时钟、SerDes 数据通道

2、PCIe 总线:PCIe 3.0/4.0 时钟

3、显示接口(LVDS 屏幕):LVDS 信号摆幅小、EMI 低,适合笔记本、工业 LCD 显示接口。

LVPECL(低压正射极耦合逻辑)和 LVDS(低压差分信号)都是高速差分信号输出模式的晶振,它们的主要区别在于功耗、信号摆幅和适用场景。

优先 LVDS: 如果你关注低功耗、短距离传输(如 FPGA、PCIe)。

优先 LVPECL: 如果你需要高速、长距离传输(如光通信、SerDes)。

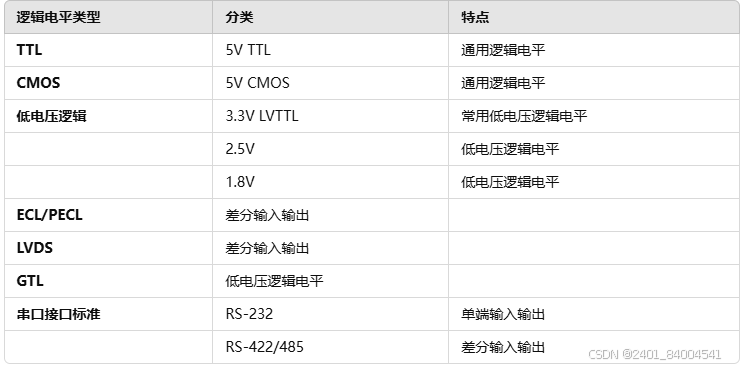

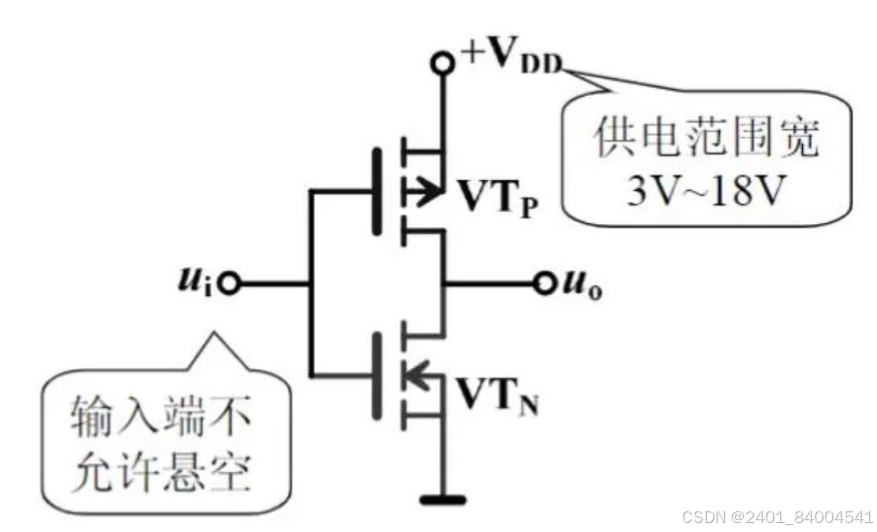

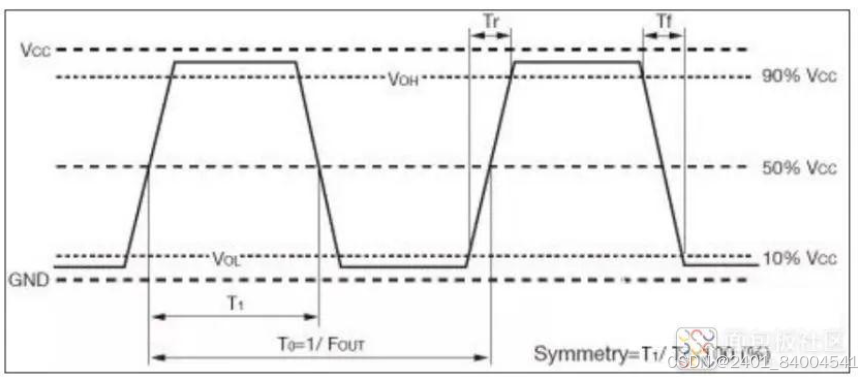

④逻辑电平说明

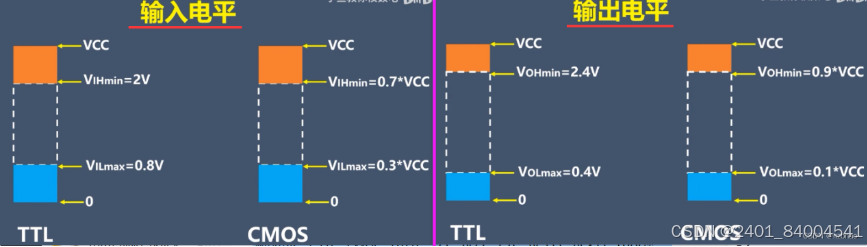

a. TTL电平

输出电平:高电平Uoh >=2.4v,低电平Uol <= 0.4v

输入电平:高电平Uih >= 2.0v,低电平 Uil <= 0.8v

b、CMOS电平

输出电平:高电平Uoh>= 0.9*VCC (≈ VCC), Uol <= 0.1*VCC(≈ GND)

输入电平:高电平Uih >= 0.7*VCC Uil <= 0.3*VCC

TTL电路是电流控制器件,而CMOS电路是电压控制器件

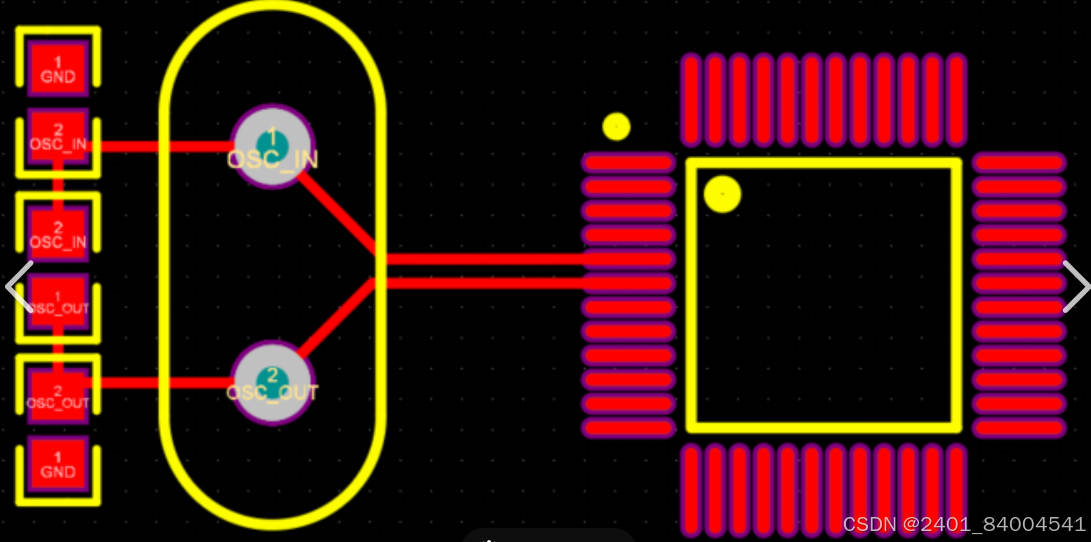

4、晶振PCB layout注意事项

4.1 晶振放置位置

a、靠近芯片(MCU、FPGA、时钟 IC)

晶振应尽量靠近芯片的时钟输入(XTAL_IN、XTAL_OUT)引脚,减少走线长度,降低寄生电感、电容对振荡信号的影响。

b、避免长走线和过孔

走线过长会引入额外的寄生电容和电感,影响振荡频率,甚至导致晶振不起振。

优先使用同层布线,避免跨层导致阻抗变化。

c、远离干扰源

避免靠近大电流、高速信号(如电源、PWM、SPI、DDR 信号等),减少 EMI 干扰。

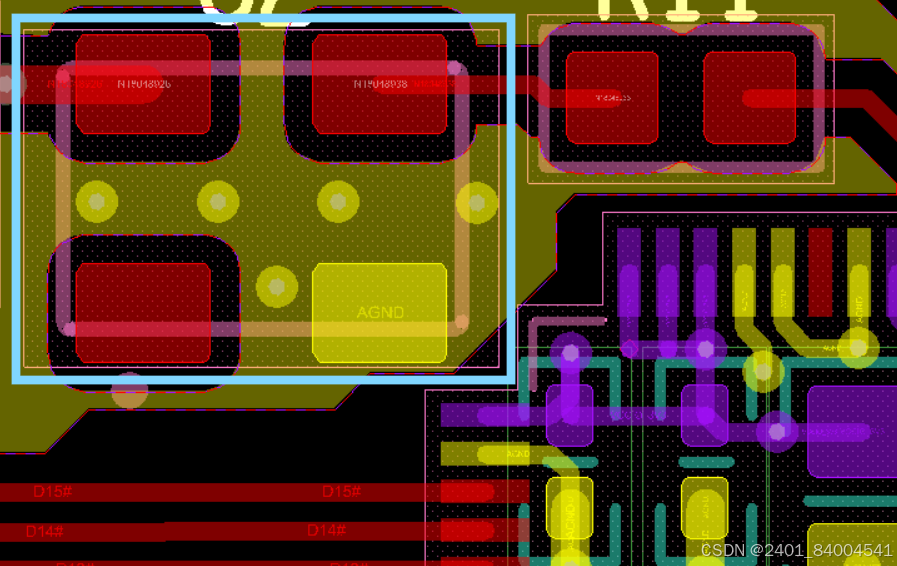

4.2 晶振布线(Routing)

a、晶振的负载电容(C1、C2)应尽量靠近晶振焊盘,减少寄生效应,晶体晶振本体下方所有层原则上不准许走线。

b、信号走线等长、短且粗

- 等长:保证 XTAL_IN 和 XTAL_OUT 走线等长,确保信号对称,减少相位偏移。

- 短且粗:减少电阻和电感影响,提高信号质量。

c、GND 参考层完整

晶振信号下方应该有完整的地平面,避免地层切割,否则会增加环路面积,降低抗干扰能力。

d、使用差分走线(LVDS / LVPECL)

- 如果是差分时钟信号(如 LVDS、LVPECL),必须遵循差分走线规则(等长、等间距、阻抗匹配)。

4.3 接地(GND)设计

a、晶振地线应尽量独立,减少噪声耦合

如果可能,在晶振附近单独布一小块局部地平面(局部屏蔽 GND),减少外部干扰。

对时钟信号需要进行包地处理,晶振电路做包地处理时需要打大量地孔,否则包地无意义

b、使用过孔降低地噪声

在晶振 GND 引脚周围放置多个地过孔,提高接地可靠性。

c、避免与高频信号共地

晶振的接地回路不应与高速数据线(如 USB、PCIe)或电源地混杂,避免噪声耦合。

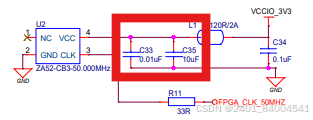

4.4 电源(VCC)设计

a、晶振电源引脚去耦

若晶振有 VCC(如有源晶振),应加 0.1uF 和 10uF 的去耦电容,靠近 VCC 引脚放置。

b、避免电源噪声

晶振电源应由低噪声电源供电,避免直接连接大功率元件(如 DC-DC 转换器)。

5、有源晶振、无源晶振测试

5.1 无源晶振测试

a、用万用表测试(只能判断好坏,不能判断震荡是否正常)

无源晶振(XTAL)本质上是一个无源压电元件,万用表无法测量它的振荡情况,但可以做简单的通断性检查:

测试 方法 :二极管档(或电阻档)测量两端阻值

- 将万用表拨到 二极管档(或 20MΩ 电阻档)。

- 分别测量晶振两端的阻值。

- 阻值接近无穷大(OL),因为晶振是一个无源谐振器,静态时不会导通。如果阻值很小(如几十欧姆),说明晶振可能短路损坏。

b、用示波器测试

测试方法 :示波器探测 MCU / FPGA 的 XTAL_OUT 引脚(不能直接测量晶振两端(XTAL_IN & XTAL_OUT)可能会干扰振荡。)

- 上电运行 MCU 或 FPGA,让晶振工作。

- 使用示波器 探头(10x 探头)测量XTAL_OUT 引脚,避免探测 XTAL_IN 引脚(该端信号较弱),带宽限制 ≤20MHz 以减少噪声。

- 观察波形:正确起振时,波形应呈现近似正弦波,峰峰值 0.2V - 1V,频率等于晶振标称频率。由于 MCU 内部有反馈放大器,信号可能会被削顶,形成畸变正弦波。

无源晶振削顶波形参考图

相关波形可参考以下博客:

5.2 有源晶振测试

a、用万用表测试(只能判断好坏,不能判断震荡是否正常)

有源晶振(如 CMOS、LVDS、LVPECL 晶振)需要供电才能工作,万用表可以用来检测供电情况,但不能直接测频率。

测试方法(CMOS、LVDS、LVPECL 晶振):

- 将万用表调到 直流电压档(DCV)。

- 黑表笔接 GND,红表笔测量晶振的 VCC 引脚。

- 确保电压符合晶振规格(如 3.3V、2.5V、1.8V)。

- 供电电压正常(如 3.3V)说明晶振已供电,可以工作;如果 VCC 为 0V,可能是电路供电异常或晶振损坏。

测试方法(仅CMOS 晶振):

- 将万用表调到 直流电压档(DCV)。

- 测量有源晶振的输出引脚(OUT也就是CLK)的电压。

- 如果晶振工作,输出端应有一个接近供电电压一半的平均电压(3.3V 供电,OUT 端测得约 1.6V(方波的平均值));如果输出电压 = 0V ,晶振可能未启动或损坏或输出电压 = 供电电压 ,可能是时钟 IC 关断了输出

万用表测量的是直流平均电压,不是实际的振荡波形,不能准确判断时钟是否工作

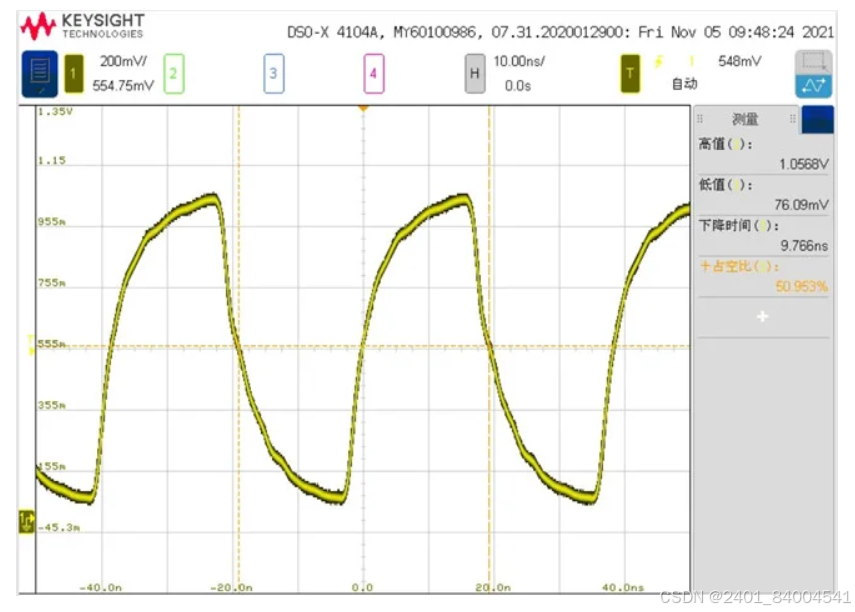

b、用示波器测试

测试方法 :有源晶振直接输出时钟信号

1.供电(如 3.3V、2.5V)给有源晶振。

2.使用 示波器(10x 探头) 测量输出信号(OUT 引脚,也就是CLK信号脚),带宽 ≥ 频率 3 倍。

3.观察波形,方波信号(CMOS输出晶振),峰峰值 接近供电电压(如 3.3V),确保频率和电压符合规格。

CMOS波形参考

LVDC波形参考

LVDS / LVPECL 晶振 输出的是差分信号,示波器测试时需要差分探头,或使用 GND + 单端探测(但信号质量会受影响); HCSL 晶振 需要50Ω 端接,否则信号可能出现反射。

若对时钟信号有严格要求(如 低抖动、高稳定性),可使用频谱分析仪或相位噪声测试仪来测量时钟质量。

在测量晶振波形时,一定要注意两个事情:1)示波器的带宽;2)负载电容。晶振对负载电容比较敏感,所以测量时要尽量减少输入电容对测量的影响。示波器操作可参考下文博客:如何用示波器测量晶振?_示波器测试晶振-CSDN博客

488

488

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?