文章目录

一:常见设计(均来自真实产品的设计)

- 自己动手画晶振和MCU连接,你能在不复制粘贴的情况下正确画出吗?下面给出答案,自己找共性。

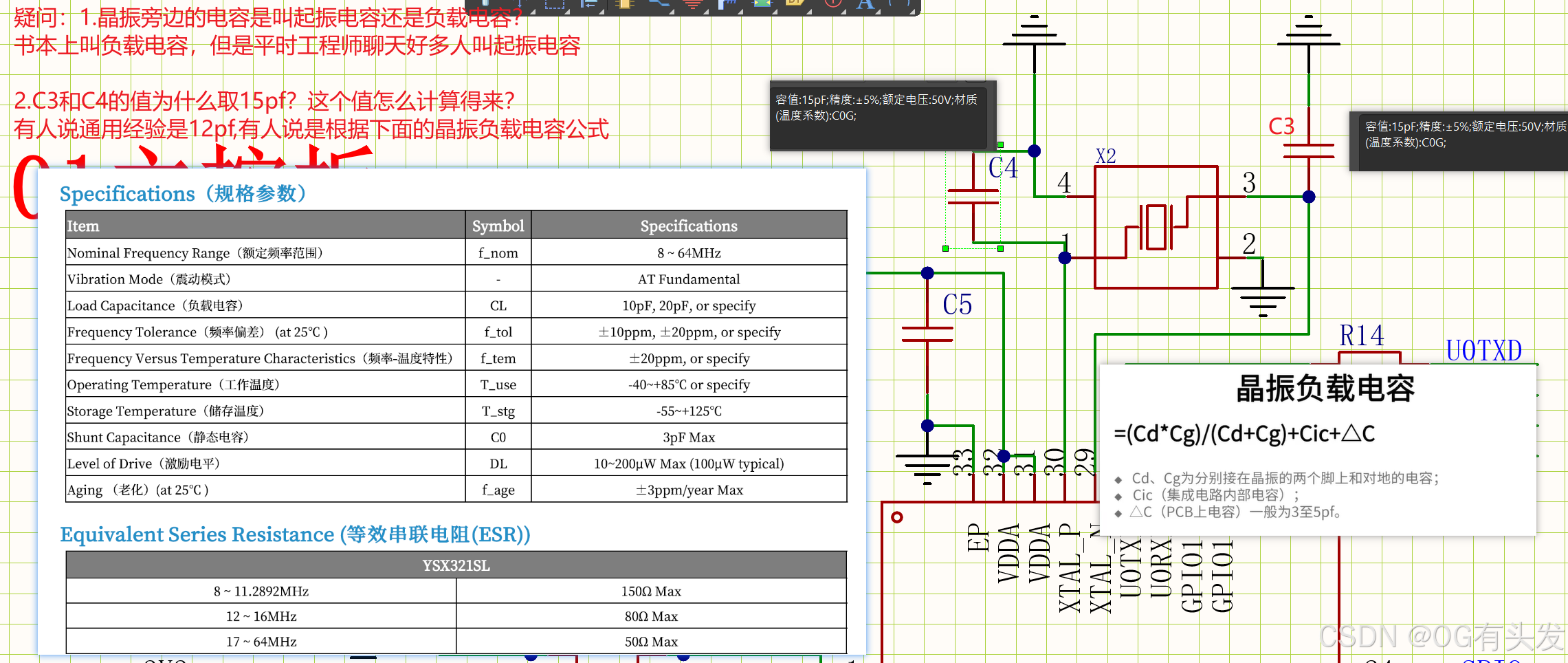

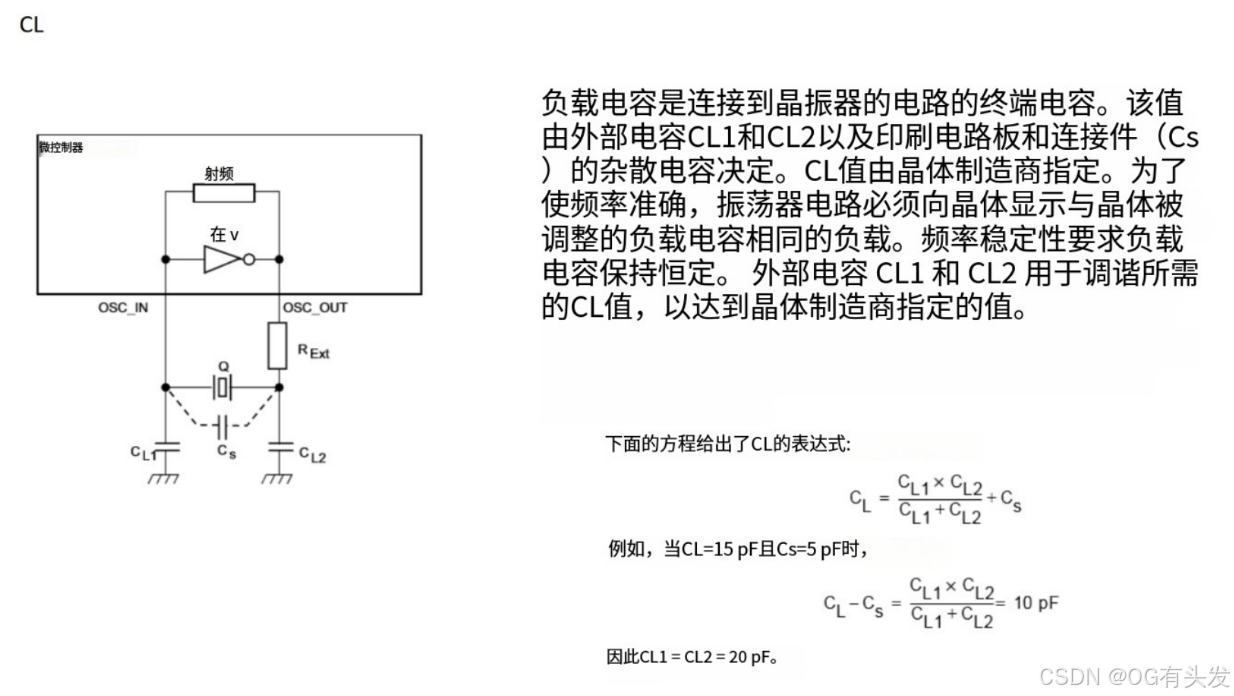

- 硬件-晶振选型-负载(起振)电容,计算晶振匹配电容?

- 本节目标是找到如何设计Cg和Cd的值,带着这个目的阅读本篇文章

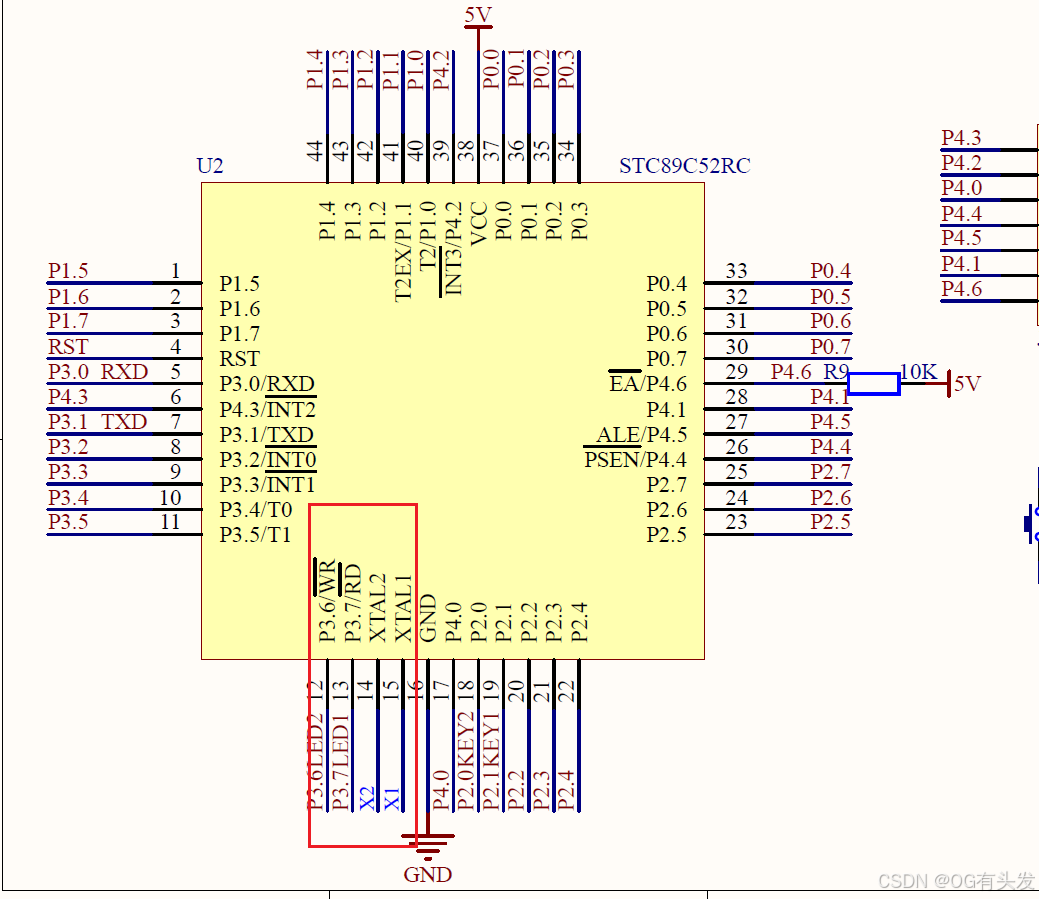

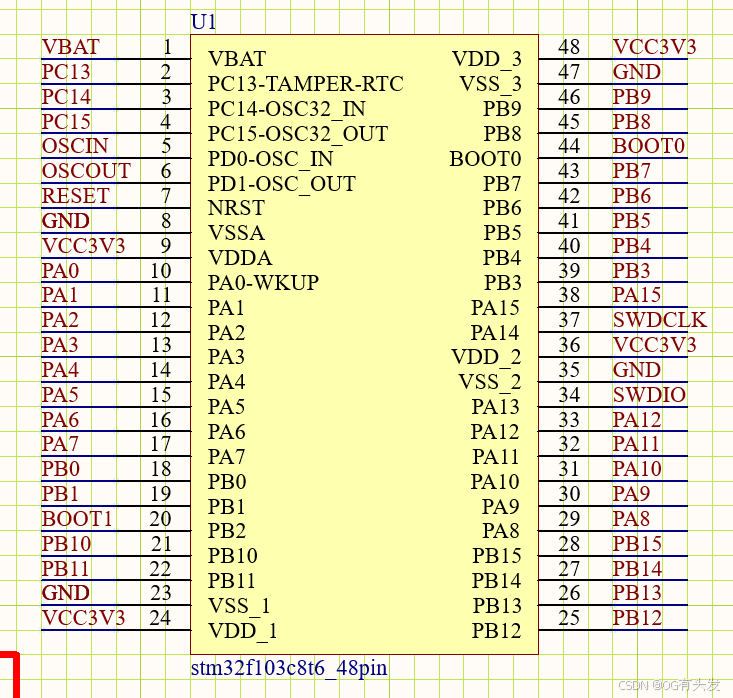

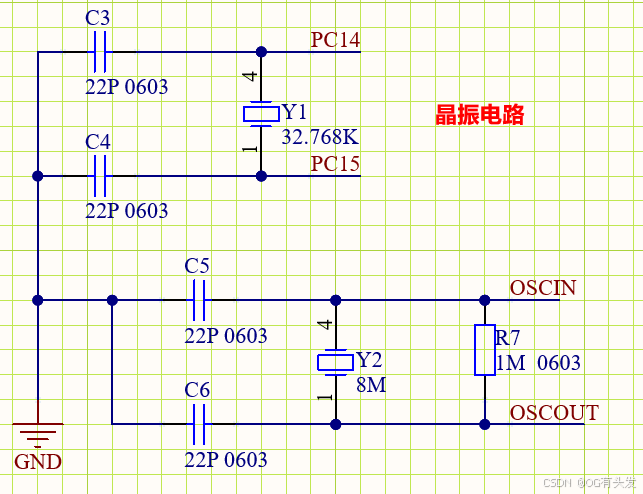

1.1 51单片机晶振设计参考

- MCU:STC89C52RC

- 负载电容取值:两个22pf

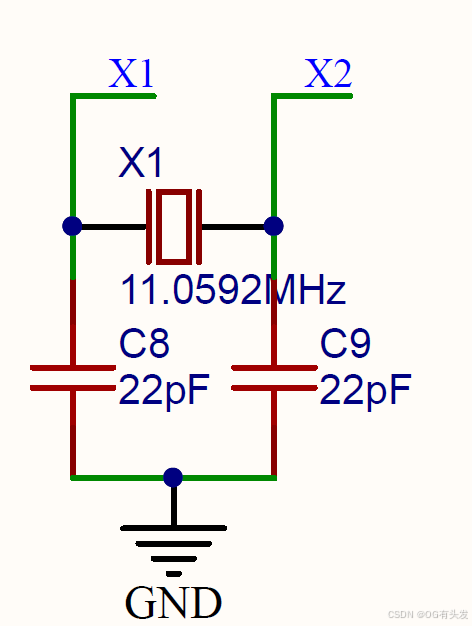

1.2 STM32晶振设计参考

- MCU:stm32f103c8t6

- 负载电容取值:两个22pf

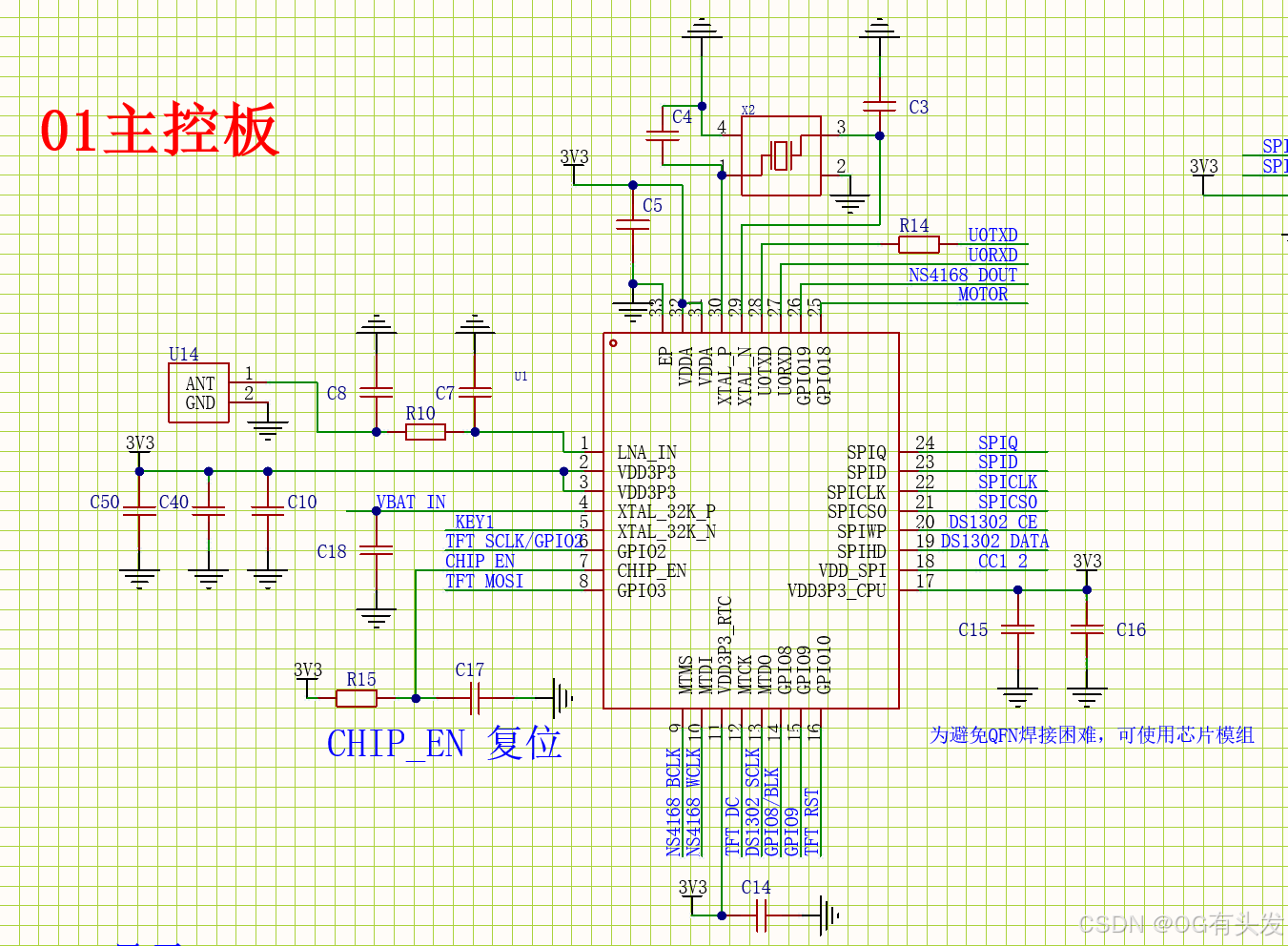

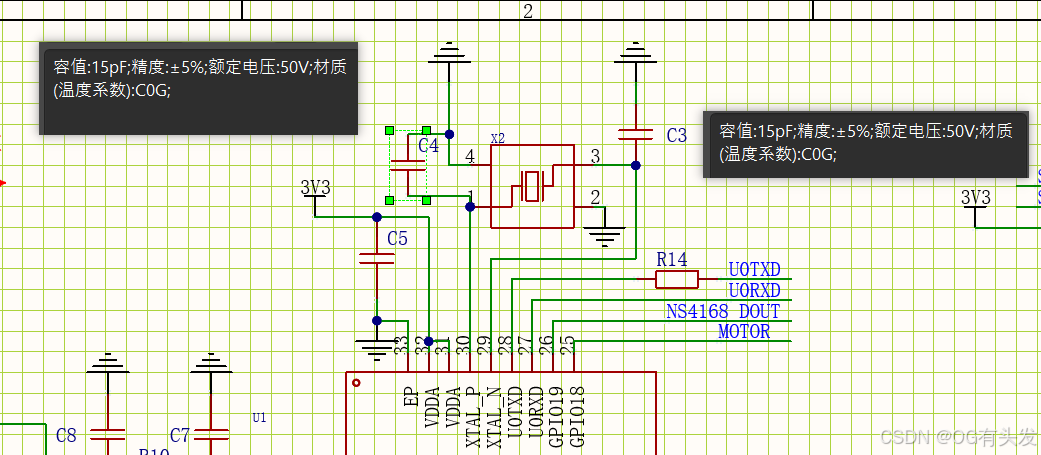

1.3 ESP32晶振设计参考

- MCU:ESP32-C3

- 负载电容取值:两个15pf

二:常见疑问

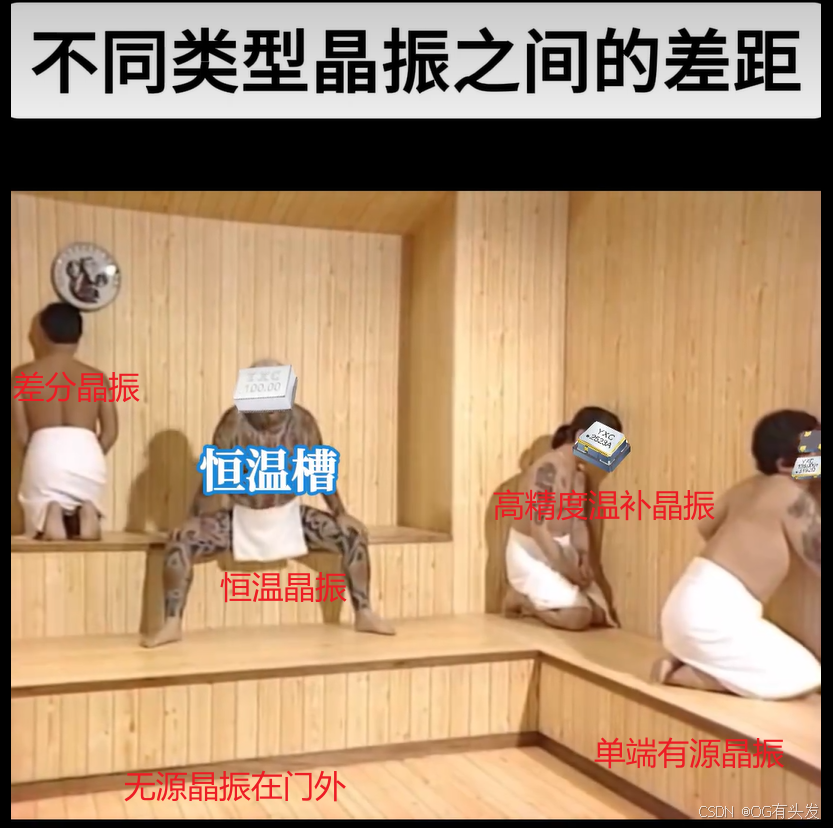

2.1 晶振江湖地位

- 消费电子领域常用无源晶振,因为便宜

- 晶振排位:无源晶振<单端有源晶振<差分晶振<高精度温补晶振<恒温晶振

2.2 有源晶振和无源晶振

晶振是我们数字电路中的心脏,有源晶振和无源晶振都可以作为我们芯片的时钟源

- 单片机的外部晶振是否稳定,受温度,湿度等环境因素影响比内部振荡器小,精度比较高。而且当设计需要降低功耗时,比如说便携式仪表等,就需要外设晶振,因为内部振荡器不能根据需要而停止,而外部晶振可以适时停止,从而进入休眠状态,降低功耗。

- 而单片机的内部晶振一般不够准确,误差比较大。但是单片机的内部晶振和外部晶振的作用都是一样的,给系统提供时钟。如果对频率要求不高的话(比如不涉及串口通信和精确定时等的话),用内部晶振就足够了,并且这样成本还低。

如果对频率要求不高,一般是优先选用内部振荡起振电容的选择:

①根据数据手册选择

②在许可范围内起振电容值越小越好,C值偏大有利于稳定,但会增加起振时间。一般为15p—30p之间,电容在地和输入输出之间。

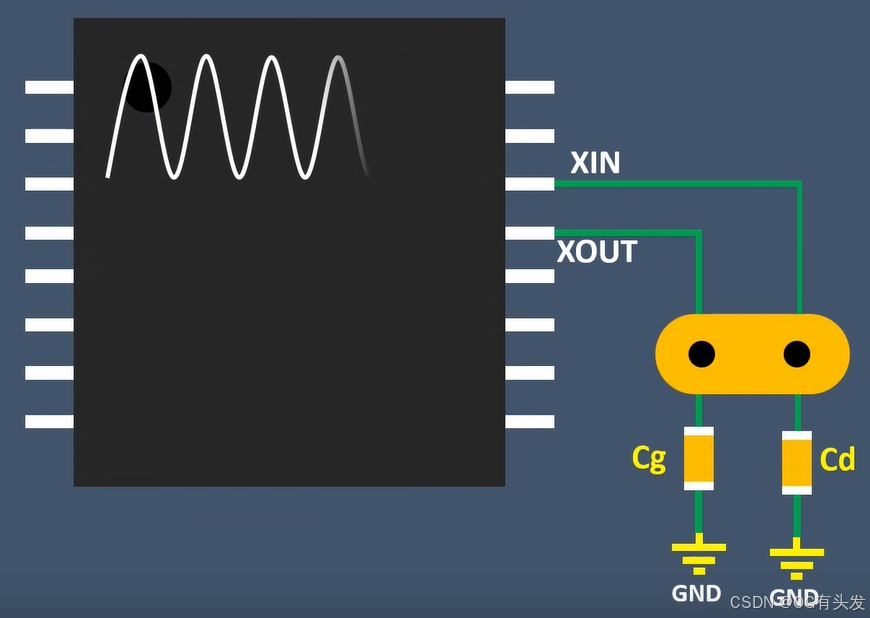

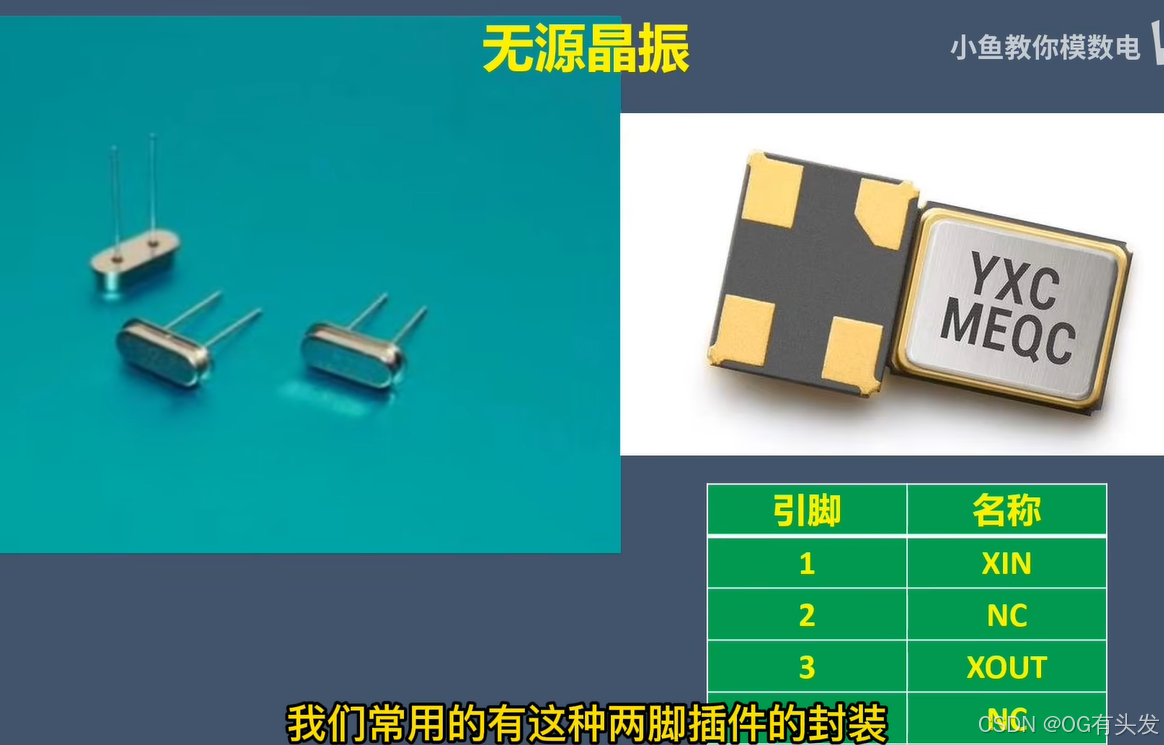

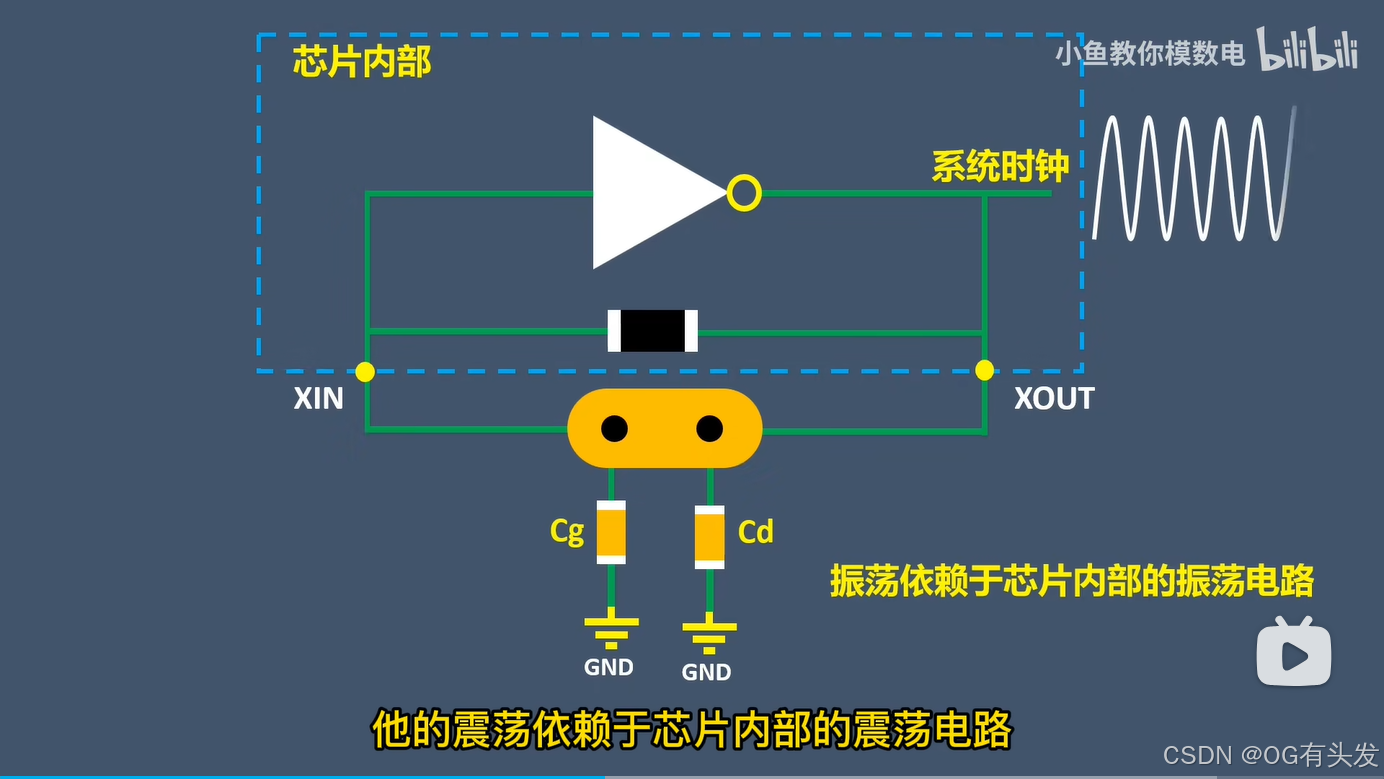

- 无源晶振:不需要为其供电,它的震荡依赖于芯片内部的震荡电路,它的自己是不能产生时钟信号的

- 常用两个封装,一个两脚封装,一个4脚封装(两个GND,一个晶振输入一个输出,同时输入输出必须接电容再接地,注意顺序,这样子电容才能参与晶振的起振)

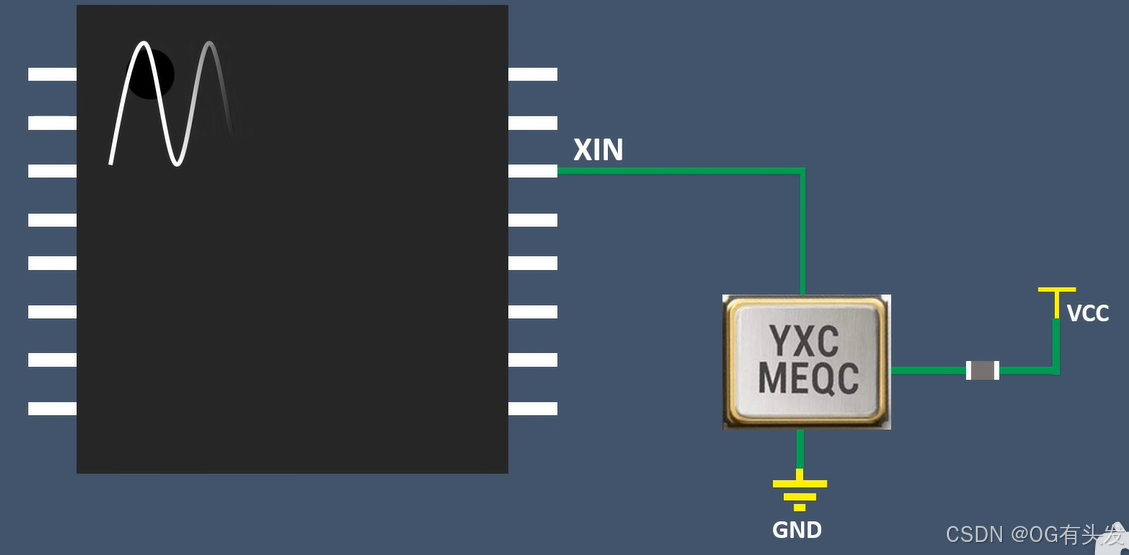

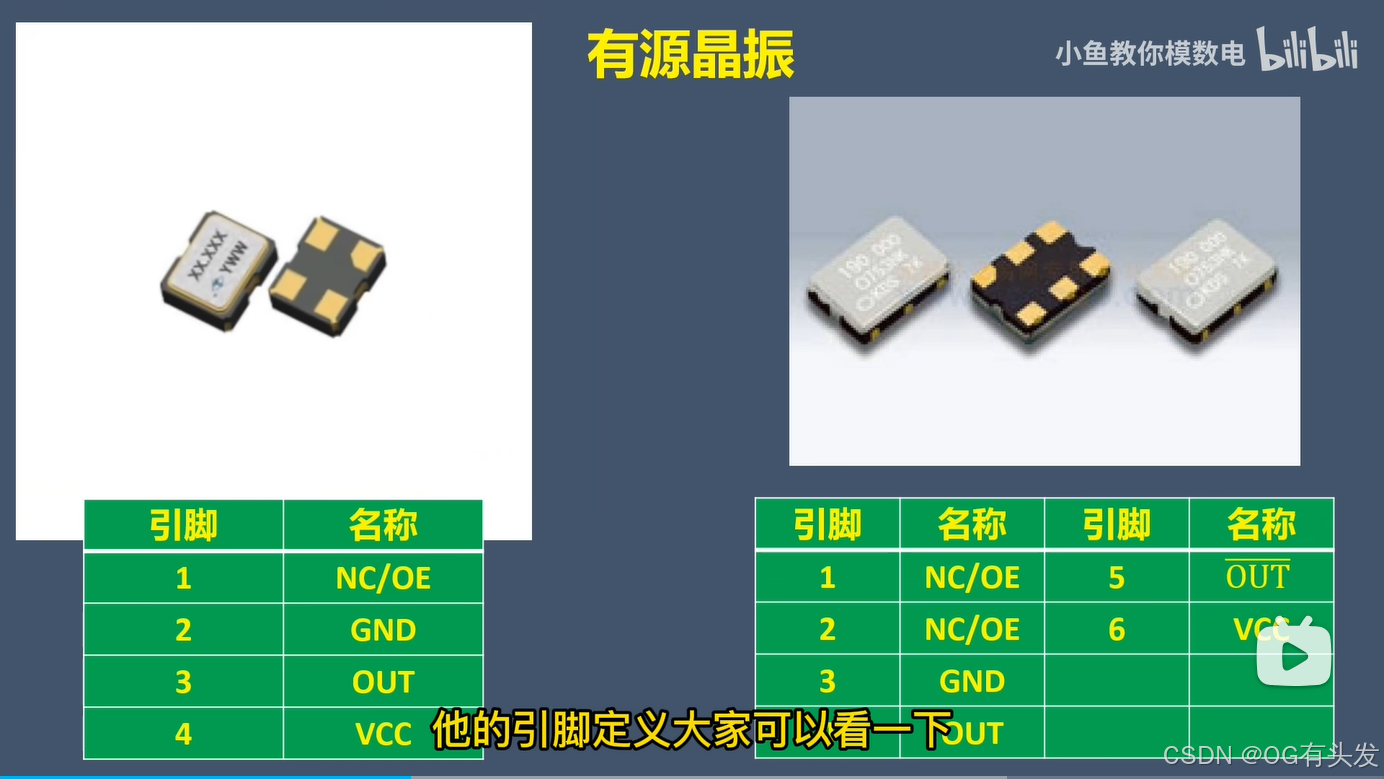

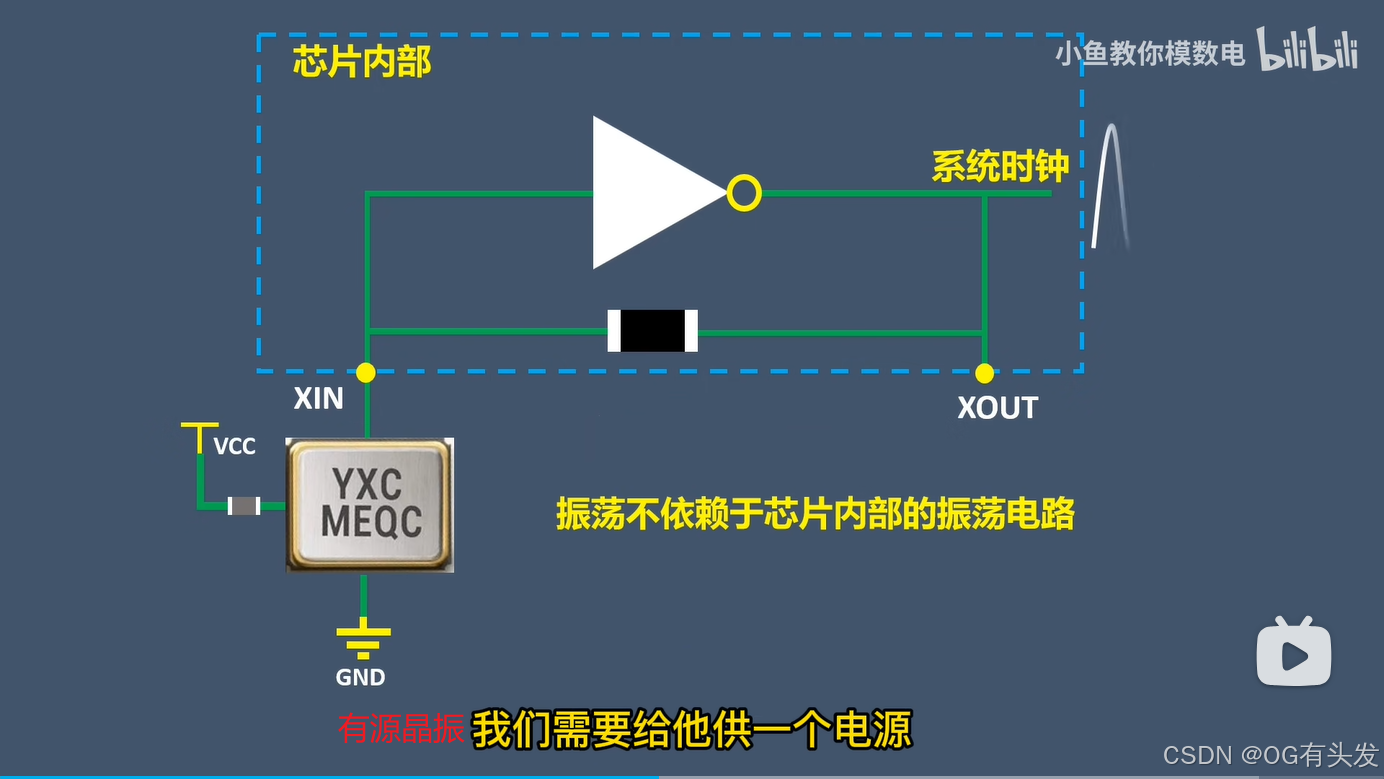

- 有源晶振:更准确应该叫振荡器,需要为其供一个电源,它的振荡不依赖于芯片内部的振荡电路,给他电源就能产生时钟信号

- 封装有4脚、6脚,其中6脚封装里的两脚(图中的4和5脚)是差分信号,常见差分信号有LVDS、LVPECL这种差分信号

- 有源晶振=无源晶振+振荡电路

现在大部分芯片是都可以支持有源晶振和无源晶振,它的时钟输入是既可以支持有源晶振又可以支持无源晶振。

- 注意:对于有源晶振,我们常常在他的电源上串联一个磁珠,放置这个晶振的一些高频噪声串到这个电源上

三:晶振匹配电容计算

3.1 无源晶振电路影响因子

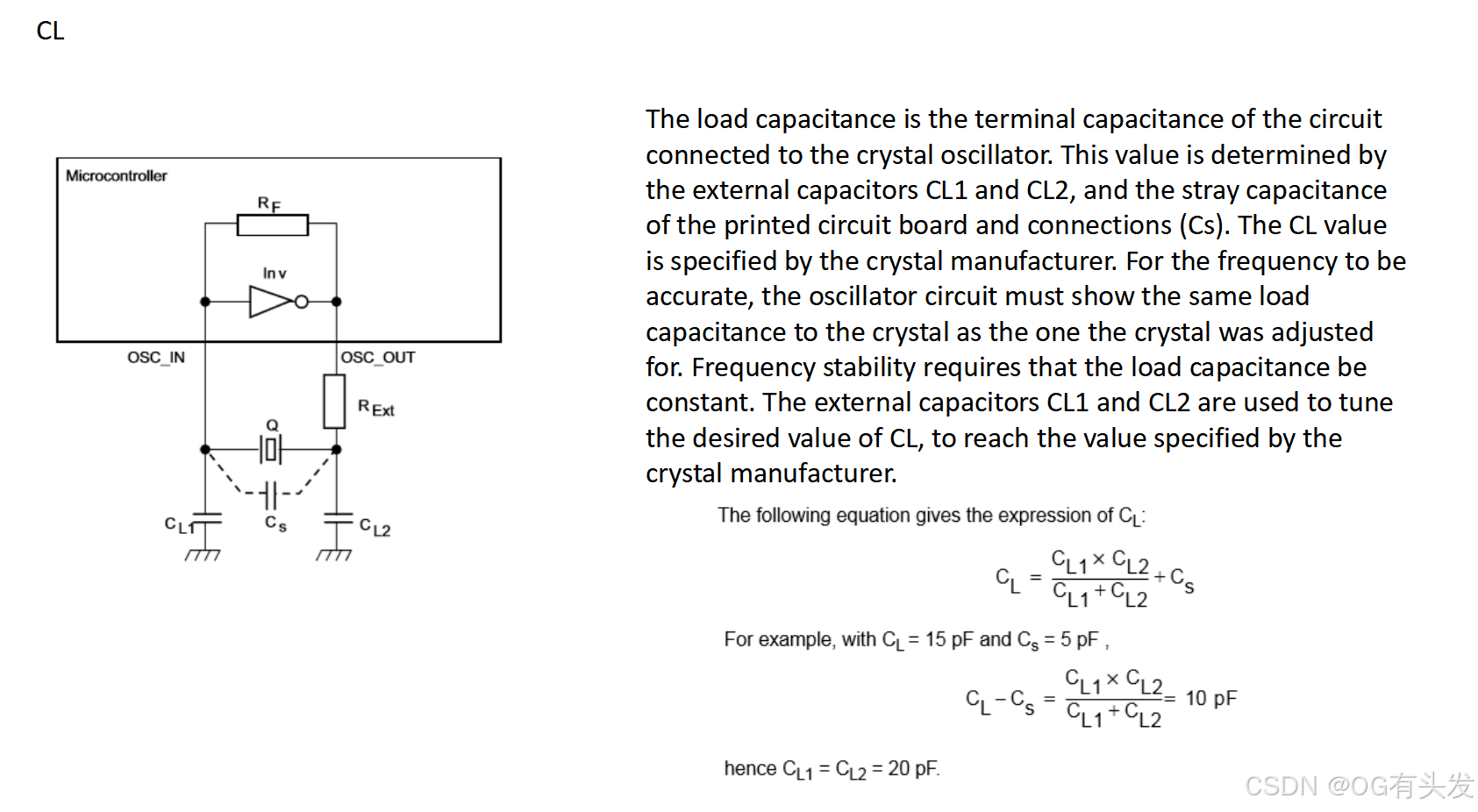

- 无源晶振频率受外接负载电容,杂散电容还有芯片的io寄生电容的影响,而有源晶振频率比较稳定,受外界参数影响小。

- 价格方面:有源晶振比较贵,无源晶振便宜,所以消费电子行业多用无源晶振。

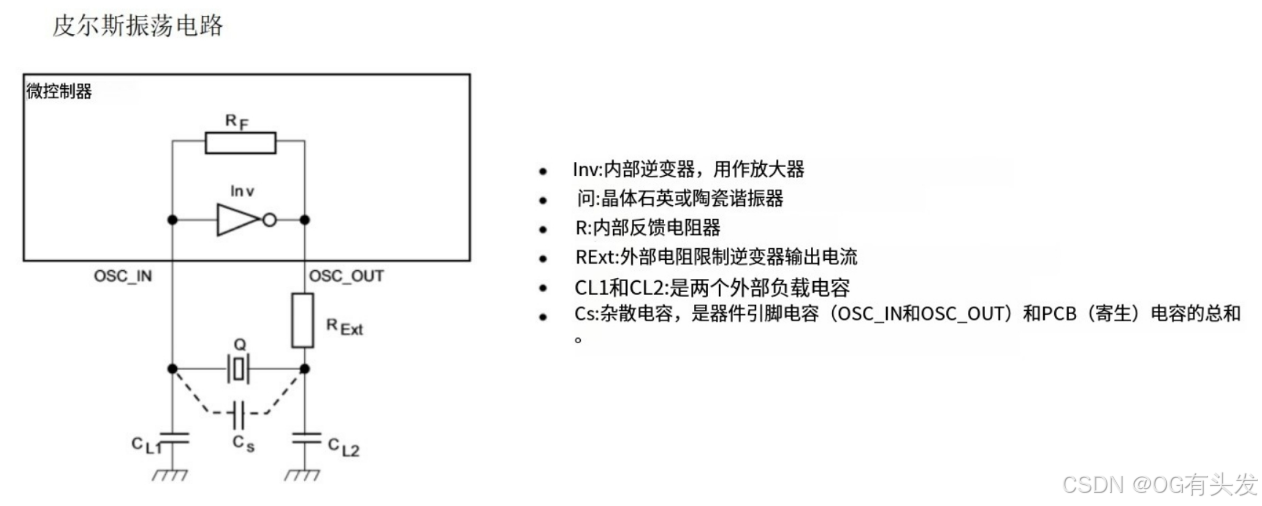

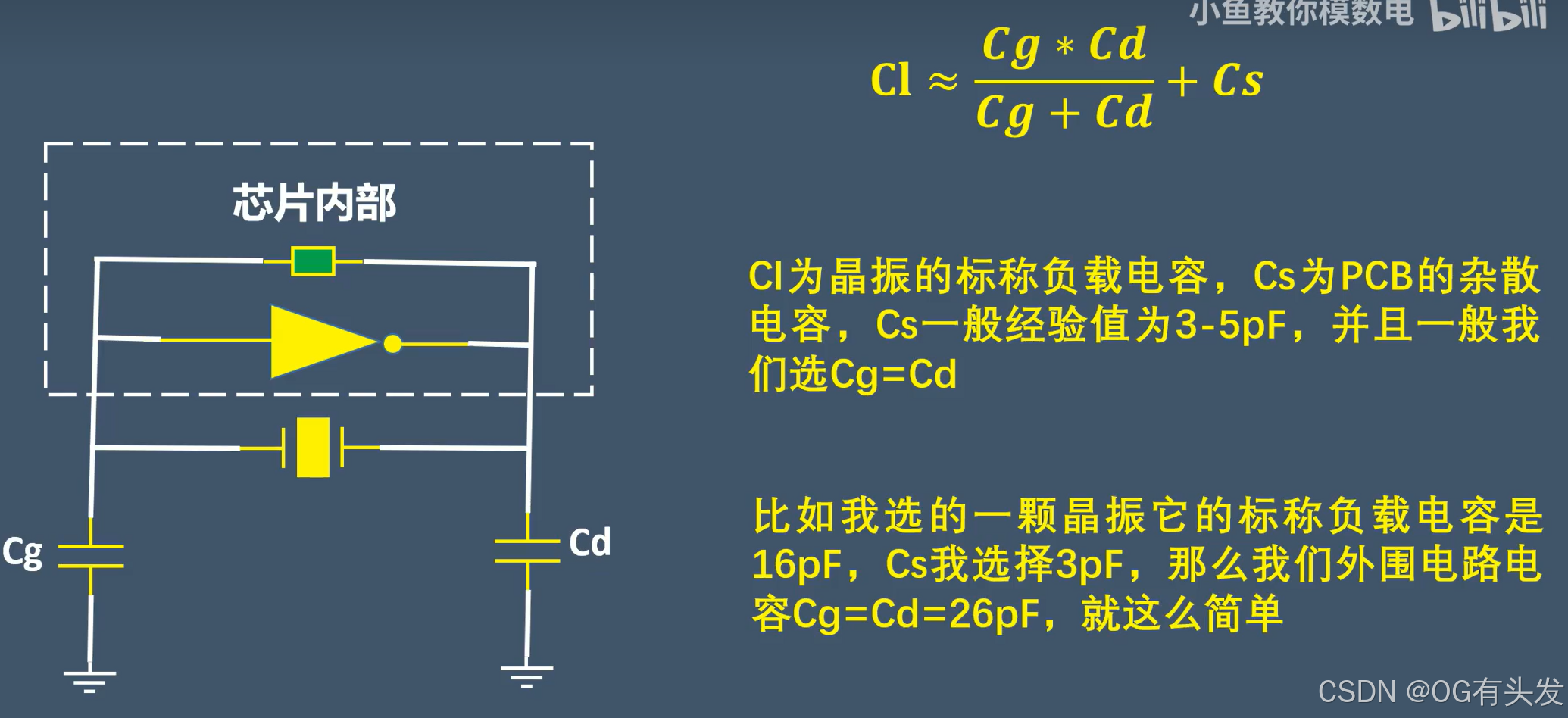

3.2 皮尔斯振荡电路

- 看数据手册,我们要设计的就只有Cg和Cd

3.3 实际例子理论计算(重点)

按照该晶振手册数据

- 1.电容标称值负载电容Cl是10pf((规格书上写的,器件的性质决定)),杂散电容C0是3pf,根据公式计算得Cg=Cd=14pf,结合实际产品分析,晶振电容选取15pf合理

- 2.电容标称值负载电容Cl是20pf,杂散电容C0是3pf,根据公式计算得Cg=Cd=34pf

- 下图的计算公式,因为计算是无源晶振,没有集成电路内部电容,所以忽略Cic,只计算PCB上的杂散电容3-5pf

四:晶振波形&频谱分析仪

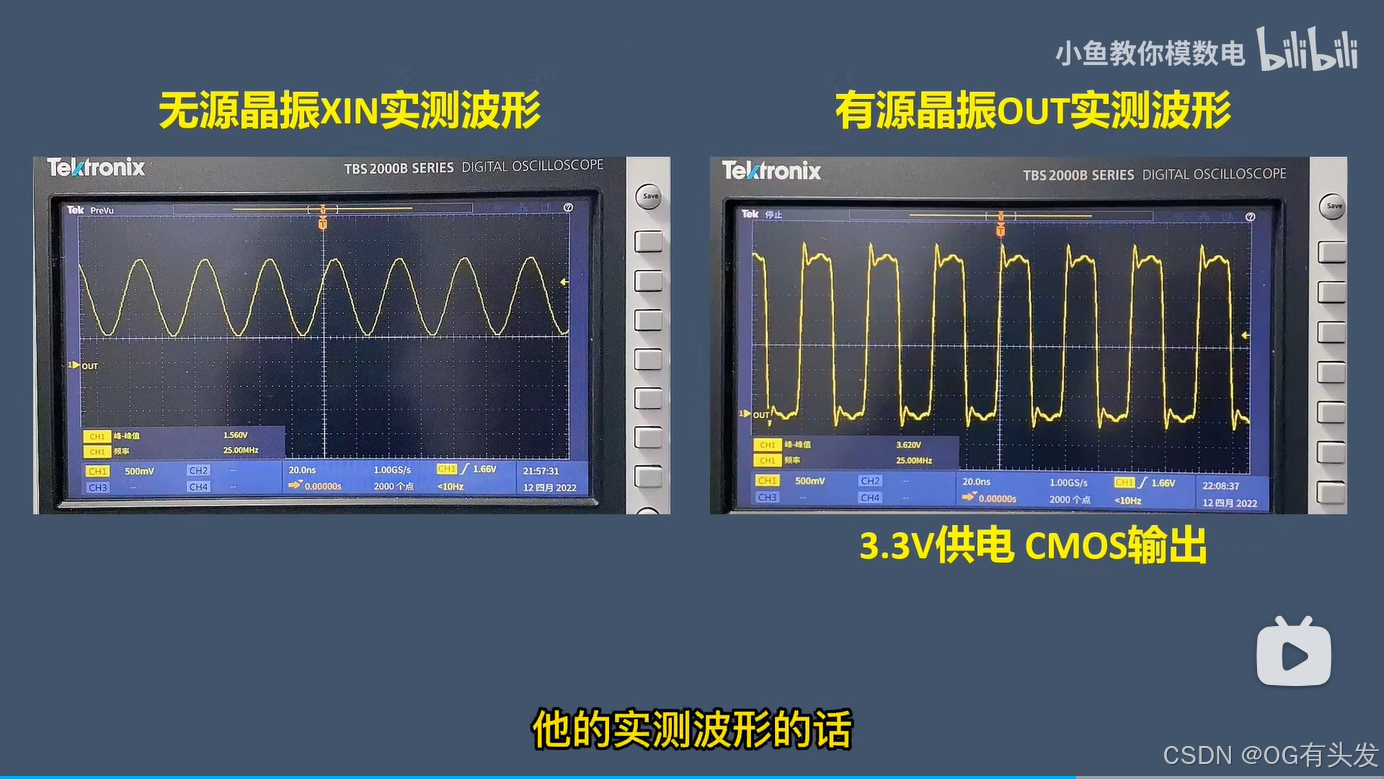

4.1 有源晶振和无源晶振实测波形

- 一个是正弦波一个是方波

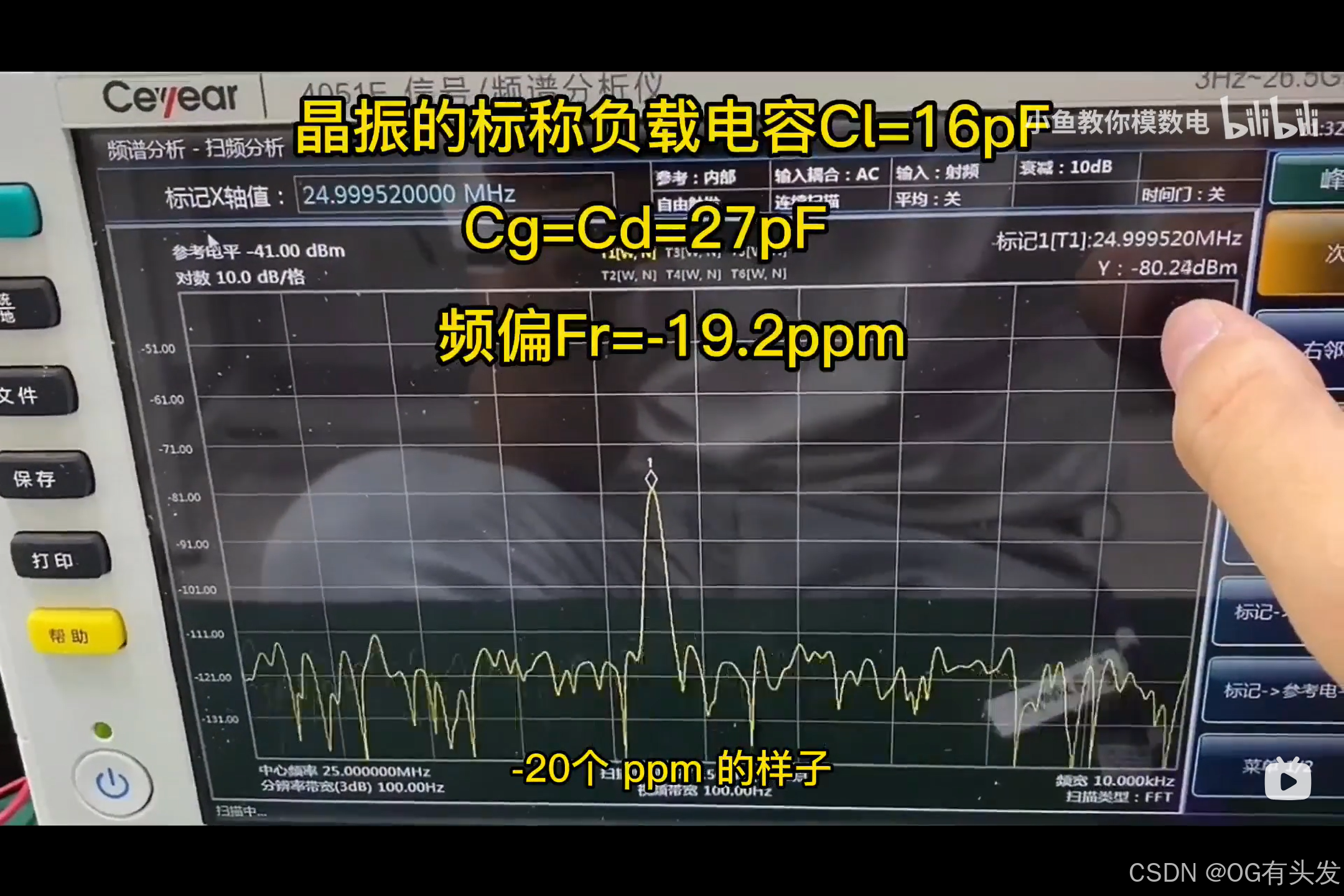

4.2 频谱分析仪

一般搞射频的人用频谱分析仪,EMC

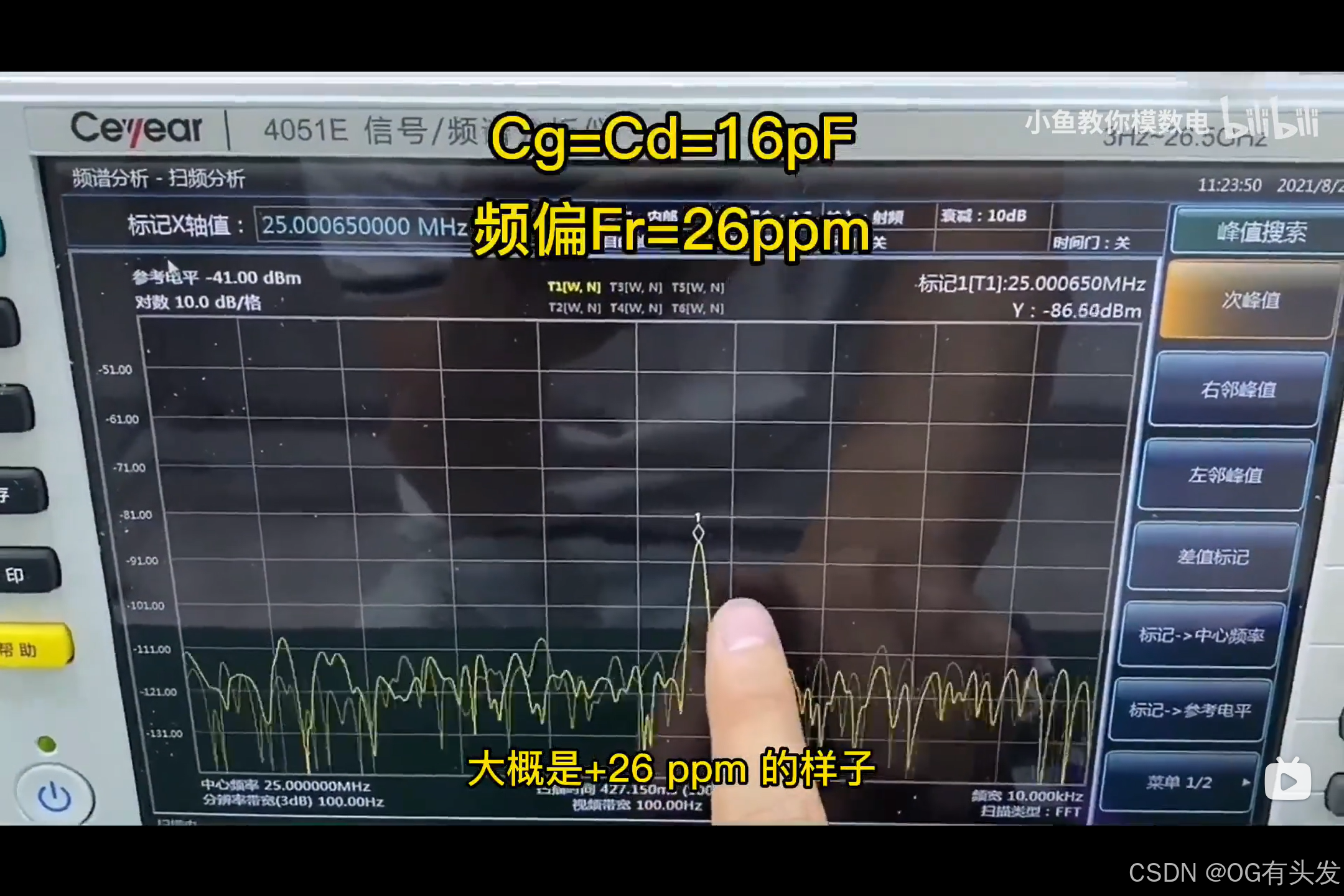

举例子:晶振的标称负载电容Cl=16pf(规格书上写的,器件的性质决定),负载电容Cg=Cd=27pf(理论是26pf,图片实际电容取27pf)

- 1.负载电容Cg=Cd=27pf,此时测出来的频率是24.999520MHZ,频偏Fr大概是-20个ppm

- 2.负载电容Cg=Cd=16pf,此时测出来的频率是25.000650MHZ,频偏Fr大概是26ppm

- 我们现在上16pf和27pf的电容,感觉都是频偏不是很大

- 注意:

1.老师傅说无源晶振常用(负载)起振电容取值是10-30pf,就是要根据实际情况分析才能得到合适的值。

2.当Cg和Cd变大,晶体振荡的频率变小。

3.示波器测量频率精度很差的。无源晶振波形是正弦波

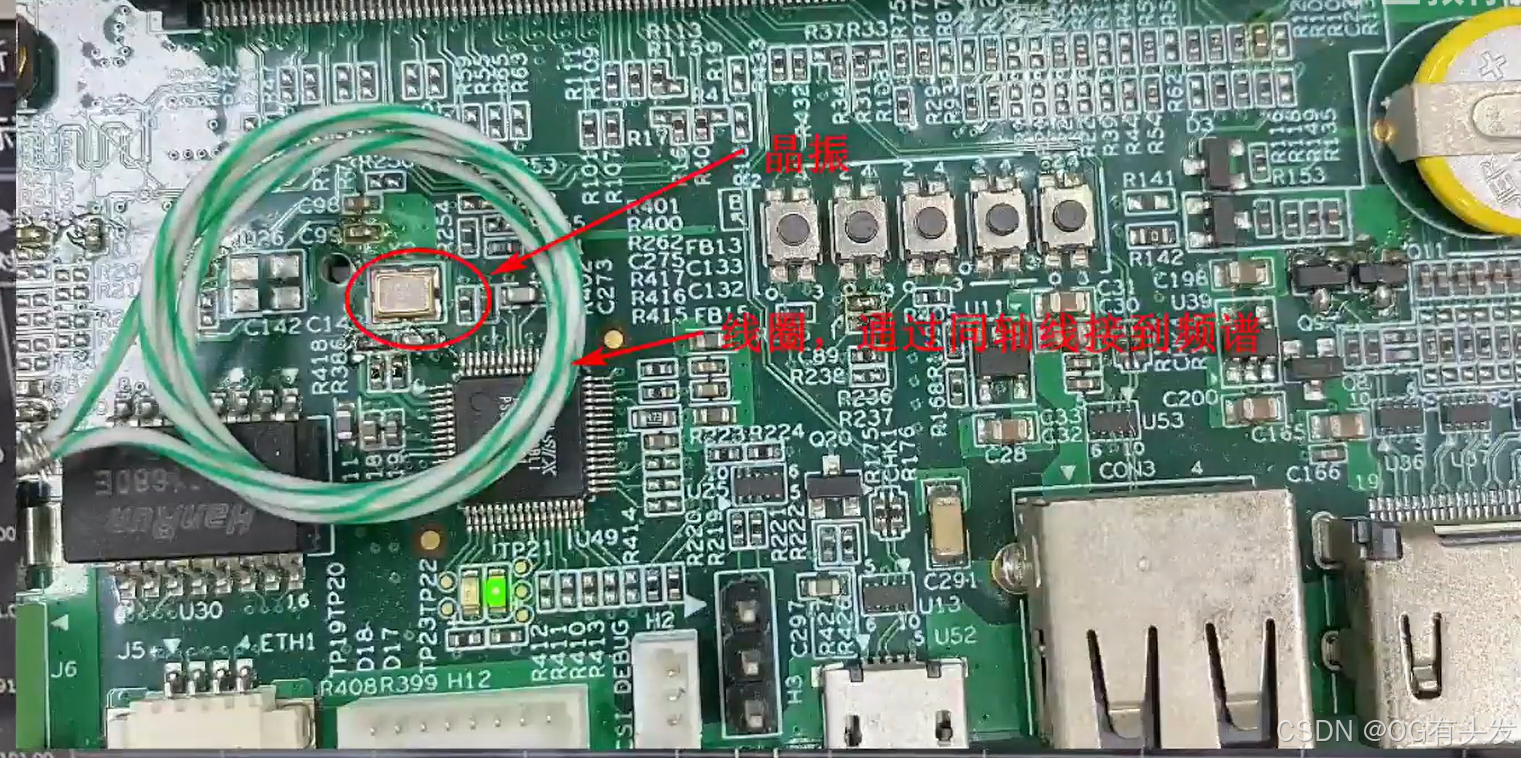

- 测量方法:频谱用一个线圈做一个传感器就可以测

- 总结:

- 1.对频率要求高上有温度补偿的有源晶振,无源晶振和谐振电容都有误差,一个个调做样品可以量产是不行的。大部分场合频率差不多就能可靠使用了,无需调校到精确频率。

- 2.这只是一般情况,STM有一篇专门对这个进行讲解的文档,像皮尔斯振荡器,不仅要考虑晶振本身的电容,也要根据芯片手册确定芯片时钟输入端的电容,甚至在较高频率的震荡中还要考虑寄生电容和分布电感,也要分割地平面,官方给出的电路也标注了在不同情况下的各种参数,文件《“Oscillator design guide for ST microcontrollers”》

4.3 单片机上电后没有运转,首先要检查什么?

- 1.首先应该确认电源电压是否正常。用电压表测量接地引脚跟电源引脚之间的电压,看是否是电源电压,例如常用的5V。

- 2.接下来就是检查复位引脚电压是否正常。分别测量按下复位按钮和放开复位按钮的电压值,看是否正确。

- 3.然后再检查晶振是否起振了,一般用示波器来看晶振引脚的波形,注意应该使用示波器探头的“X10”档。另一个办法是测量复位状态下的IO口电平,按住复位键不放,然后测量IO口(没接外部上拉的P0口除外)的电压,看是否是高电平,如果不是高电平,则多半是因为晶振没有起振。

- 4.另外还要注意的地方是,如果使用片内ROM的话(大部分情况下如此,现在已经很少有用外部扩ROM的了),一定要将EA引脚拉高,否则会出现程序乱跑的情况。有时用仿真器可以,而烧入片子不行,往往是因为EA引脚没拉高的缘故(当然,晶振没起振也是原因之一)。

- 经过上面几点的检查,一般即可排除故障了。如果系统不稳定的话,有时是因为电源滤波不好导致的。在单片机的电源引脚跟地引脚之间接上一个0.1uF的电容会有所改善。如果电源没有滤波电容的话,则需要再接一个更大滤波电容,例如220uF的。遇到系统不稳定时,就可以并上电容试试(越靠近芯片越好)。

五:PCB晶振布局

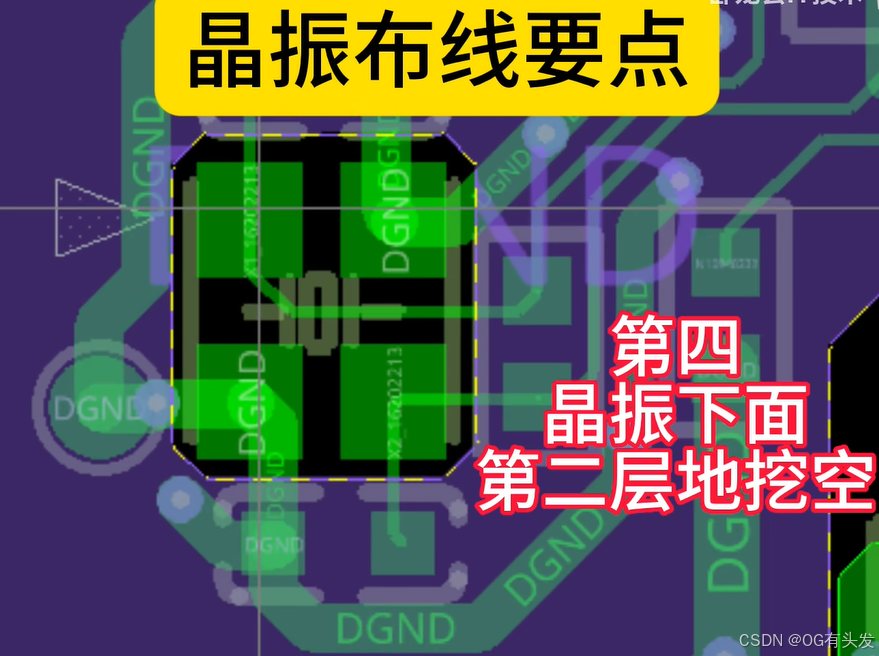

5.1 总结:

- 1.晶振靠近芯片;

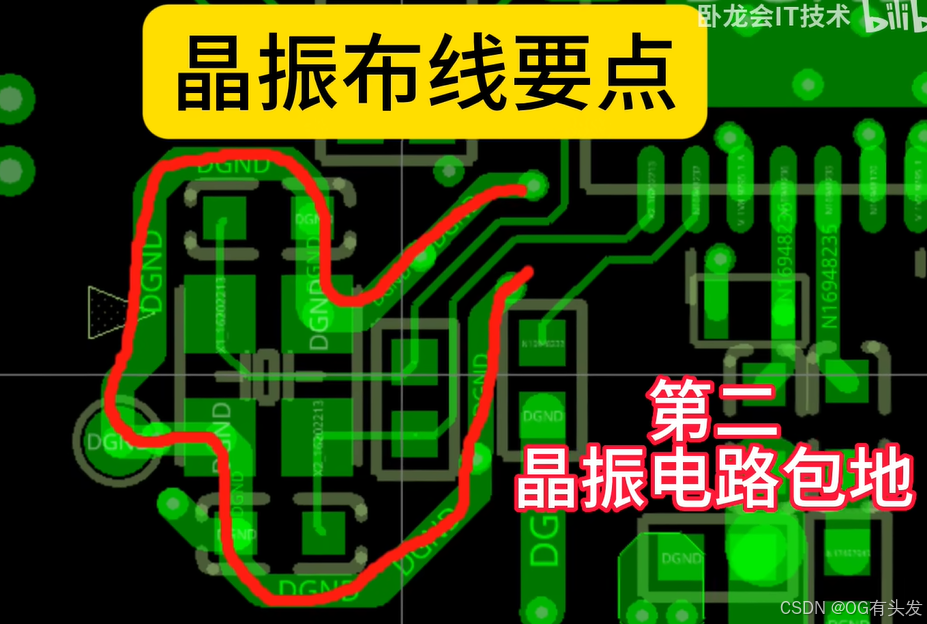

- 2.晶振电路包地;

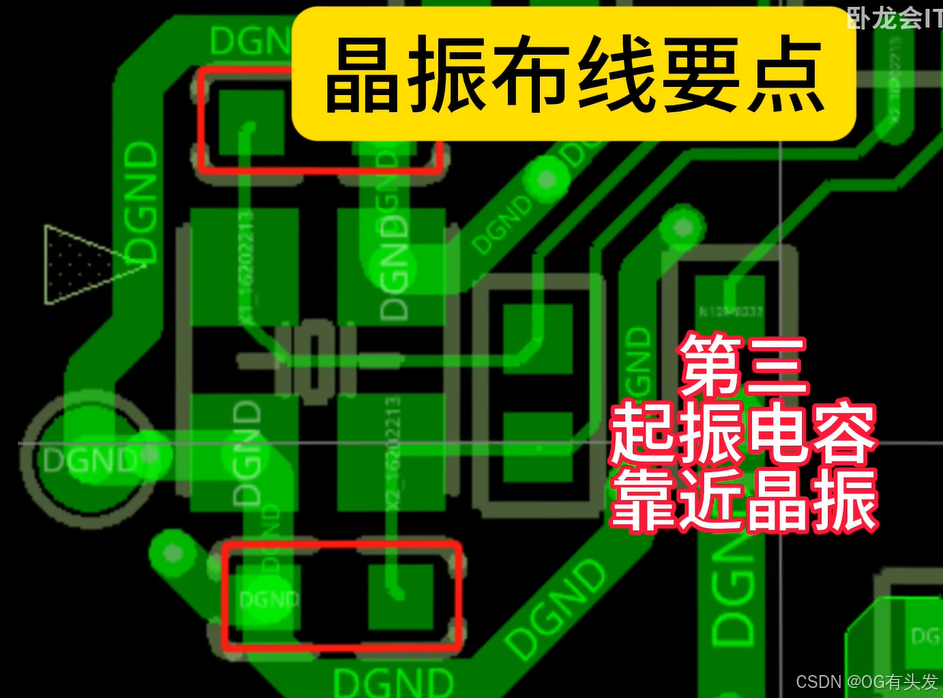

- 3.起振电容靠近晶振;

- 4.晶振下面第二层挖空;

- 挖空处理是一为了保证负载电容的恒定,晶振的两个焊盘与其下方的平面层之间会形成寄生电容,该电容会影响晶振的频偏,导致系统工作不正常,为了减少寄生电容,需要在晶振下方的平面层做挖空处理,让焊盘到平面的距离增大;二是为了抑制热传导的频偏影响,晶振的频率会受到温度的影响,如果周围有发热的器件会通过铜皮传导到晶振,从而造成频偏,为了隔绝热传导,需要用挖空处理。

- 多层板层与层之间的厚度很小,相当于是挨的很紧的极板,电容会大一些。

所以可以考虑把晶振下面的几层铜挖掉减小电容,而最后一层铜一般不挖,避免高频透过去。

双层板,就完全没有必要挖了。- 包铜是只在晶振外围用一圈gnd的线包围晶振,隔一段距离打一个过孔,而铺铜是指在晶振下方铺大链接的铜层,这是两个不同的概念,两者都对晶振稳定运行利好

- 5.晶振不能靠近板边;

- 6.晶振下面所有层不能布线(高速板太密集起码相邻层不能布线)

以上,完

8960

8960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?