网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

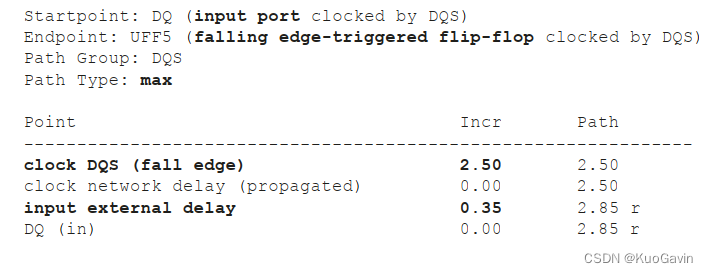

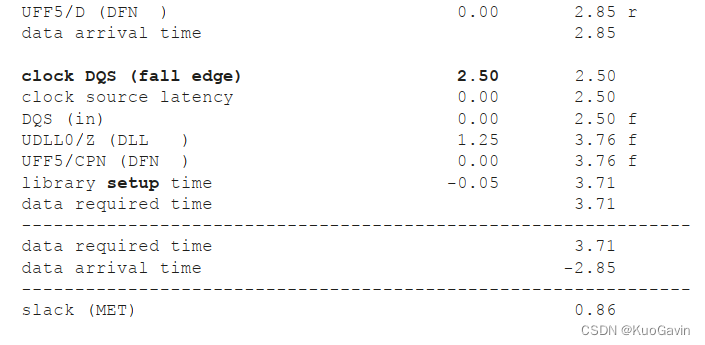

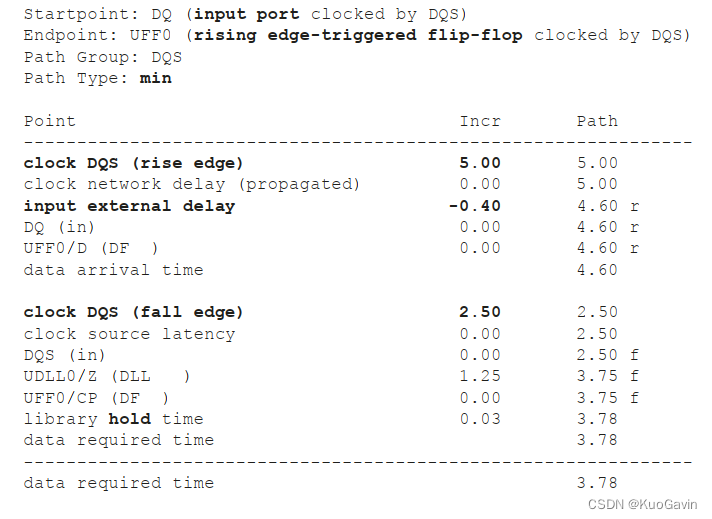

以下是保持时间检查的路径报告:

9.3.2 写周期(Write Cycle)

在写周期中,

D

Q

S

DQS

DQS沿会与从

D

U

A

DUA

DUA内存储控制器输出的

D

Q

DQ

DQ信号相差四分之一周期,因此存储器可以直接使用

D

Q

S

DQS

DQS选通脉冲去捕获数据。

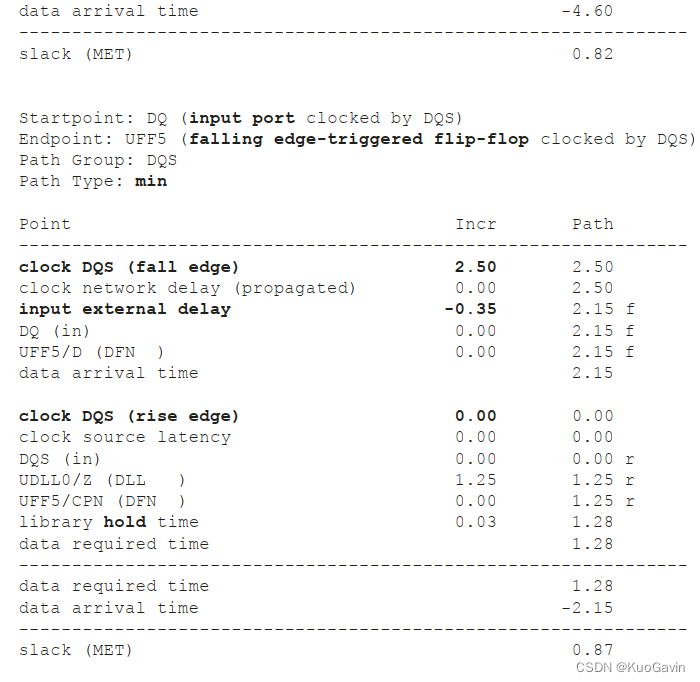

图9-13显示了存储器引脚上所需的波形,在存储器引脚处,

D

Q

S

DQS

DQS信号必须与

D

Q

DQ

DQ数据窗口的中心对齐。请注意,仍然是由于

I

O

IO

IO缓冲器延迟不匹配或者

P

C

B

PCB

PCB互连走线的变化,仅在存储控制器(

D

U

A

DUA

DUA内部)中对齐

D

Q

DQ

DQ和

D

Q

S

DQS

DQS还不足以使这些信号在

S

D

R

A

M

SDRAM

SDRAM存储器引脚处真正的对齐。因此,

D

U

A

DUA

DUA通常在写周期中使用额外的

D

L

L

DLL

DLL去进行控制,以实现

D

Q

S

DQS

DQS和

D

Q

DQ

DQ信号之间所需的四分之一周期偏移(offset)。

如何约束此模式的输出取决于控制器中时钟的生成方式,接下来我们考虑两种不同情况。

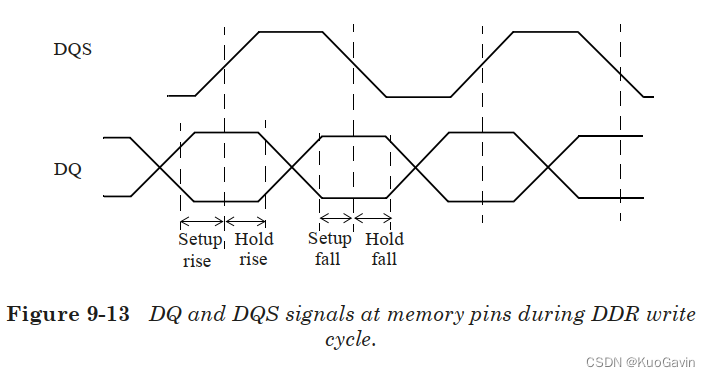

情况1:内部二倍频时钟(Case 1: Internal 2x Clock)

如果内部时钟是

D

D

R

DDR

DDR时钟频率的两倍,则输出逻辑可以类似于图9-14中所示。

D

L

L

DLL

DLL提供了一种必要时使

D

Q

S

DQS

DQS时钟偏斜的机制,从而满足存储器引脚上的建立时间和保持时间要求。在某些情况下,可以不使用

D

L

L

DLL

DLL,而是使用负沿触发的触发器来获得

90

90

90度的偏移。

对于图9-14中所示情况,可以进行如下输出延迟约束:

# 166MHz (333Mbps) DDR; 2x clock is at 333MHz:

create_clock -period 3 [get_ports CLK2X]

# Define a 1x generated clock at the output of flip-flop:

create_generated_clock -name pre_DQS -source CLK2X \

-divide_by 2 [get_pins UFF1/Q]

# Create the delayed version as DQS assuming 1.5ns DLL delay:

create_generated_clock -name DQS -source UFF1/Q \

-edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

D

Q

DQ

DQ输出引脚上的时序必须相对于衍生时钟

D

Q

S

DQS

DQS进行约束。

假设

D

D

R

S

D

R

A

M

DDR,, SDRAM

DDRSDRAM的

D

Q

DQ

DQ和

D

Q

S

DQS

DQS引脚之间建立时间要求分别为

D

Q

DQ

DQ上升沿的

0.25

n

s

0.25ns

0.25ns和下降沿的

0.4

n

s

0.4ns

0.4ns。类似地,假设

D

Q

DQ

DQ引脚上升沿和下降沿的保持时间要求分别为

0.15

n

s

0.15ns

0.15ns和

0.2

n

s

0.2ns

0.2ns。

D

Q

S

DQS

DQS输出上的

D

L

L

DLL

DLL延迟已设置为四分之一周期,即

1.5

n

s

1.5ns

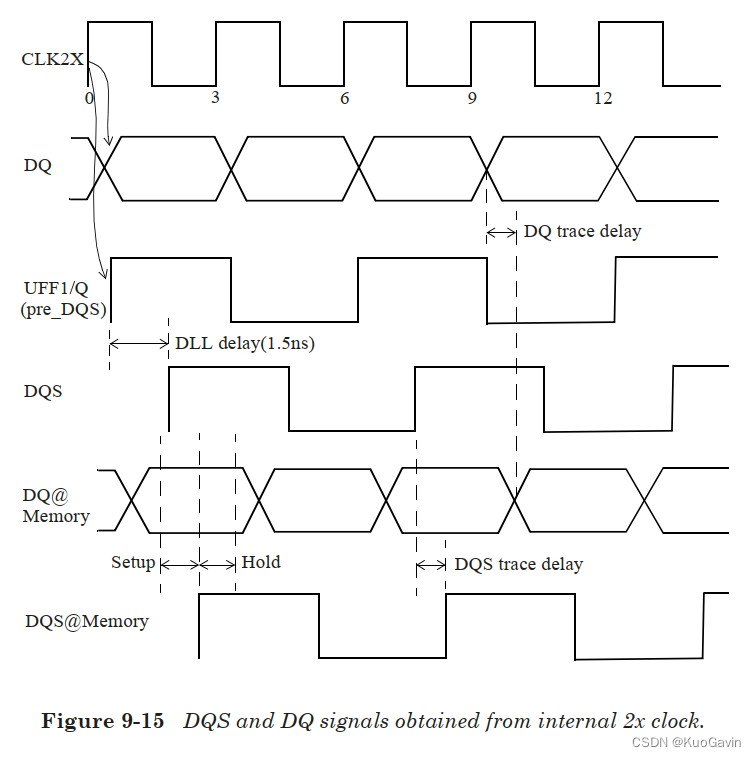

1.5ns,所有波形如下图9-15所示:

set_output_delay -clock DQS -max 0.25 -rise [get_ports DQ]

# Default above is rising clock.

set_output_delay -clock DQS -max 0.4 -fall [get_ports DQ]

# If setup requirements are different for falling edge of DQS,

# that can be specified by using the -clock\_fall option.

set_output_delay -clock DQS -min -0.15 -rise DQ

set_output_delay -clock DQS -min -0.2 -fall DQ

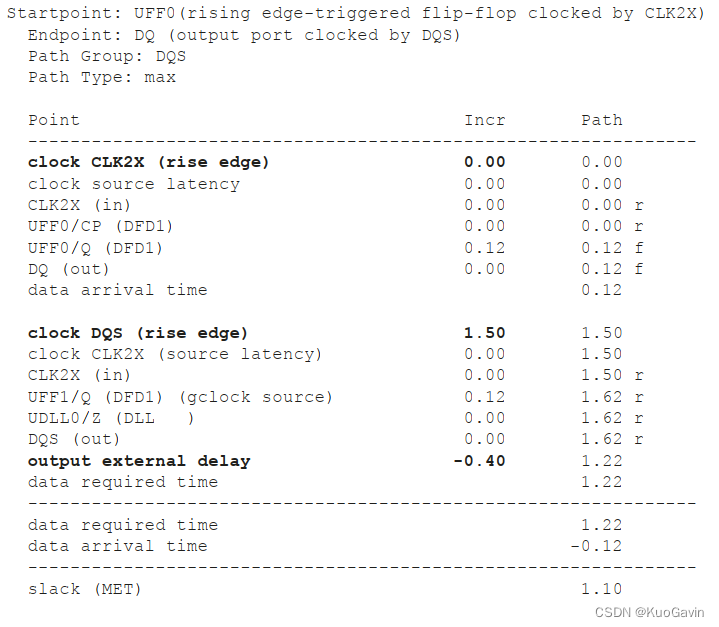

以下是通过输出

D

Q

DQ

DQ路径的建立时间检查报告。建立时间检查从

0

n

s

0ns

0ns处发起

D

Q

DQ

DQ的

C

L

K

2

X

CLK2X

CLK2X上升沿到

1.5

n

s

1.5ns

1.5ns处的

D

Q

S

DQS

DQS上升沿进行。

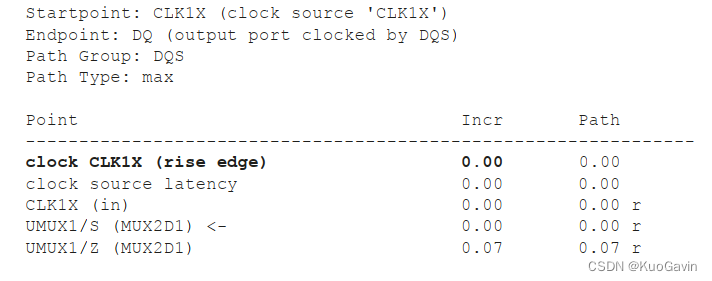

请注意,上述报告中的四分之一周期延迟出现在了时钟

D

Q

S

DQS

DQS上升沿的第一行中,而不是在

D

L

L

DLL

DLL实例

U

D

L

L

0

UDLL0

UDLL0的那行中。这是因为

D

L

L

DLL

DLL延迟已被建模为了衍生时钟

D

Q

S

DQS

DQS定义的一部分,而不是

D

L

L

DLL

DLL时序弧中的一部分。

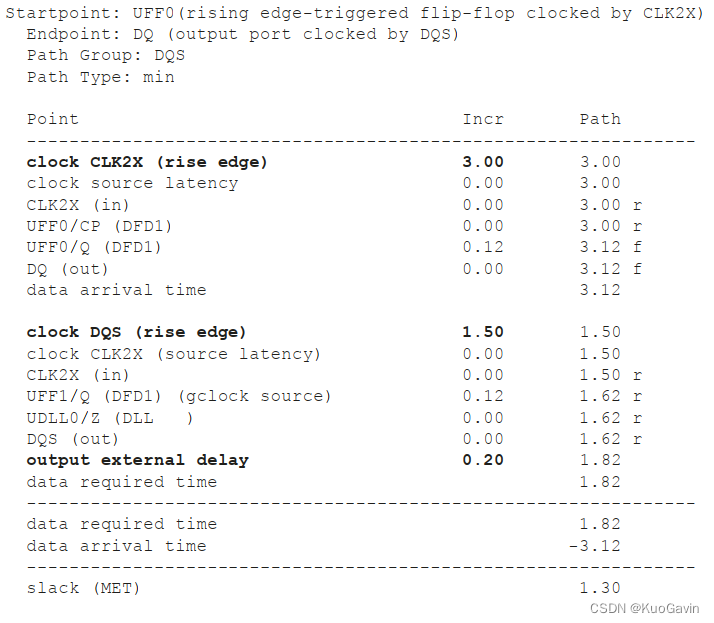

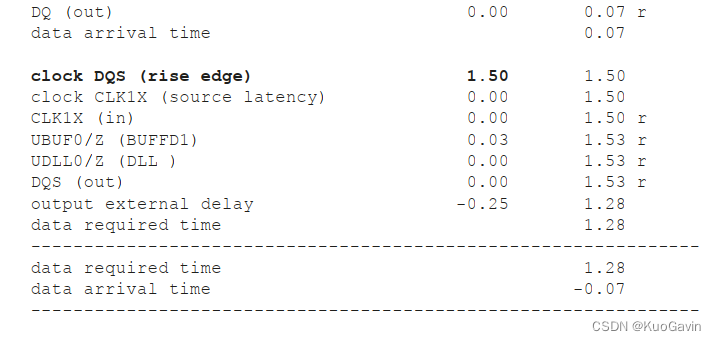

以下是通过输出

D

Q

DQ

DQ路径的保持时间检查报告。保持时间检查从

3

n

s

3ns

3ns处发起

D

Q

DQ

DQ的时钟

C

L

K

2

X

CLK2X

CLK2X上升沿到

1.5

n

s

1.5ns

1.5ns处的

D

Q

S

DQS

DQS前一个上升沿。

情况2:内部一倍频时钟(Case 2: Internal 1x Clock)

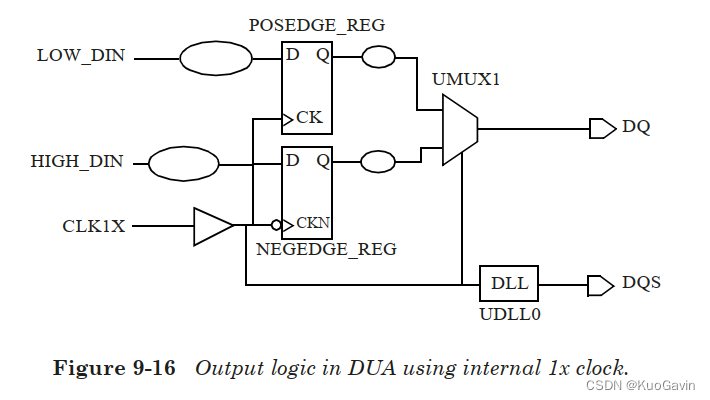

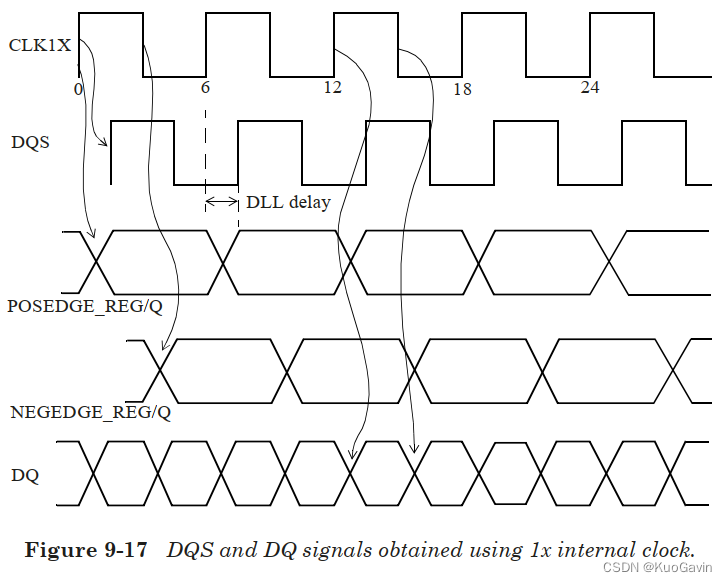

当内部只有一倍频时钟可用时,输出电路通常可能类似于图9-16所示的电路。

有两个触发器用于生成

D

Q

DQ

DQ数据:第一个触发器

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG由时钟

C

L

K

1

X

CLK1X

CLK1X的负沿触发,而第二个触发器

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG由时钟

C

L

K

1

X

CLK1X

CLK1X的正沿触发。每个触发器会锁存适当的边沿数据,然后使用

C

L

K

1

X

CLK1X

CLK1X作为多路复用器的选择信号来多路复用该数据:

C

L

K

1

X

CLK1X

CLK1X为高电平时,触发器

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG的输出发送到

D

Q

DQ

DQ;而当

C

L

K

1

X

CLK1X

CLK1X为低电平时,触发器

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG的输出发送到

D

Q

DQ

DQ。因此,数据会在时钟

C

L

K

1

X

CLK1X

CLK1X的两个边沿都到达输出

D

Q

DQ

DQ。请注意,每个触发器都有半个周期将数据传播到多路复用器的输入端,以确保在由

C

L

K

1

X

CLK1X

CLK1X边沿选择输入数据之前,已在多路复用器的输入端口上准备好了输入数据。相关波形如图9-17所示。

这种情况的输出延迟约束如下:

# Create the 1x clock:

create_clock -name CLK1X -period 6 [get_ports CLK1X]

# Define a generated clock at DQS. It is a divide-by-1 of

# CLK1X. Assume a quarter-cycle delay of 1.5ns on UDLL0:

create_generated_clock -name DQS -source CLK1X \

-edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

# Define a setup check of 0.25 and 0.3 between DQ and DQS

# pins on rising and falling edge of clock:

set_output_delay -max 0.25 -clock DQS [get_ports DQ]

set_output_delay -max 0.3 -clock DQS -clock_fall \

[get_ports DQ]

set_output_delay -min -0.2 -clock DQS [get_ports DQ]

set_output_delay -min -0.27 -clock DQS -clock_fall \

[get_ports DQ]

建立时间和保持时间检查可验证从多路复用器到输出的时序。建立时间检查之一是从多路复用器输入处的

C

L

K

1

X

CLK1X

CLK1X上升沿(发起

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG数据)到

D

Q

S

DQS

DQS的上升沿。另一个建立时间检查是从多路复用器输入处的

C

L

K

1

X

CLK1X

CLK1X下降沿(发起

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG数据)到

D

Q

S

DQS

DQS的下降沿。同样,保持时间检查是从(与建立时间检查)相同的

C

L

K

1

X

CLK1X

CLK1X边沿到

D

Q

S

DQS

DQS的前一个下降沿或上升沿。

以下是通过

D

Q

DQ

DQ端口的建立时间检查报告,该检查在(选择输出

N

E

G

E

D

G

E

_

R

E

G

NEGEDGE\_REG

NEGEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的上升沿之间进行。

这是通过

D

Q

DQ

DQ端口的另一个建立时间检查报告,该检查在(选择输出

P

O

S

E

D

G

E

_

R

E

G

POSEDGE\_REG

POSEDGE_REG的)

C

L

K

1

X

CLK1X

CLK1X的下降沿和

D

Q

S

DQS

DQS的下降沿之间进行。

这是通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

K

1

X

CLK1X

CLK1X的上升沿和

D

Q

S

DQS

DQS的前一个下降沿之间进行。

这是另一个通过

D

Q

DQ

DQ端口的保持时间检查报告,该检查在

C

L

K

1

X

CLK1X

CLK1X的下降沿和

D

Q

S

DQS

DQS的前一个上升沿之间进行。

尽管以上接口时序分析已忽略了任何负载对输出的影响,但我们也可以指定额外的负载(使用set_load命令)来提高准确性。

S

T

A

STA

STA同样可以通过电路仿真来补充,以实现可靠的

D

R

A

M

DRAM

DRAM时序。

D

D

R

DDR

DDR接口的

D

Q

DQ

DQ和

D

Q

S

DQS

DQS信号通常在读模式和写模式下使用终端电阻

O

D

T

ODT

ODT(On-Die Termination),以减少由于

D

R

A

M

DRAM

DRAM和

D

U

A

DUA

DUA处的阻抗不匹配而引起的任何反射(reflection)。在使用

O

D

T

ODT

ODT的情况下,用于

S

T

A

STA

STA的时序模型将无法提供足够的精度。设计人员可以使用另一种机制,例如详尽的电路级仿真,来验证信号完整性和

D

R

A

M

DRAM

DRAM接口的时序。

9.4 DAC接口(Interface to a Video DAC)

考虑下图9-18的一个典型

D

A

C

DAC

DAC接口,其中高速时钟将数据传输到

D

A

C

DAC

DAC的低速时钟接口。

时钟

D

A

C

_

C

L

K

DAC\_CLK

DAC_CLK是时钟

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK的

2

2

2分频,

D

A

C

DAC

DAC建立时间和保持时间检查针对的是

D

A

C

_

C

L

K

DAC\_CLK

DAC_CLK的下降沿。

在这种情况下,即使可以根据需要将从快时钟域到慢时钟域的接口指定为多周期路径,但也可以将建立时间视作单周期(

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK)路径。如图9-18所示,

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK的上升沿发起数据,而

D

A

C

_

C

L

K

DAC\_CLK

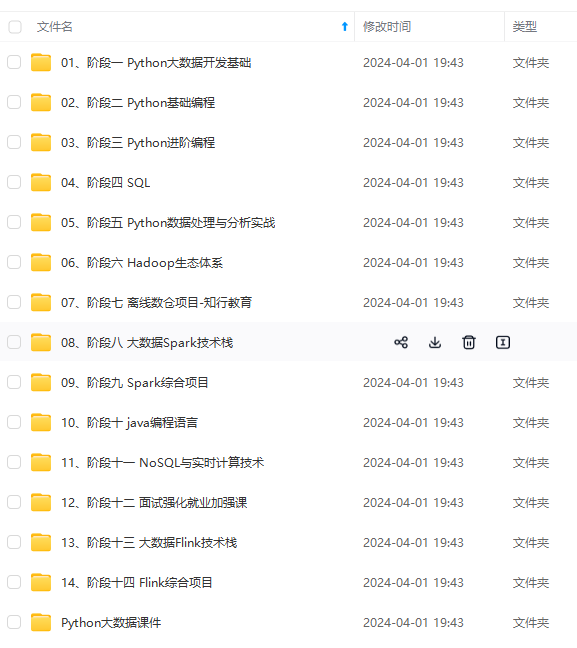

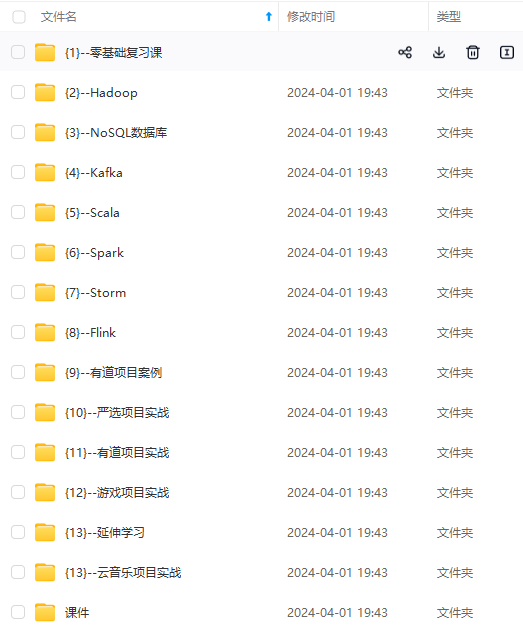

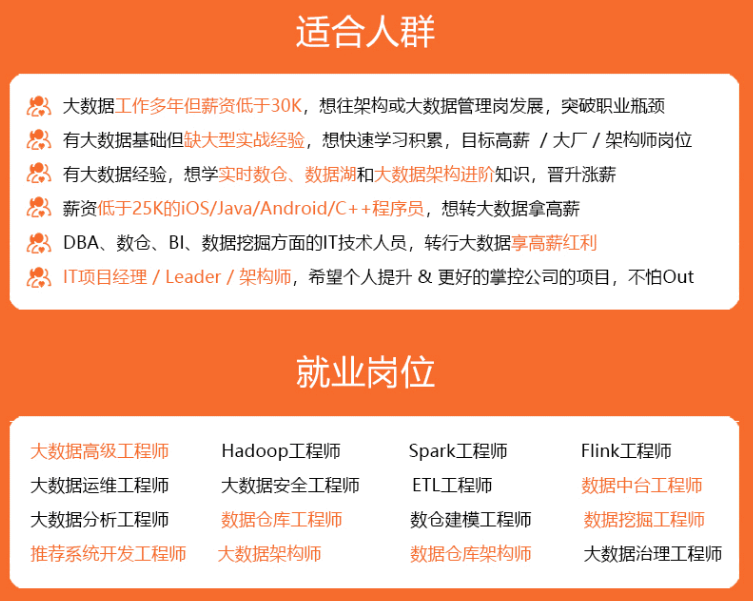

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

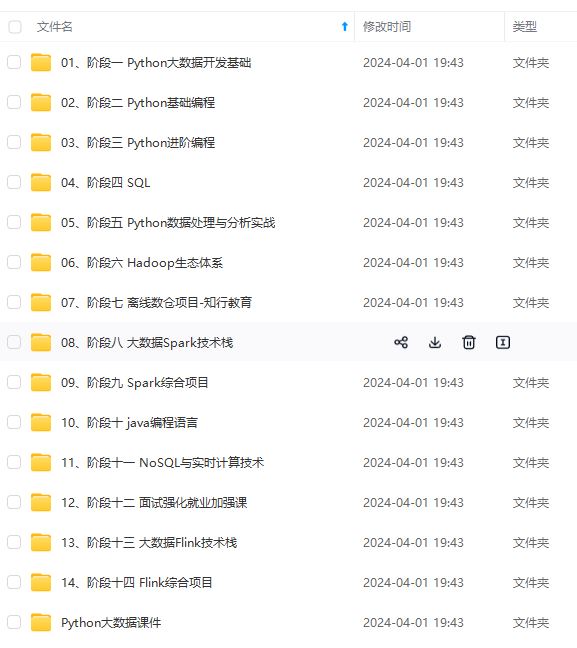

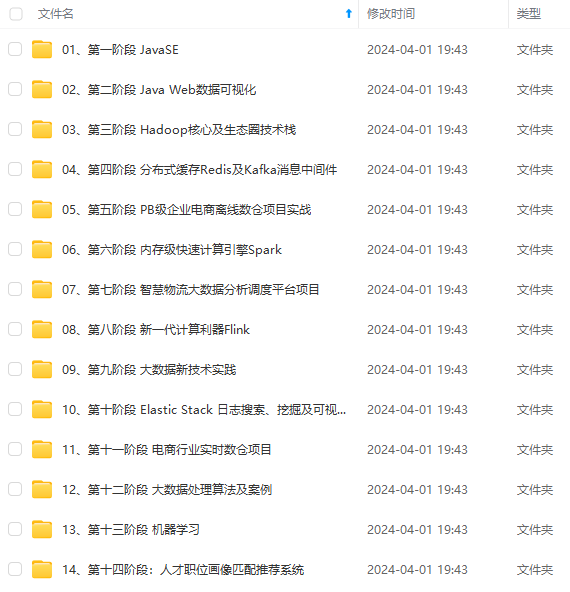

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

STA同样可以通过电路仿真来补充,以实现可靠的

D

R

A

M

DRAM

DRAM时序。

D

D

R

DDR

DDR接口的

D

Q

DQ

DQ和

D

Q

S

DQS

DQS信号通常在读模式和写模式下使用终端电阻

O

D

T

ODT

ODT(On-Die Termination),以减少由于

D

R

A

M

DRAM

DRAM和

D

U

A

DUA

DUA处的阻抗不匹配而引起的任何反射(reflection)。在使用

O

D

T

ODT

ODT的情况下,用于

S

T

A

STA

STA的时序模型将无法提供足够的精度。设计人员可以使用另一种机制,例如详尽的电路级仿真,来验证信号完整性和

D

R

A

M

DRAM

DRAM接口的时序。

9.4 DAC接口(Interface to a Video DAC)

考虑下图9-18的一个典型

D

A

C

DAC

DAC接口,其中高速时钟将数据传输到

D

A

C

DAC

DAC的低速时钟接口。

时钟

D

A

C

_

C

L

K

DAC\_CLK

DAC_CLK是时钟

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK的

2

2

2分频,

D

A

C

DAC

DAC建立时间和保持时间检查针对的是

D

A

C

_

C

L

K

DAC\_CLK

DAC_CLK的下降沿。

在这种情况下,即使可以根据需要将从快时钟域到慢时钟域的接口指定为多周期路径,但也可以将建立时间视作单周期(

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK)路径。如图9-18所示,

X

P

L

L

_

C

L

K

XPLL\_CLK

XPLL_CLK的上升沿发起数据,而

D

A

C

_

C

L

K

DAC\_CLK

[外链图片转存中…(img-kGdbV2T9-1715102734676)]

[外链图片转存中…(img-BL2IYB5f-1715102734676)]

[外链图片转存中…(img-6yovsJV1-1715102734677)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

981

981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?