数字电子钟计时系统设计——基于NE555与74系列芯片

基础要求:数码管实现从00:00:00到23:59:59的计时。

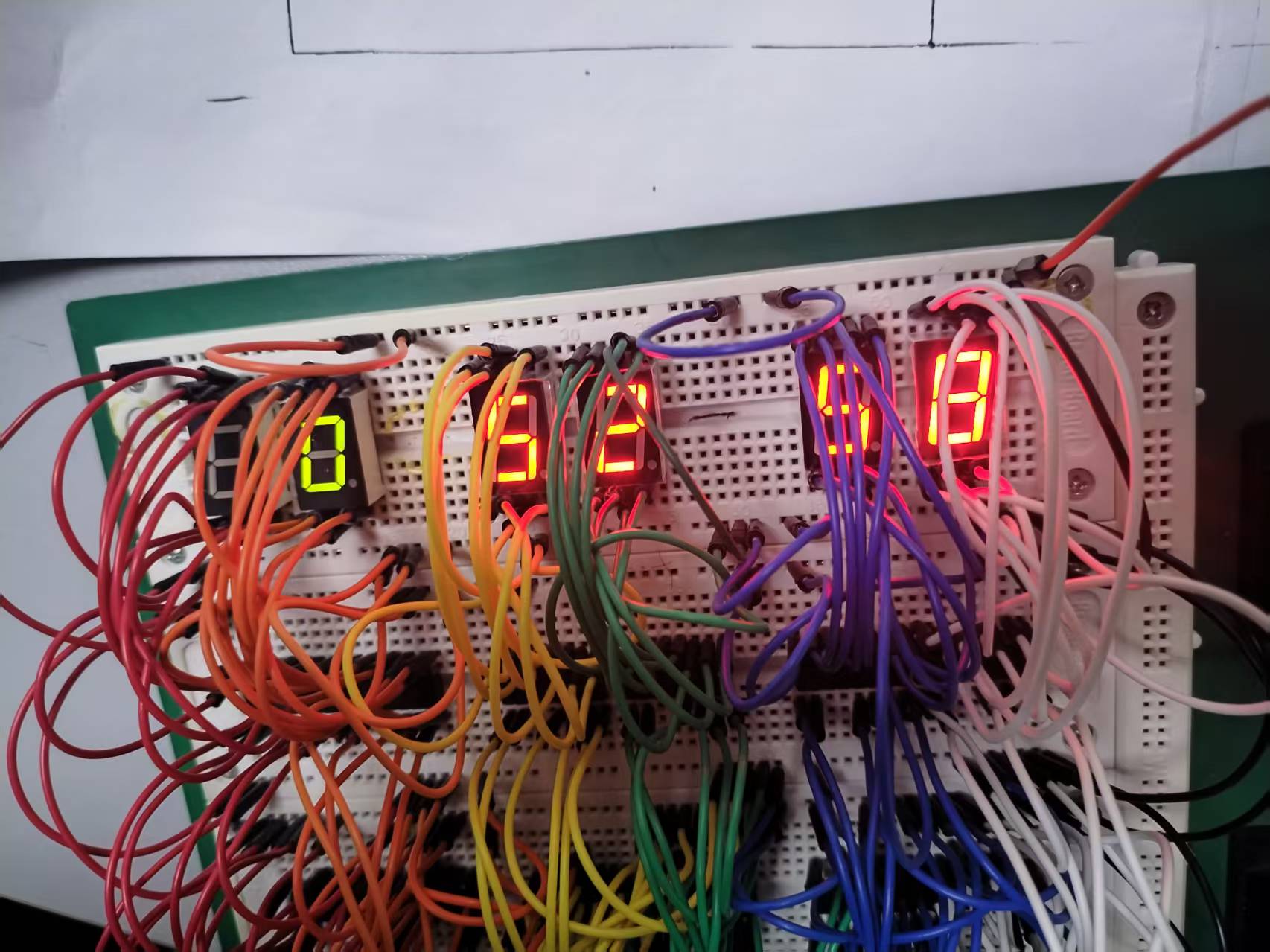

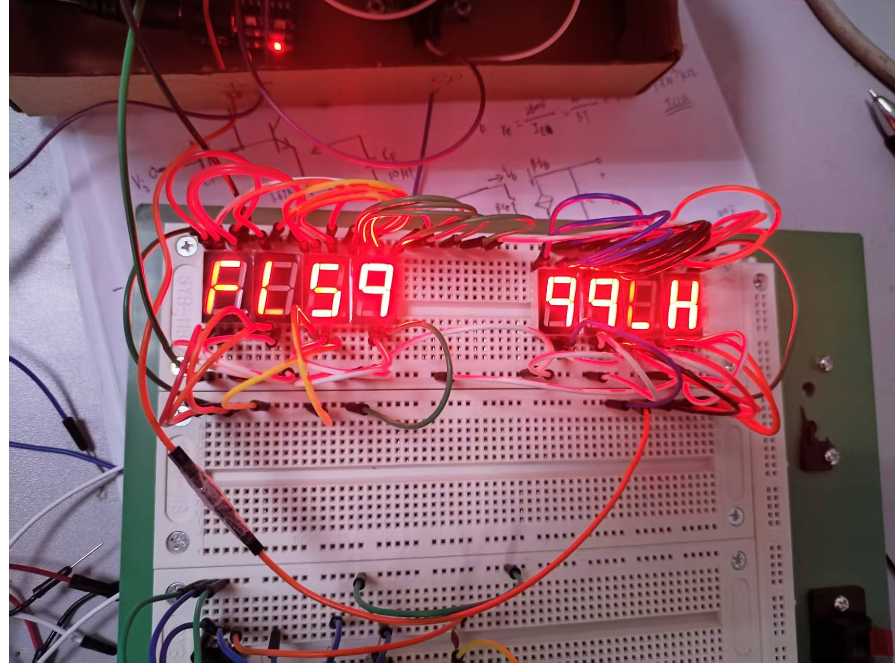

1、最终效果展示

数字电子钟计时系统设计——基于NE555与74系列芯片

2、具体方案

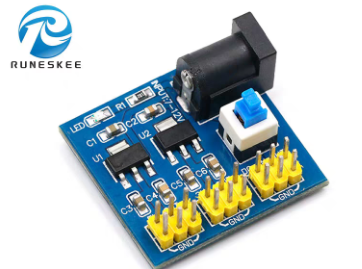

(1)5V电源

随便找个5V就可以(比如51单片机),我们当时选择的是供电模块。

!!!注意:购买时一定要选择【配线】

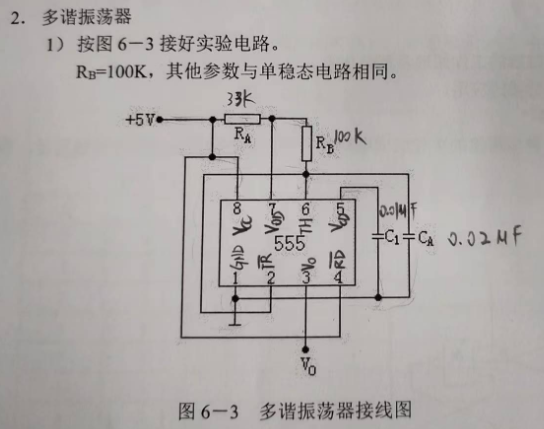

(2)时钟源(CP)设计方案

方案1:自己连接电路(电阻、电容大小用我图中标记的就可以)

(a)实际电路接线

(b)最终效果展示

NE55定时器产生矩形方波

其他方案

方案2:信号发生器

方案3:51单片机编程

方案4:NE555脉冲模块

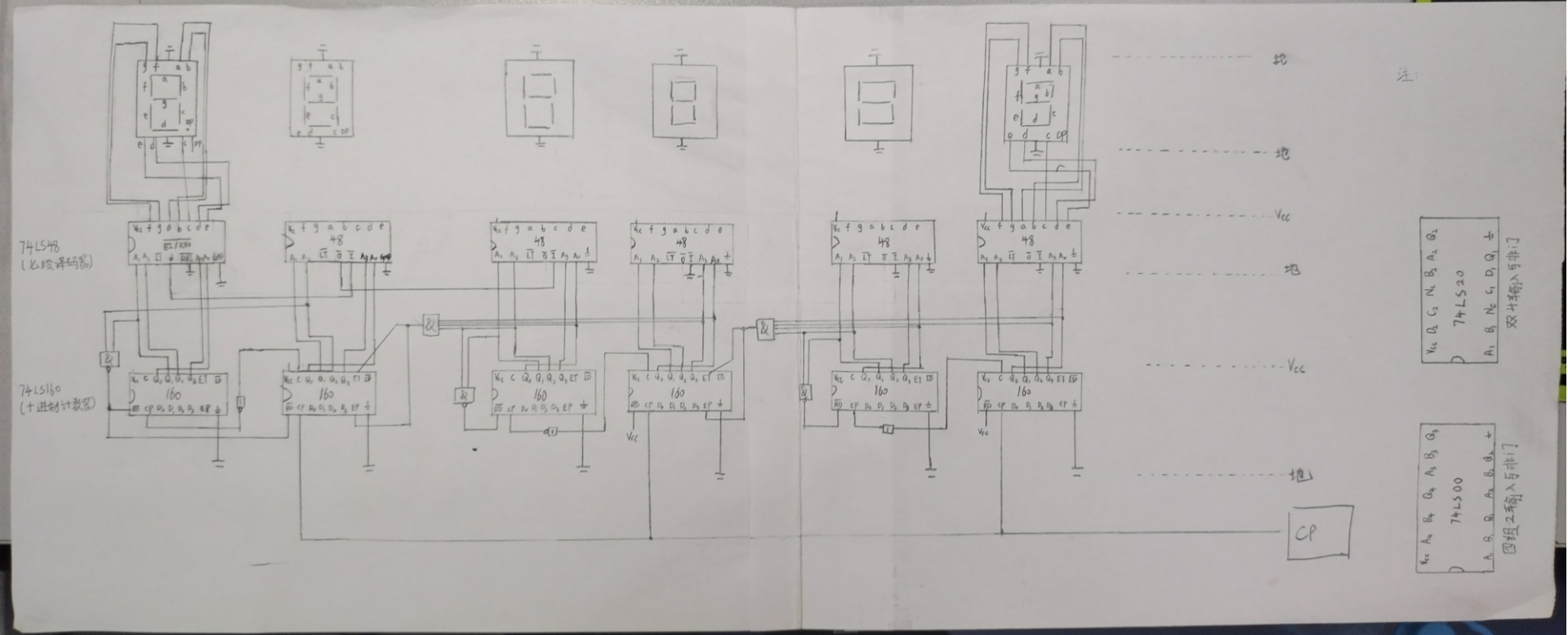

(3)主体电路设计

(a)手绘电路接线图

——电路接线图PDF下载链接:

注:

- CP ——时钟信号输入。

- 中间数码管的接线方式与两侧数码管相同,为简化电路图,未重复绘制。

- 为保持图纸整洁,VCC 和 GND 的连线仅在右侧用虚线标注,实际电路需按规范完整连接。

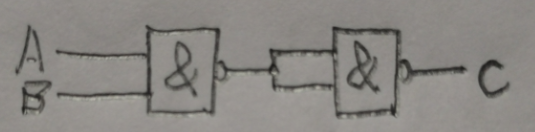

- 图中使用

与门和与非门,均以逻辑符号表示,未展示具体芯片接线。

与门的实现方式: 可以通过两个与非门级联 实现:

- 右下角提供了两种标准TTL与非门芯片:

74LS00(四路2输入与非门)74LS20(双路4输入与非门)

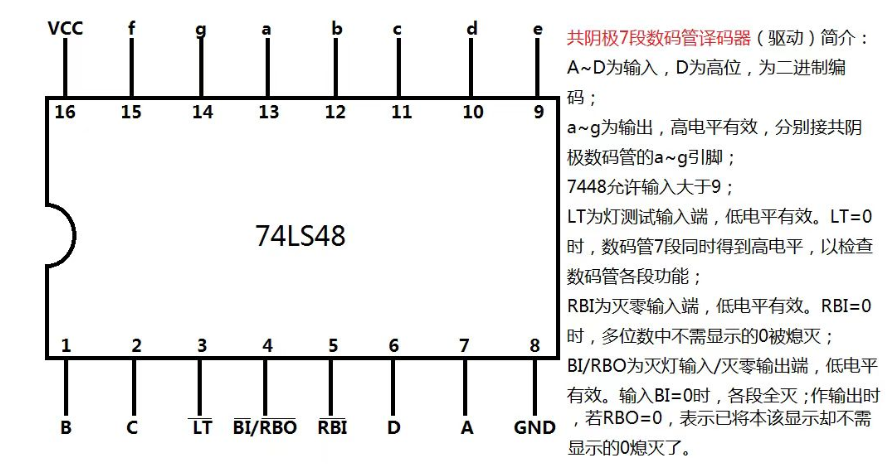

(b) 74LS48芯片(共阴极7段数码管译码器)讲解

- 理论与实际不符的地方

- 理论上,当

RBI = 0(低电平)且输入的 BCD 码为 0000(十进制 0) 时,74LS48会强制所有 7 段输(a-g)为 熄灭状态(即输出全高电平,数码管不显示)。也就是说,RBI仅对输入 0000(十进制 0)有效,对其他 BCD 码(0001~1001)无影响。 - 实践发现,

RBI引脚必须一直接GND,否则,不管输入的 BCD 码为何值,数码管都一直显示0。

- 理论上,当

74LS48的LT反引脚可以悬空(引脚悬空,默认为高电平)。

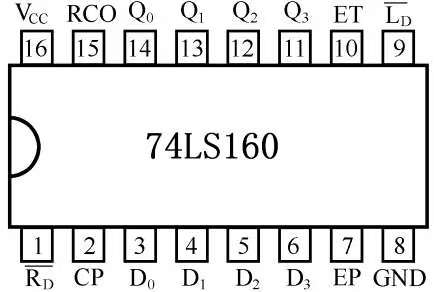

(c)74LS160芯片(十进制计数器)讲解

CP为时钟输入引脚。D0~D3为数据输入引脚,用于预置计数初值,在下一个CLK↑(上升沿 ),将D0~D3加载到计数器。LD反(全称Load, 低电平 有效),同步并行加载,当LD反 = 0时,下一个CLK↑将D0-D3加载到计数器。- 因为我们用的是 异步清零 方案,所以

D0~D3和LD反悬空即可(引脚悬空,默认为高电平)。 Q0-Q3为4 位 BCD 计数输出(0000~1001,即 0~9)。RD反为异步清零引脚,低电平有效,我们的电路图采用的就是异步清零方案。- 注意⚠️

RD反引脚在不使用时不可以悬空, 必须接VCC。(可以发现,电路图最右侧的74LS160的RD反引脚没有用到,所以接到了VCC)

- 注意⚠️

ET、EP为计数使能端,只有当EP=ET=1时,计数器才会在CLK↑时递增计数。这俩个引脚悬空即可(引脚悬空,默认为高电平)。RCO为进位输出引脚,当计数器达到1001(9)时,RCO引脚输出高电平,在下一个CLK↑又恢复到低电平,可用于级联扩展。RCO引脚也就是电路图中VCC引脚旁边的C引脚。- 那么

74LS160和74LS161有什么区别呢?74LS160为十进制计数器,而74LS161为十六进制计数器。

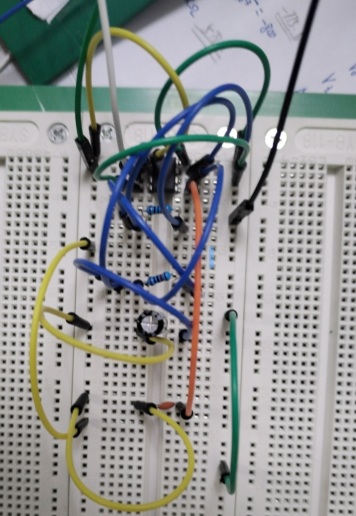

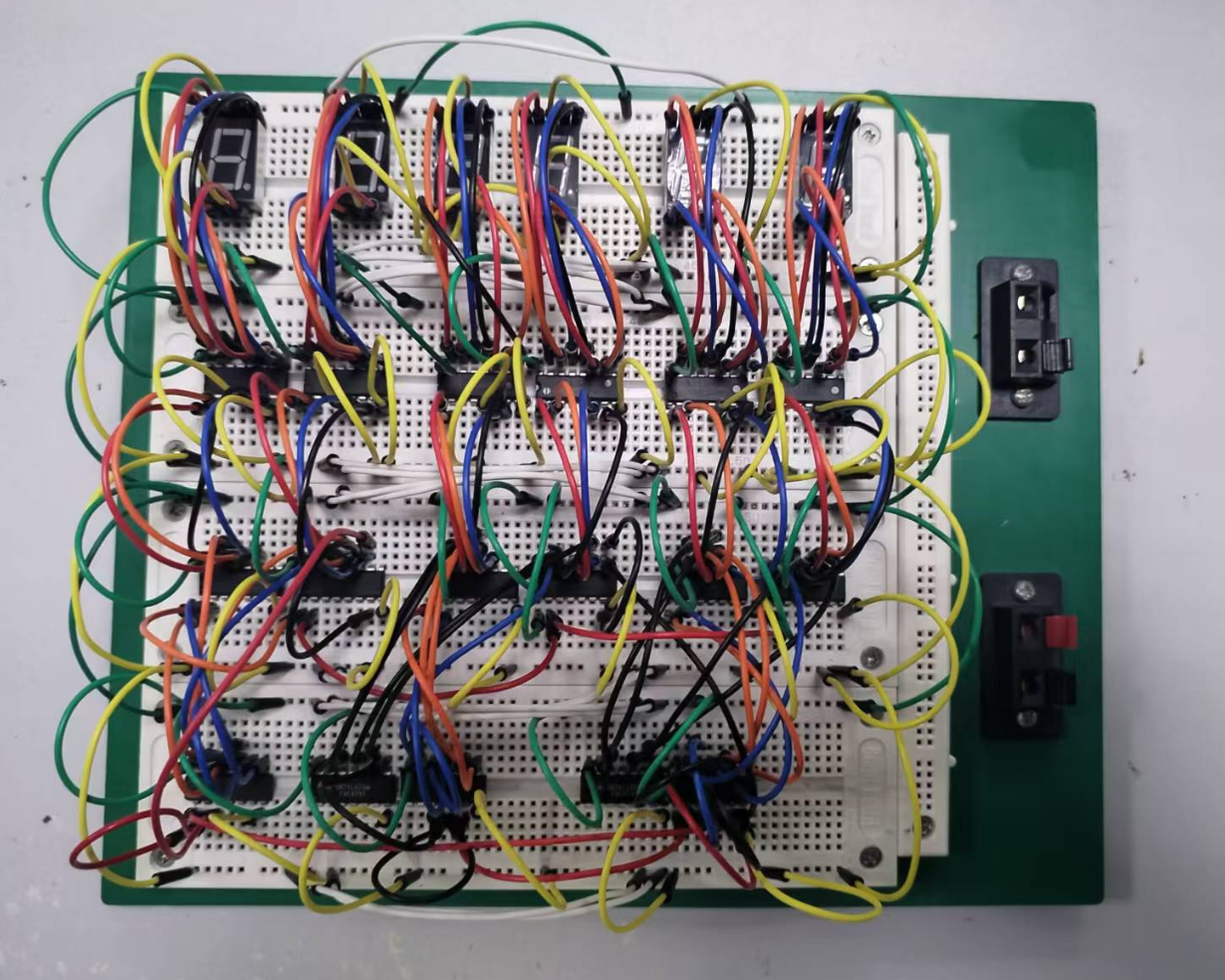

(d)实际接线图

当然我们也可以采用这种彩虹🌈接线方式:

3、其他

(1)先实现单个数码管计数

单个数码管计数

(2)如何快速进位?

将时钟线在需要进位的地方快速拔插

(3)玩转数码管

- 点亮数码管的任意段

点亮数码管

- 最后,我们点亮了八个数码管,前四个为字母“FLSQ”分别来自我们四个人的名字,后四个数码管为字母“qqLH”,也就是我们的团队名称“强强联合”

项目团队:强强联合

完成日期:2024-05-20-09:13。 😄正好过去一年了。

联系方式:CSDN私信@[锋狂]

🎯 使用小贴士

如果本博客对您的开发工作有帮助,欢迎:

点赞收藏 👍 让更多开发者看到

留言反馈 ✍️ 您的建议是我们改进的动力

关注更新 🔔 更多精彩内容、实用技巧

2564

2564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?