一、实验内容

1、数字电子钟以一昼夜24小时为一个计数周期。

2、具有“时”“分”、“秒”数字显示。

二、实验设计

1.555定时器

555定时器是一种集成电路,可以用来产生各种精确的时间延时和周期信号。555定时器可以用来实现各种功能,比如脉冲生成、频率分割、频率测量、频率调制、频率合成、脉冲宽度调制等。它常常被用在电子钟、计时器、脉冲发生器、电压控制振荡器等电路中。

它由三个主要部分组成:比较器,RS触发器和放大器。这个定时器可以根据外部电阻和电容的组合来实现不同的工作模式,比如单稳态、多稳态和振荡器。

多谐振荡电路:

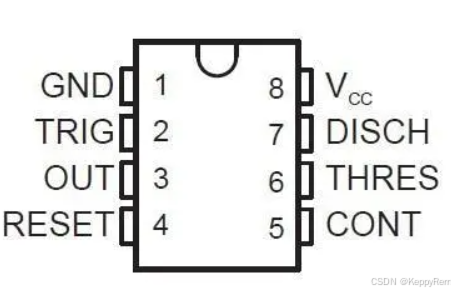

1.555定时器引脚图

- GND:接地。

- TRIG:触发引脚,用于控制定时器的启动。

- OUT:输出引脚,通过该引脚可以输出定时器的状态。

- RESET:复位引脚,用于重置定时器。

- CONT:连续引脚,用于控制定时器的工作模式。

- THRESHOLD:阈值引脚,用于控制定时器的阈值。

- DISCHARGE:放电引脚,用于控制定时器的放电。

- VCC:连接电源正极,通常为5V或12V。

2.多谐振荡电路图

充电时间:

放电时间:

振荡周期:

振荡频率:

占空比:

若占空比=2/3,频率为2KHZ,其中C=0.1微法,得R1=R2=2.35kΩ

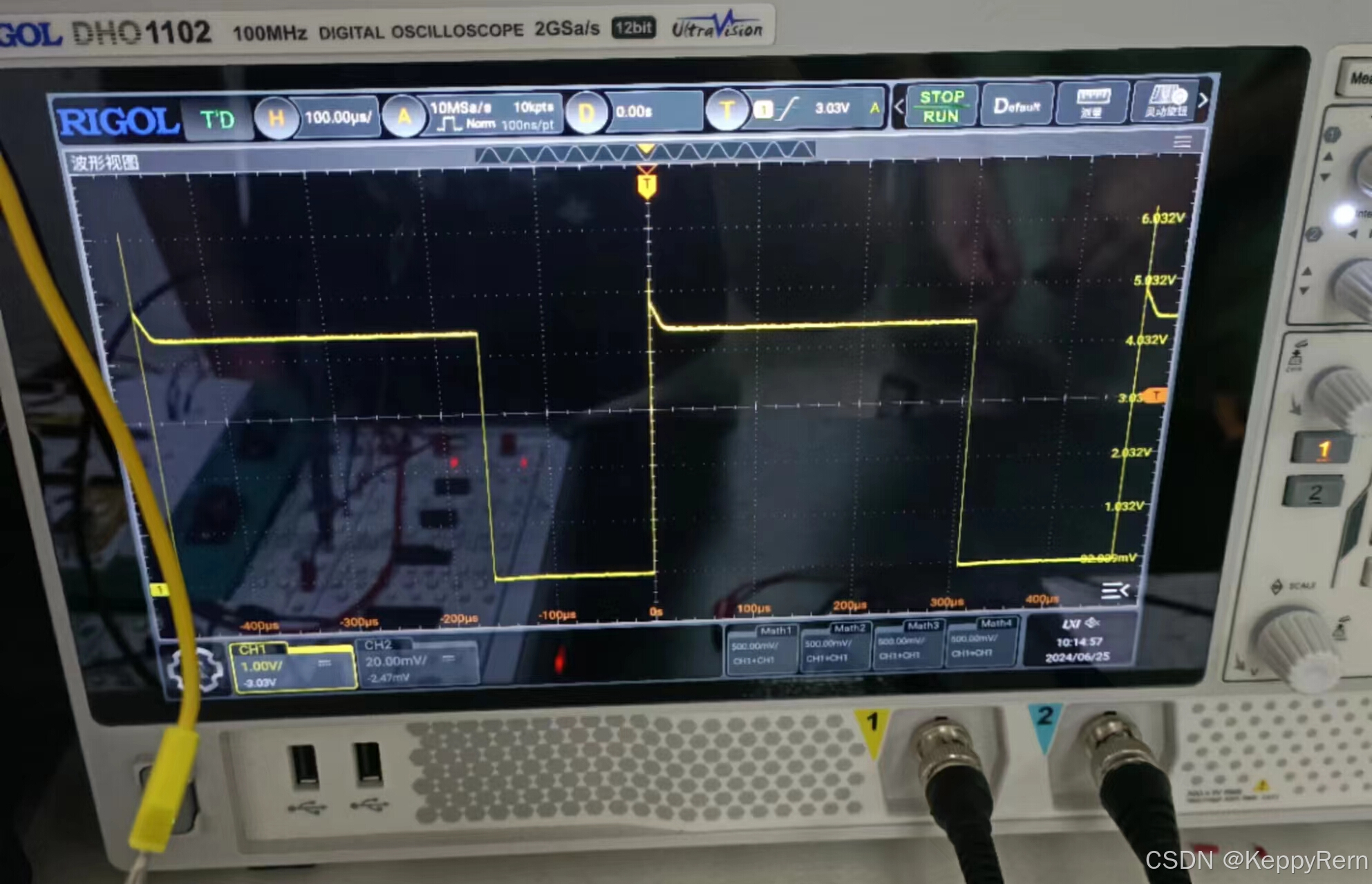

3.示波器显示

2.分频电路

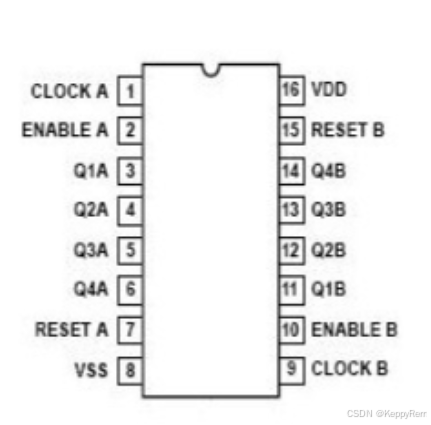

1.CC4518引脚图

- 1CP、2CP:时钟输入端。

- 1CR、2CR:清除端。

- 1EN、2EN:计数允许控制端。

- 1Q0~1Q3:计数器输出端。

- 2Q0~2Q3:计数器输出端。

- Vdd:正电源。

- Vss:地。

- RESET:清零端

(1)CC4518芯片是一种数字集成电路芯片,具有以下基础功能:

1. 逻辑门功能:CC4518芯片包含两个4位全加器,可以进行二进制数的加法运算。每个全加器包含两个输入端,一个进位输入端,两个输出端,分别用于计算两个二进制数的和和进位。

2. 加法器功能:CC4518芯片可以将两个二进制数相加,并输出其和和进位。通过将多个芯片级联,可以实现更长的二进制数加法运算。

3. 输入输出功能:CC4518芯片具有多个输入端和输出端,用于连接外部电路。输入端用于接收输入信号,输出端用于输出计算结果。

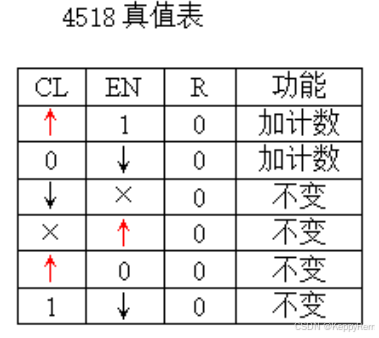

(2)CC4518是一个双BCD同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。

每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。

若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;

若用CLOCK信号上升沿触发,触发信号由CLOCK端输入,ENABLE端置“1”。

RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

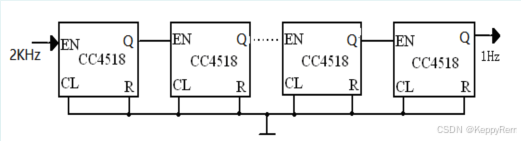

2.分频电路图

采用CC4518芯片进行分频,

上接用NE555产生的一个2KHz的脉冲,用CC4518进行四次分频(——进行3次十分频和1次二分频),使其频率达到1Hz。

3.计数

1.CC4518芯片

上述分频电路已提及,略。

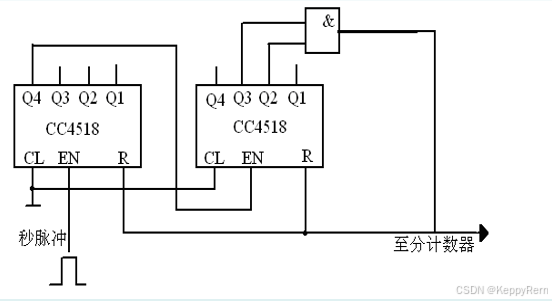

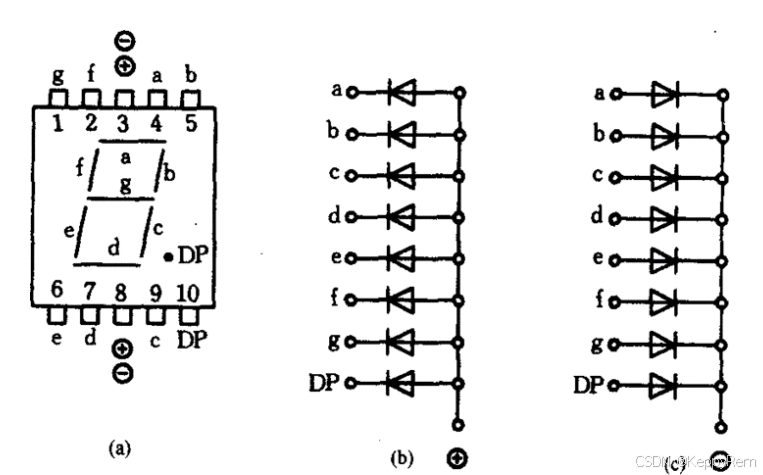

2.60进制

由于秒和分的显示均为60进制,因此它们可以由二级十进制计数器组成,其中秒和分的个位为十进制的计数器,十位为六进制的计数器,可采用反馈归零法来实现。

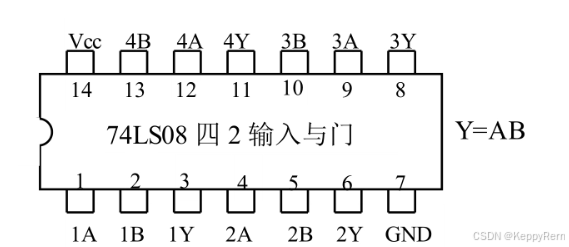

BCD码:Q4 Q3 Q2 Q1

0 1 1 0 (6)Q2 Q3 求& 输出Y=1,将“1”输入RESET端清零,实现60进制。

3.24进制

BCD码:Q4 Q3 Q2 Q1

0 0 1 0 (2)

0 1 0 0 (4)Q2 Q3 求& 输出Y=1,将“1”输入RESET端清零,实现24进制。

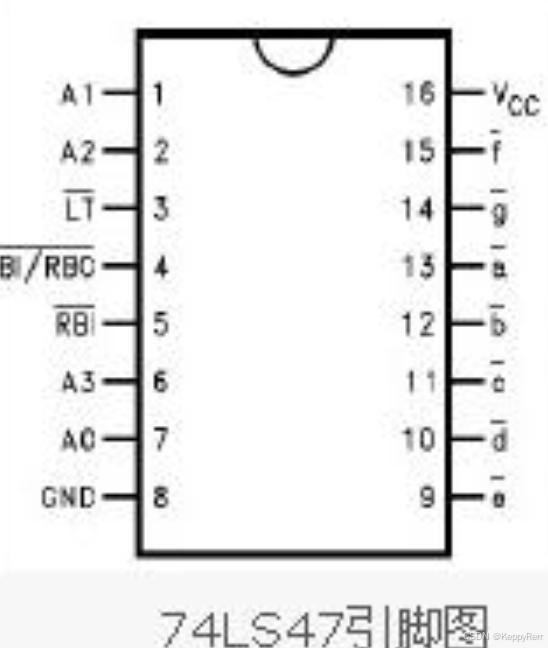

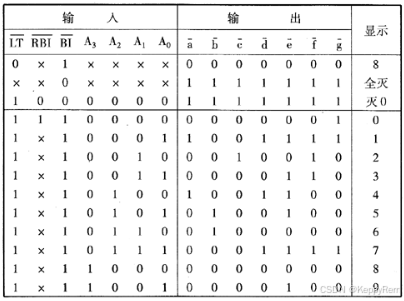

4.译码器

74LS47译码器引脚及功能图

74LS47是BCD-7 段数码管译码器驱动器,74LS47 的功能用于将BCD 码转化成数码块中的数字,通过它来进行解码,可以直接把数字转换为数码管的数字。

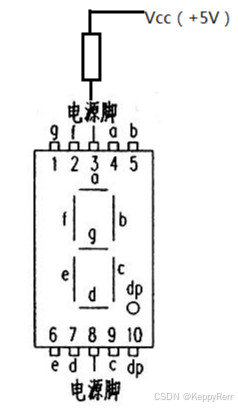

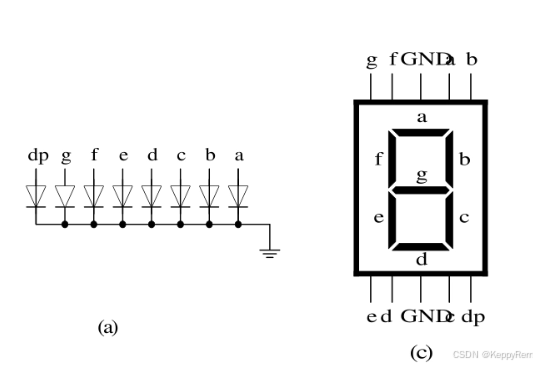

5. 显示—数码管

1.共阳极数码管

共阳极数码管阳极与Vcc连接,而每个数字段的阴极与输出引脚连接。当将对应的输出引脚拉高时,数字段就会被点亮。

2.共阴极数码管

共阴极数码管的共阴极与Vcc连接,而每个数字段的阳极分别与输出引脚连接。当将对应的输出引脚拉低时,数字段就会被点亮

6.与门—74LS08

引脚图

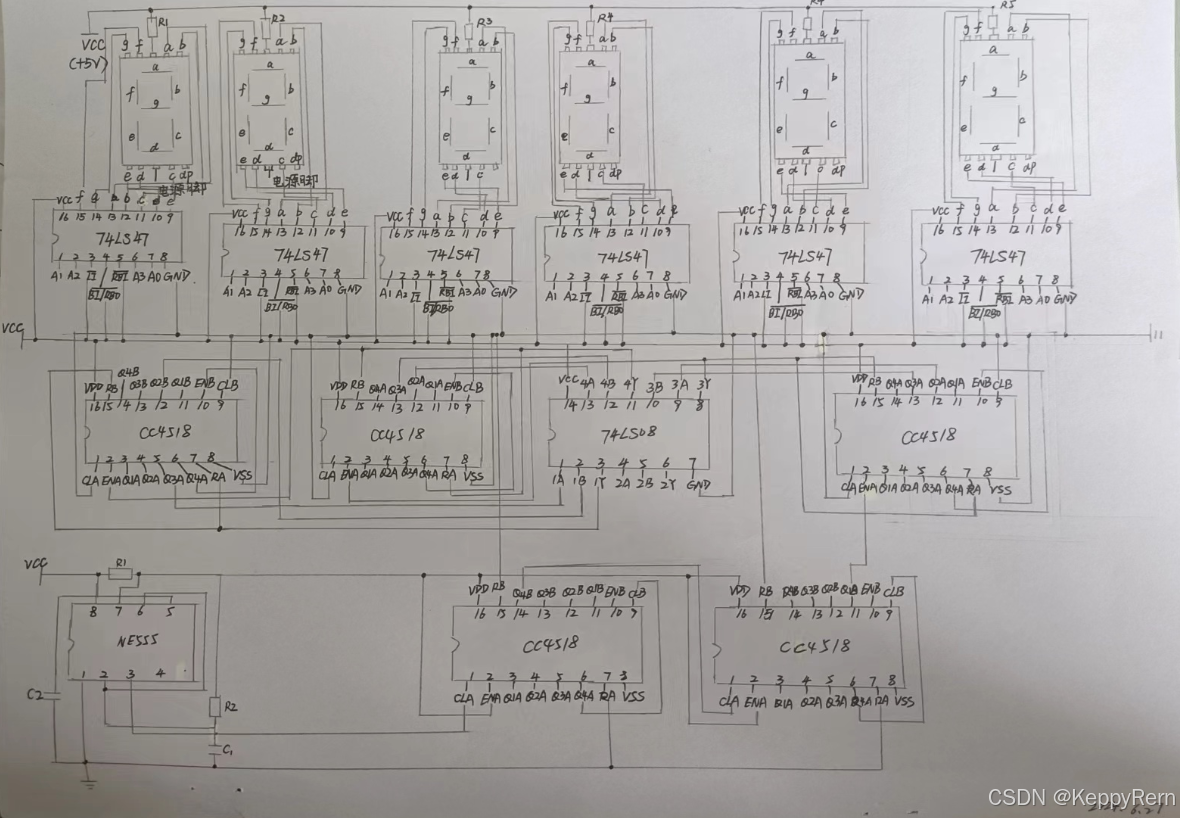

7.连接图

注:未连接CC4518与74LS47部分

3640

3640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?