既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

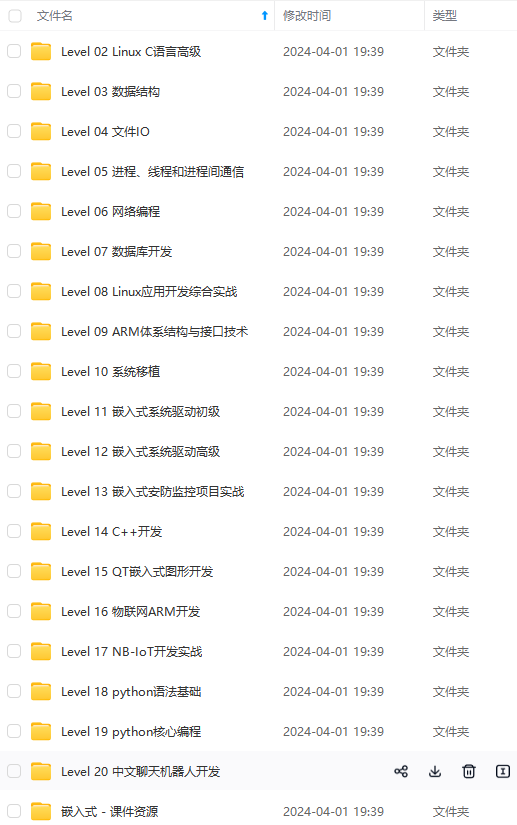

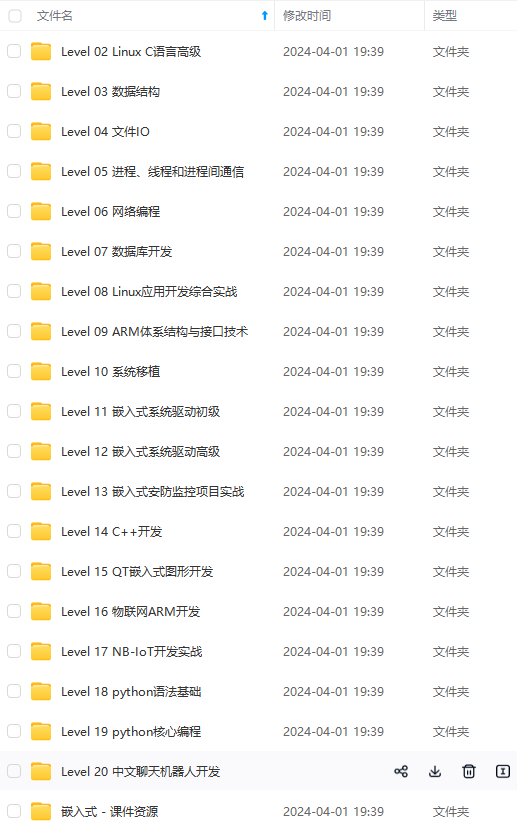

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

读信号(OE,即RD)

片选信号(CS)

若SRAM支持字节控制,还有UB/LB信号。

上一节提到的TFTLCD信号,RS、D0~D15、WR、RD、CS、RST和BL等

其中真正操作LCD时用到的就只有:

数据&命令:RS

数据线:D0~D15

写信号:WR

读信号:RD

片选信号:CS

操作时序和SRAM控制类似,唯一不同是TFTLCD有RS信号,但是没有地址信号

TFTLCD通过RS信号来决定传送是数据还是命令,可以理解为一个地址信号

将RS接到FSMC地址线A10(A0-A25随意),TFTLCD就被当做一个SRAM使用

这样TFTLCD成为只有一个地址的SRAM设备,从而实现FSMC驱动TFTLCD

三,FSMC存储块

STM32的FSMC支持8/16/32位数据宽度,我们使用的LCD为16位,所以设置选择16位

FSMC的外部设备地址映像:STM32的FSMC将外部存储器划分为固定大小为256M字节的四个存储块

如图:

FSMC分为4块,每块256M字节又被划分为4*64,即四个片选

NOR / PSRAM使用块1,共256M

NAND闪存使用块2,3,共512M

PC卡使用块4,共256M

所以我们使用NOR PSRAM驱动TFTLCD

四,存储块1(Bank1)寄存器介绍

STM32的FSMC存储块1(Bank1)用于驱动NOR FLASH/SRAM/PSRAM

Bank1被分为4个区,每个区管理64M字节空间,每个区都有独立的寄存器对所连接的存储器进行配置。

Bank1的256M字节空间由28根地址线(HADDR[27:0])寻址。 这里HADDR,是内部AHB地址总线

HADDR[25:0]来自外部存储器地址FSMC_A[25:0],而HADDR[26:27]对4个区进行寻址。

如下图所示:

说明:

HADDR[27:26]是不可手动配置的,当选择所在区后会自动赋值

注意:

1,当Bank1接 8位宽度存储器时:HADDR[25:0] -> FSMC_A[25:0]

2,当Bank1接16位宽度存储器时:HADDR[25:1] -> FSMC_A[24:0]

由于内部每个地址对应一个字节,外部设备16位宽,FSMC的一个地址对应两个字节

即:

0000对应FSMC_A[0]=0 (2字节)

0010对应FSMC_A[0]=1 (2字节)

0100对应FSMC_A[1]=1 (2字节)

所以对应关系需要除以2,内部右移一位对齐

此时最低位没用,访问最低位需要使用UB/LB

不论外部接8位/16位宽设备,FSMC_A[0]永远接在外部设备地址A[0]

五,存储块1(Bank1)模式A读写时序

STM32的FSMC存储块1支持的异步突发访问模式

包括模式1,模式A~D等多种时序模型,驱动SRAM一般使用模式1或模式A

我们使用模式A驱动LCD(当做SRAM使用),模式A支持读写时序分开设置

上一篇说的LCD时序,我们知道,LCD的读写耗时是不同的.写快读慢

这里采用模式A,针对不同的速度,做不同的设置

模式A读时序:

模式A写时序:

ILI9341时序-读写高低电平最小持续时间:

根据ILI9341时序读写高低电平最小持续时间来配置模式A的读写时序

六,FSMC相关寄存器介绍

对于NOR FLASH/PSRAM控制器-存储块1,可通过FSMC_BCRx、FSMC_BTRx和FSMC_BWTRx寄存器设置(其中x=1~4,对应4个区)。

通过这3个寄存器,可以设置FSMC访问外部存储器的时序参数,拓宽了可选用的外部存储器的速度范围。

1,SRAM/NOR闪存片选控制寄存器(FSMC_BCRx)

FSMC_BCRx

EXTMOD:

扩展模式使能位,控制是否允许读写不同的时序,需设置为1

WREN:

写使能位。我们要向TFTLCD写数据,需设置为1

MWID[1:0]:

存储器数据总线宽度。00,表示8位数据模式;01表示16位数据模式;10和11保留。

我们的TFTLCD是16位数据线,需设置WMID[1:0]=01。

MTYP[1:0]:

存储器类型。00表示SRAM、ROM;01表示PSRAM;10表示NOR FLASH;11保留。

我们把LCD当成SRAM用,需设置MTYP[1:0]=00。

MBKEN:

存储块使能位。需设置为1

2,SRAM/NOR闪存片选时序寄存器(FSMC_BTRx)-读时序控制

FSMC_BTRx

ACCMOD[1:0]:

访问模式。00:模式A;01:模式B;10:模式C;11:模式D。

我们使用模式A,需设置为00

DATAST[7:0]:

数据保持时间,等于: DATAST(+1)个HCLK时钟周期,DATAST最大为255。

对于ILI9341相当于RD低电平持续时间,最大355ns

对于STM32F1,一个HCLK=13.8ns (1/72M),设置为15,相当于16个HCLK=220.8,加上STM32F1的FSMC性能较低一些,配置为15即可

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

-1715874806422)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

5452

5452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?