基于开关轨迹优化的SiC MOSFET 有源驱动电路研究综述

王 宁 张建忠

(东南大学电气工程学院 南京 210096)

摘要 随着 SiC MOSFET 的推广,其开关暂态过程中的超调、振荡以及电磁干扰问题越来越受到人们的重视。有源栅极驱动(AGD)电路作为一种新型驱动电路,已被广泛应用于 SiC MOSFET开关轨迹的优化控制。首先,该文分析 AGD 电路的工作原理,给出不同驱动参数对开关特性的影响;其次,着重探讨阈值触发型 AGD 电路的工作模式,分别从暂态定位技术、逻辑处理架构和功率放大拓扑三方面对 AGD 电路进行归纳总结,并评价不同技术的优缺点,给出 AGD 电路设计的建议流程;最后,展望基于 SiC MOSFET 开关轨迹优化的 AGD 电路的发展趋势。

引言

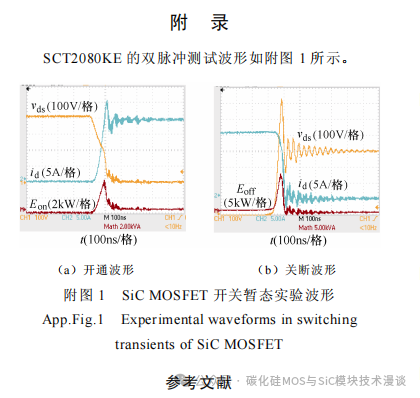

以碳化硅金属氧化物半导体场效应晶体管(Silicon Carbide Metal Oxide Semiconductor FieldEffect Transistor, SiC MOSFET)为代表的宽禁带半导体器件的诞生和发展使电力电子技术迎来了新的发展,和传统的 Si 基器件相比,在静态特性方面,SiC MOSFET 具有更低的导通电阻、更高的热导率以及能与 IGBT 媲美的功率等级;在动态特性方面,SiC MOSFET 则具备更快的开关速度及频率上限,这有助于电力电子装置整体功率密度及效率的提升[1]。然而,开关瞬态过程的高 dv/dt、di/dt 以及与之相伴的超调振荡使得 SiC MOSFET 完全取代 Si IGBT 仍然受到一些限制。附录给出了 ROHM 公司推出的SiC MOSFET 产品 SCT2080KE 在 400V、20A 工作条件下的双脉冲测试波形,实验结果体现出宽禁带器件高速开关暂态的局限性,具体表现为:

一方面,开关暂态有逾越安全工作区的风险。虽然 SiC 肖特基二极管消除了 Si 二极管的反向恢复效应,但是较大结电容使得开通过程仍存在较大的电流超调;SiC MOSFET 的结电容更小,对于回路寄生电感更加敏感,特别是在器件关断时会产生较大的关断电压尖峰与持续振荡,极易突破器件的额定工作值,造成不可逆转的失效[2]。

另一方面,串扰问题值得注意。半桥电路中桥臂中点电位的瞬变通过结电容形成位移电流,与回路寄生电感与栅极驱动电阻相作用,形成电压尖峰。由于 SiC 器件具有更低的开通阈值,正向串扰增大了桥臂直通的风险;同时 SiC 可承受负关断电压绝对值更低,负向串扰会造成器件的损坏[3]。

SiC MOSFET 对于开关损耗更加敏感。更快的开关速度使得 SiC MOSFET 电压、电流交叠区域更小,开关损耗更低,但在高频驱动的情况下,单次开通或者关断损耗的提升可能会显著降低系统效率,引发散热不良、器件失效等问题[4-5]。

电磁兼容问题是当下危害电力电子系统的重要问题之一[6-7]。电力电子装置中的半导体器件的高频、高速切换是电磁噪声的源头;而复杂的寄生参数网络为骚扰信号提供了路径。电磁干扰(Electromagnetic Interference, EMI)不仅以泄露电流、轴电流的形式在功率回路形成安全隐患;同时对于控制侧模拟电路、数字电路形成较强的干扰,降低系统运行的可靠性。

优化 PCB 布局、降低回路寄生电感被证实是一种有效缓解上述问题的方式,但其非常依赖于设计人员的经验,同时为进一步降低寄生参数需要复杂的先进封装技术[8],成本昂贵。增设滤波器、吸收电路等手段都是以增加额外损耗、牺牲系统功率密度为代价的,并且往往需要进行反复的试错实验,大大降低了研发效率。

有源栅极驱动(Active Gate Driver, AGD)作为一种新型驱动电路,通过附加有源器件,调节驱动部件参数,以达到优化开关特性的目的。AGD 技术最早被应用于 IGBT 驱动中,主要有损耗降低[9]、串扰抑制[10]、串联均压[11]、并联均流[12]、有源钳位[13]、短路保护[14]和暂态轨迹优化 7个用途。SiC MOSFET相对于 Si IGBT 开关速度更快,所带来的超调、振荡、EMI 问题更加显著,如何在不显著增加开关损耗的情况下,通过降低开关速度来优化开关轨迹,是本文 AGD 电路应用的目的。

本文根据现有文献,从工作原理、控制手段、电路拓扑等方面出发,归纳整理了针对 SiC MOSFET轨迹优化的 AGD 电路相关技术,并在性能方面进行了对比,给出 AGD 建议的设计流程,最后讨论了未来 AGD 电路发展的趋势。

1 AGD 工作原理

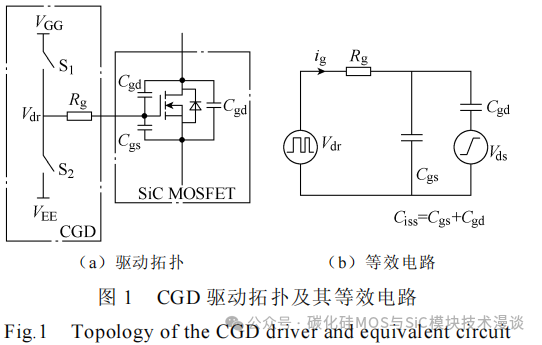

常规栅极驱动(Conventional Gate Driver, CGD)拓扑及其等效电路如图 1 所示,SiC MOSFET 的开关暂态实际为对输入电容的充放电过程。图 1 中,VGG 为正驱动电压,VEE 为负驱动电压,S1 和 S2 为驱动开关,Vdr 为驱动输出电压,Rg 为栅极驱动电阻,Cgs 为栅源电容,Cgd 为栅漏电容,Cds 为漏源电容,Vds 为漏源电压,Vgs 为栅源电压,ig 为栅极电流,id为漏极电流。SiC MOSFET 的开关轨迹有 7 个基本的特征参量,分别为开关延时 tdelay、漏源电压变化率 dv/dt、漏极电流变化率 di/dt、电流超调量 Ios、电压超调量 Vos、EMI 水平及开关损耗 Psw。

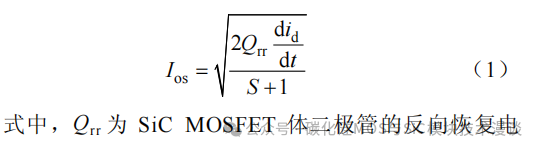

对于 SiC MOSFET 而言,开关过程中的高电流变化率 did/dt 是危害器件可靠工作的主要原因[15],具体表现为:在开通过程中,高速电流切换恶化了SiC MOSFET 体二极管的反向恢复效应,额外的电流应力不仅增加了器件的开通损耗,并且电流尖峰也会以差模 EMI 的形式降低系统电磁兼容特性。SiC MOSFET 的开通电流超调量 Ios 可表示为

荷;S 为反向恢复软度。在关断过程中,由于回路寄生电感 Lloop 无法静态储能,高电流变化率会与之作用产生较高的尖峰电压。电压超调量不仅增大了器件的关断损耗,同时也增加了器件击穿的可能,并且系统的共模 EMI特性也随之恶化。SiC MOSFET 电压超调量表示为

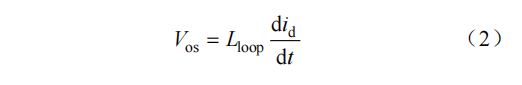

调节 CGD 电路中驱动电压 Vdr、驱动电阻 Rg、栅源电容 Cgs 等栅极部件的数值可以实现对于漏极电流变化率的调控,SiC MOSFET 的电流变化率可近似为

式中,gfs 为 SiC MOSFET 的电导;VTH 为开通阈值电压;Vmil 为米勒平台电压;Ls 为器件源极电感。

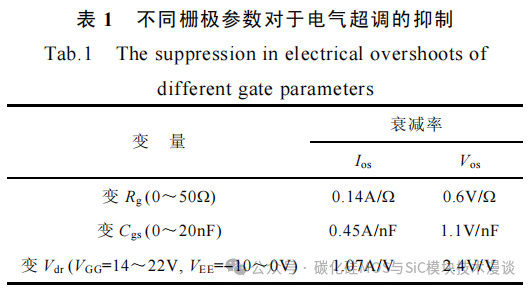

由式(3)和式(4)可以看出,增大 Rg、Cgs以及降低 Vdr 可以有效降低 did/dt 的数值,进而实现电流、电压超调的抑制。根据文献[16]的实验结果,栅极部件参数对于 SiC MOSFET 开通电流超调抑制和关断电压超调抑制效果见表 1[16]。在单位步长变化条件下,变 Vdr 对于电气超调量的抑制效果更为明显。

然而,人为地在设计初期调整驱动部件参数,降低 SiC MOSFET 开关速度虽然可以降低超调、振荡和 EMI 等开关暂态负面效应,但随之带来的开关延时上升和开关损耗增加却不能忽视。

过长的开关延时一方面会增加环路的响应时延;另一方面 SiC MOSFET 的开关速度直接关乎死区时间的设定,一味调节栅极驱动参数都是以牺牲变换器控制性能为代价的。同时,SiC MOSFET 的开关损耗被定义为漏极电流 id 和漏源电压 vds 的交叠面积,降低器件开关速度是以牺牲开关损耗、降低系统效率以及增加散热负担为代价的。SiC MOSFET的开关损耗表达式可表示为

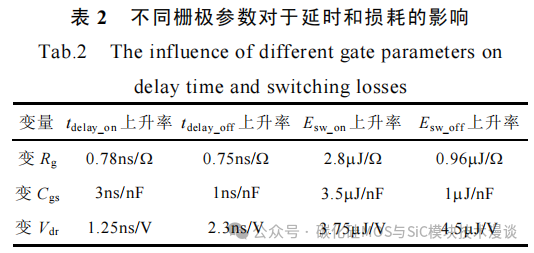

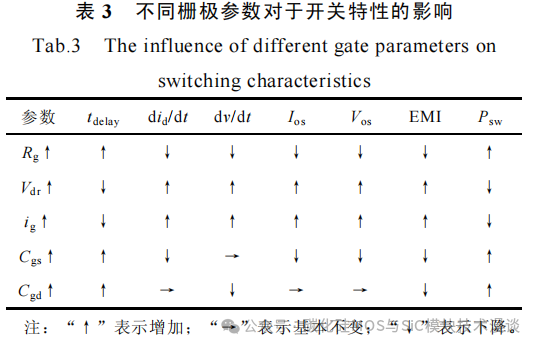

不同栅极参数对于延时和损耗的影响见表 2。表 2 给出了和表 1 相同参数变化范围内,文献[16]结果中,调节栅极部件对于开关延时以及开关损耗的影响。显然,CGD 中一旦设定好了栅极驱动部件参数值,那么 SiC MOSFET 开关轨迹就基本固定,CGD 电路灵活性的缺乏导致了其很难兼顾开关损耗和超调抑制效果。表 3 给出了不同栅极参数对于开关特性的影响趋势。

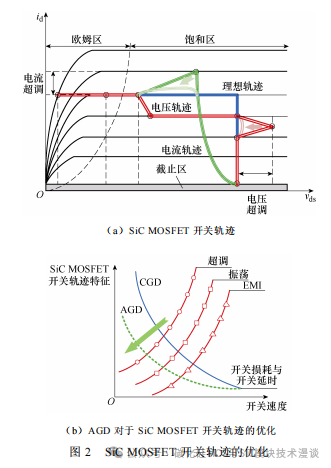

针对以上问题,AGD 可以通过其特有的暂态定位功能,有针对性地调整某一暂态瞬间的某一栅极部件,只降低该阶段的开关速度,进而在不明显增加开关延时和总开关损耗的情况下,将开关瞬态的负面效应降到容许的程度。相对于传统 CGD 电路,AGD 可以更有选择性地调节 SiC MOSFET 的开关轨迹,灵活度更高。SiC MOSFET 开关轨迹的优化如图 2 所示。

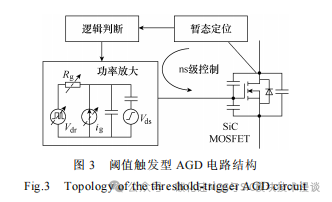

基于 IGBT 的 AGD 电路分为开环型、全闭环型和阈值触发型三种控制模式。开环型[17-18]不存在反馈通路,直接在驱动电路前向通道上切换驱动参数,控制简单、响应快,缺点是受限于器件模型的精确性,不能适应电力电子装置工作点以及工作环境的变化。全闭环型[19]指实时采样功率器件的电压、电流信息,通常使用高带宽模拟 PI 调节器对器件的动态轨迹进行全闭环调节,该方法对于器件的控制自由度最高,但是受限于响应速度与成本。阈值触发型,又称“离散时间反馈型[20]”,是一种介于前两者之间的控制方式。通过采样反馈,当器件电压、电流等电气量超过某一阈值时,则会触发响应,通过逻辑判断,给出切换驱动部件参数的指令,以达到优化开关轨迹的目的。IGBT 开关速度为μs 级,而 SiC MOSFET 为 ns 级,全闭环调节方式很难追踪其暂态开关轨迹。目前,阈值触发型 AGD 是应用最广的 SiC MOSFET 有源栅极驱动电路,被广泛用于抑制 SiC MOSFET 开关瞬态的超调、振荡及EMI 问题。

阈值触发型 AGD 电路结构如图 3 所示,暂态定位、逻辑判断、功率放大为基于开关轨迹优化的SiC MOSFET 有源驱动所必须的三个基本模块电路。三个模块电路的组成形式与实现功能有所差异,在数十 ns 级的尺度下,共同完成了对于 SiC MOSFET某一开关暂态的某一驱动部件参数的调节。从电路设计的角度出发,基于现有文献,本文分别对三个模块电路的设计思路与相关技术进行了对比与总结。

2 AGD 的暂态定位模块

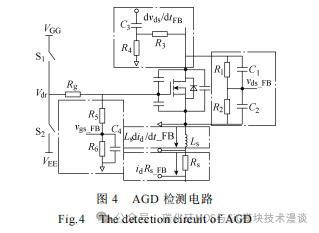

SiC MOSFET 的开关瞬态主要分为开关延迟、电压变化、电流变化三个阶段。AGD 电路可以实现对 SiC MOSFET 开关暂态瞬间较为精准的定位,这得益于附加的 AGD 检测电路,如图 4 所示。基本的检测电路需要满足如下几个要求:①高带宽;②具备一定的抗噪能力;③采样可以准确反映电气参数;④附加电路尽可能不影响开关特性;⑤易于设计逻辑接口。

2.1 时序检测

2.1.1 基于模型时间估计的定位

根据 SiC MOSFET 开关暂态的动态行为模型,各阶段的持续时间都可以被近似估计。在逻辑控制电路中设计固定延时可以实现 AGD 作用时序的控制,本质上属于不准确的开环控制。SiC MOSFET的开关暂态时间会随着负载工况、寄生参数、驱动参数、器件选型的变化而变化,同时受温度影响较大[21]。由于该方法实现简易,不需要高速接口电路,常被用以时序微调以及作为 AGD 的控制变量。

2.1.2 基于栅极回路的定位

根据 SiC MOSFET 的跨导特性,在饱和区其可以近似等效为一个压控电流源,通过检测 vgs 可以得到 id 的状态信息。基于栅极回路的定位[22-23],不参与功率回路高压、大电流的瞬变切换,有利于接口电路的设计,同时在布局上更靠近弱电侧,避免了长反馈线拾取功率级噪声。该方法主要有以下 3 个缺陷:①容易受栅极回路振荡的影响而产生误判,加大滤波电容则降低了检测电路带宽;②不能很好地反映 vds 的信息;③采样电路一定程度上会影响开关速度。

2.1.3 基于功率回路的定位

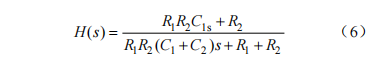

直接对 SiC MOSFET 的 id、vds 状态进行检测,可以最大程度地增加采样的精度与测量带宽。文献[24]通过二阶 RC 分压网络对 vds 进行采样,采样电路的传递函数可表示为

前馈电容 C1 可以加大反馈电压的摆率,提升采样带宽;积分电容 C2 对于反馈信号进行滤波降噪,通过选取 C1 与 C2 的数值可以达到响应速度与噪声的折中。文献[25]则通过一阶 RC 微分电路和 I/V 转换电路得到 dvds/dt 的信息。

对于漏极电流的检测是设计采样电路的难点。文献[22, 26-28]采用了分流电阻的检测方法,该方法实施简易,但分流电阻损耗较大,不适合大电流场合;同时必须选择低感值电阻以减小 did/dt 带来的采样误差。在这种应用中,昂贵的高共模抑制电流感应放大器增加了 AGD 的总体成本。开尔文连接的 SiC MOSFET 可以将 Ls从驱动回路和功率回路中解耦,优化开关轨迹[29]。利用这一特殊结构,文献[24-25]通过检测 Ls 上的感应电压 Lsdid/dt,有效地捕捉了电流变化阶段。这一方法不用外加无源器件,最大程度地利用了器件本身的寄生参数。

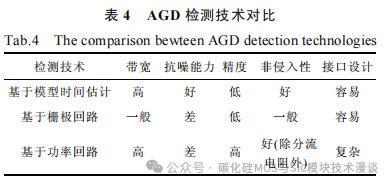

文献[26, 30-32]采用高带宽互感线圈对漏极电流进行实时采样,虽然测量精度较高,但这种方式价格昂贵且不易于集成。基于功率回路的检测定位技术,应对采样电路进行精细的滤波处理,同时无源器件需要有足够的耐压。三种检测技术的对比见表 4。

2.2 接口电路设计

2.2.1 逻辑门翻转

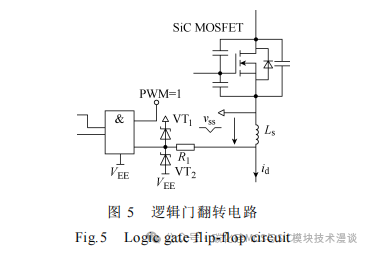

以捕捉电流暂态的接口电路为例,逻辑门翻转电路如图 5 所示,文献[25]采取了逻辑门与功率回路直接连接的接口电路。电流上升阶段,Ls 上的感应电压由 0 降为负值,一旦超过与门的阈值电平,就会促使电路翻转。在该设计中,逻辑门的正电源与 SiC MOSFET 源极相连,负电源则与负驱动电压相连。该接口电路结构简单,但将逻辑门等效为比较器使用,无法改变触发阈值,很容易受到干扰。

2.2.2 比较器触发

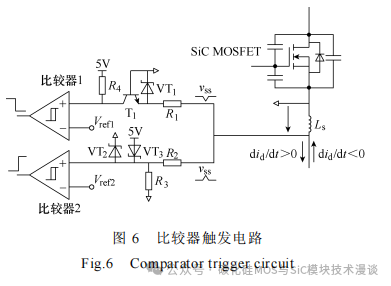

文献[24]通过使用高速比较器,完成了阈值可调的双向逻辑触发。比较器触发电路如图 6 所示,当 id 上升时,在 Ls 上感应出负电压将三极管 VT1射极拉低,比较器 1 正输入端电位低于负输入端,输出翻转为 0;当 id 下降时,在 Ls 上感应出正电压,当比较器 2 正输入端电位高于负输入端时,输出翻转为 1。和采用逻辑门翻转的接口电路相比,比较器触发的方式主要有以下优点:可以灵活设置合理的参考阈值电压,有效规避误触发;构建迟滞型比较器电路可有效缓解电路的干扰振荡;部分比较器带输出锁存功能,为 SiC MOSFET 的状态监控提供了有用信息。

2.2.3 高速 ADC 采样

文献[26, 32]采用高速 ADC 直接读取来自高带宽电流互感器的数值。这种方法可以对 SiC MOSFET的漏极电流进行实时监控,但处理速度不可避免地受限于模数转换电路的性能,同时模拟信号在 SiC MOSFET 驱动过程中容易受到干扰。

AGD 暂态定位部分对于接口电路有如下要求:①完成 1 位或多位的数模转换,电平匹配;②保证强弱电接口的安全可靠;③低延时。以上三种接口电路的设计方法,从成本与结构复杂度的角度依次递增,从响应速度方面依次递减。目前,研究者使用较多的是比较器触发的方式。

3 AGD 的逻辑判断模块

在接收到暂态定位的触发信号后,AGD 需要进行一定的逻辑处理。逻辑处理模块与 PWM 信号相结合,将逻辑分为开通暂态与关断暂态两部分,最终根据功率放大电路的设计,给出特定的减速触发信号。在实现方式方面,主要有采用离散逻辑门电路和采用可编程逻辑器件两种。

3.1 采用离散逻辑门

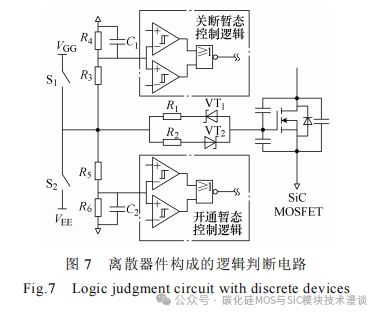

在对于开通与关断暂态独立控制的 AGD 电路中,采用离散逻辑器件在成本方面具有较大优势。离散器件构成的逻辑判断电路如图 7 所示,文献[23]仅使用两个比较器和一个或非门就完成了逻辑处理工作,并且开通与关断的逻辑电路完全一致。采用离散器件的逻辑处理方式对后期集成电路设计具有指导意义,但对于功率放大结构复杂的 AGD 电路,会导致器件堆积的问题,增加了设计难度以及系统功耗。每一个逻辑门芯片都至少具有数 ns 的延时,多级串联使用的情况下对于 AGD 处理速度的影响较大。

3.2 采用可编程逻辑器件

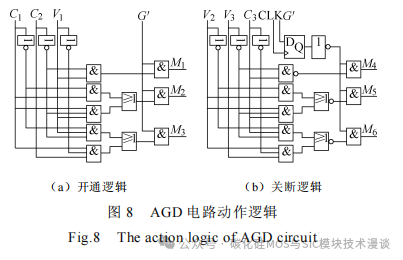

采用可编程逻辑器件 FPGA 或 CPLD 是目前复杂逻辑处理的首选。文献[27]的开通与译码逻辑如图 8 所示,显然采用 HDL 语言可以大大简化设计的复杂度。由于可编程逻辑器件具有相对固定的延时,有利于多路逻辑的综合,拓展了 AGD 功率放大电路设计的自由度。但对于简单逻辑控制的 AGD 电路,采用可编程器件会造成资源的浪费,同时在成本方面也不具备优势。

4 AGD 的功率放大模块

功率放大驱动部分是 AGD 电路的核心。通过该模块内部晶体管的动作,可以改变 SiC MOSFET开关暂态阶段驱动电阻 Rg、驱动电压 Vdr、驱动电流 ig 的数值,以达到抑制超调、振荡、EMI 的目的。根据改变的栅极物理量的不同,功率放大部分主要有变驱动电阻型、变驱动电压型、抽取/注入驱动电流型以及电流型等。调节 Ciss 也可对 SiC MOSFET开关暂态的 did/dt、dv/dt 进行调节,但由于以下原因很少应用:①电容容差大,温漂严重;②对附加Cgd 耐压要求较高;③SiC MOSFET 输入电容非线性,模型不精确;④修改电容参数有增大串扰风险;⑤不易于集成。

4.1 变驱动电阻型

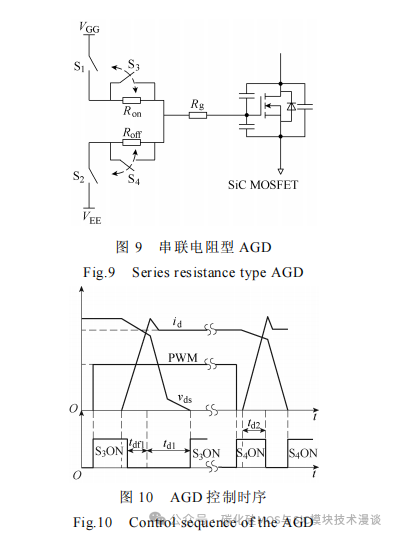

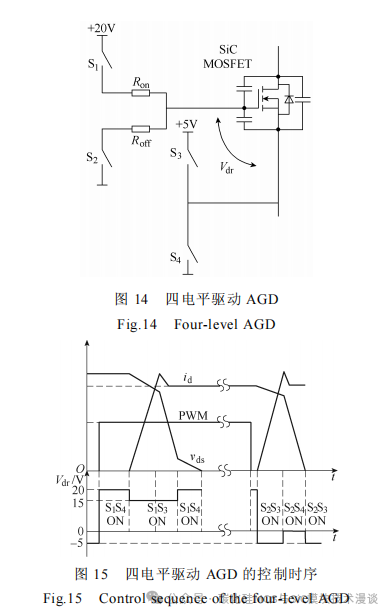

文献[33]将驱动电阻分为两部分,通过旁路其中一个电阻,而达到调节总驱动电阻的目的。文献[33]提出的串联电阻型 AGD 如图 9 所示,调节电阻Ron 和 Roff 与原驱动电阻 Rg 为串联关系。S1 和 S2 的断开,使得开关速度下降,继而电压、电流超调与did/dt,dv/dt 下降,缓解了 EMI。通过调节 S3、S4断开的时间,从而达到开关速度与开关损耗的折中。图 10 为该电路的 AGD 控制时序[33]。

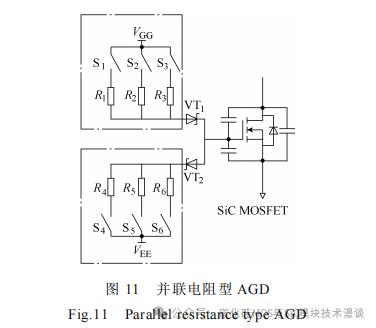

文献[27]将 SiC MOSFET 开通与关断暂态分为精确的八个阶段,通过多级并联电阻的方式,改变

总的驱动电阻值,如图 11 所示。该设计在开通和关断某一暂态时,最多可以实现六种驱动电阻数值的选择,并且可以通过增加并联支路数达到更多组合方式。

通过调整驱动电阻串并联形式的 AGD 电路结构可重复性高、便于集成。但每个电阻几乎都需要一个与之对应的晶体管及驱动电路,增加了器件的数量与控制复杂度,切换速度以及稳定性也值得关注。同时,想达到更高分辨率的驱动电阻调节,必须增加串并联支路的数量,使得系统更加复杂。

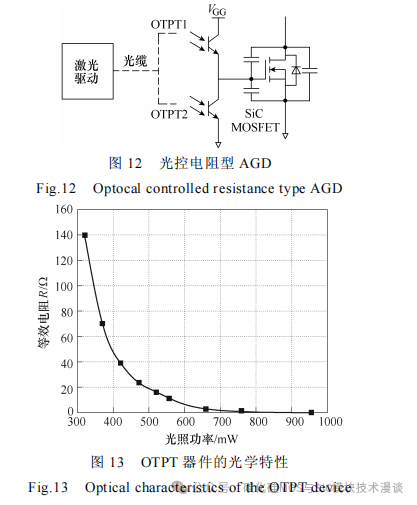

为达到 Rg 的无级调节,砷化镓光触发功率晶体管(GaAs-based Optically Triggered Power Transistor, GaAs-OTPT)被应用于 AGD 电路中[34],光控电阻型 AGD 如图 12 所示。OTPT 的等效电阻随照射其表面的光照功率的上升而减低,通过可调激光源,能够实现驱动电阻的无级调节,OTPT 器件的光学特性如图 13 所示[34]。虽然该结构同样能有效调节SiC MOSFET 的开关暂态,但 OTPT 等效电阻的非线性、系统调节速度以及附加电路成本使得该方法的推广仍存在着一些挑战。

4.2 变驱动电压型

降低驱动电压可以减缓对于 Ciss 的充电速度。文献[24]将传统的两电平驱动,拓展为四电平驱动,如图 14 所示,通过增设一对推挽管,在开关瞬态向漏极投切一个辅助电平,在不破坏原有驱动结构的情况下,有效降低了驱动电压的绝对值。图 15 给出了等效栅极驱动电压 Vdr 的变化情况[24]。该结构通过调节投切时间来达到开关速度与开关损耗的折中,但无法调节单个驱动电平。

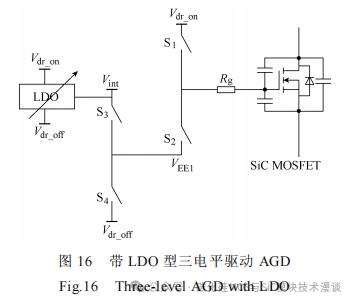

为提升驱动电压的调节自由度,可调线性稳压器(Low Dropout Regulator, LDO)被应用于文献[30]中。带 LDO 型三电平驱动 AGD 如图 16 所示[30],该设计为三电平驱动,两推挽电路呈垂直级联结构,增加级联阶数可以输出更多的驱动电平。输出电压可调的 LDO 使得 Vint 不再固定,用户可以根据使用场合灵活设定,但无法在线实时调节。

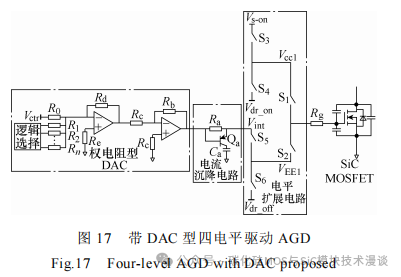

文献[31]将驱动电平数提升为 4 个,带 DAC 型四电平驱动 AGD 如图 17 所示。为进一步提高驱动电压在线调节的自由度,该设计搭建了权电阻型DAC。在使用 n 个增益电阻的情况下,可以输出 2n级驱动电压;在 n 足够大时,近似可达成驱动电压的无级调节。附加的电流沉降电路提升了驱动电压的下拉能力,可以有效降低误触发风险。此设计中,高速 DAC 与高带宽功放等设计增加了成本与设计的复杂度。

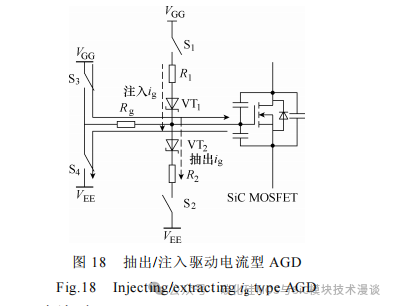

4.3 抽出/注入驱动电流型

在 SiC MOSFET 高速开启瞬态,抽取一部分栅极驱动电流 ig,有利于降低开通速度,减小电流超调;在关断瞬态,注入一部分 ig,有利于减小关断速度,降低电压应力以及 EMI 水平。文献[25]在开关暂态阶段分别导通 S1 和 S2,以实现动态栅极电流调节的功能,抽出/注入驱动电流型 AGD 如图 18所示。经分析,在忽略防电流倒灌二极管压降以及将辅助开关管视为理想开关的情况下,抽出/注入驱动电流型的 AGD 电路等效为变驱动电阻型和变电压型的复合电路,本质上仍为电压型驱动电路。

4.4 电流型

传统电压型驱动电路在开关瞬态可以等效为RC 充电电路,SiC MOSFET 是一个复杂的高阶数学模型。采用恒栅极电流的 AGD 电路有利于对 SiC MOSFET 驱动进行降阶处理,直接调节 ig 更有利于对 did/dt、dv/dt 进行精确调节,进而更有针对性地优化开关轨迹,分别表示为

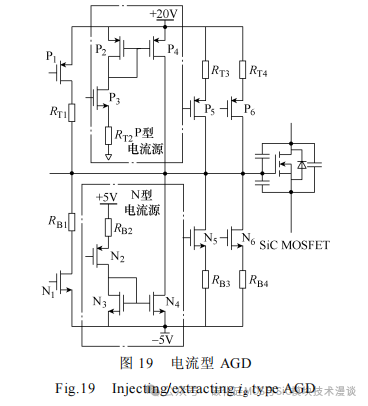

文献[32]提出了应用于 SiC MOSFET 的电流源驱动电路,电流型 AGD 如图 19 所示。上部分 P 型电流源主导开通过程的栅极电流控制,P1、RT1 主要用以缩短开通延时;P2、P4、P3、RT2 构成的可控电

流镜可从栅极注入恒定电流,用于开通 did/dt 的斜率控制;RT3、P5 用于抑制开通电流超调;RT4、P6用于加快开通时的电压下降速度以进一步减小开通损耗。下部分 N 型电流源电路主要用于从栅极抽取恒定的驱动电流,功能与 P 型电路类似,不再赘述。

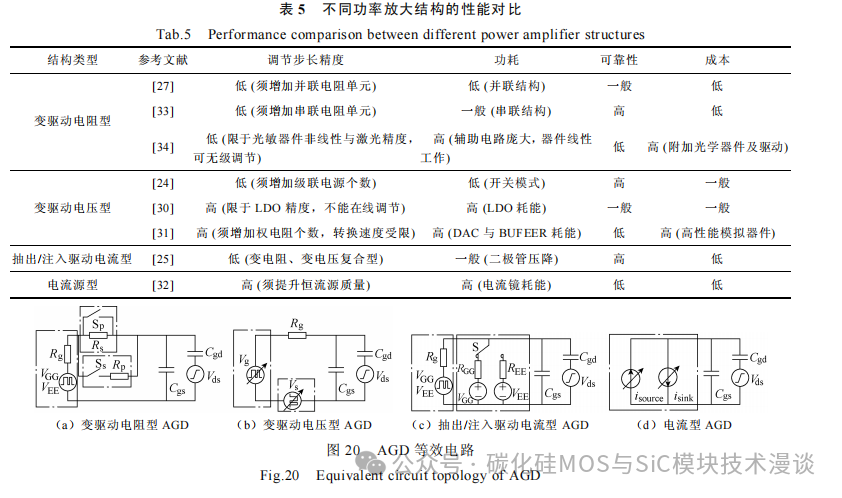

表 5 给出了本节所提四大类 AGD 功率放大驱动的性能对比,并作出了相关解释。调节步长精度表示 AGD 对于 Rg、Vdr、ig 控制的准确度,可以看出,调 Vdr 与恒 ig 型可以获得较高的调节精度,这得益于内部模拟器件工作于线性区域,但不可避免地会增加 AGD 电路的能耗。变电阻型、抽取/注入电流型、以及文献[24]中的变 Vdr 结构虽然调节精度受限,但由于其工作于开关模式,在能耗方面有着独特的优势。AGD 电路属于新型驱动电路,由于器件数量的增加,在可靠性方面逊于 CGD 电路。表 5中可靠性的评价标准为附加电路受损情况下,SiC MOSFET 能否继续运行。对于激光驱动、恒流驱动的 AGD,由于改变了 CGD 驱动的电路架构,所以可靠性下降。变 Rg 结构,根据切换开关管的串并联关系,可以得知文献[33]的设计在可靠性方面优于文献[27]。变电压型 AGD 的主要敏感部件为 DAC与 BUFFER 电路,同时也是其成本明显高于其他AGD 电路的原因。 图 20 给出了四种功率放大模式的等效电路结

构性能对比。可以看出,变驱动电阻型和抽出/注入驱动电流型 AGD 电路均保留了原 CGD 电路的驱动架构。变电压型 AGD 在固定某些附加电平的情况下等效于 CGD 电路。电流型 AGD 表现为以可变电流源替代电压源。

5 AGD 的控制效果

图 21 展示了文献[24]所提出的变驱动电压型AGD 对于 SiC MOSFET 开关轨迹的优化效果,实验在 500V/280A 双脉冲测试平台上进行。在开通轨迹的优化对比中,相同电流超调量的情况下 AGD电路所带来的开通延时以及开通损耗远低于 CGD电路;在关断轨迹的优化对比中,相同电压超调量下 AGD 的关断延时以及关断损耗同样远低于 CGD电路。图 21 展示的 SiC MOSFET 开关轨迹优化趋势与图 2 的分析一致。

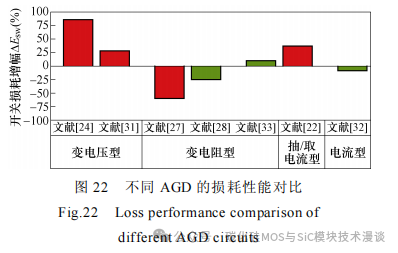

相同电流、电压抑制效果下 SiC MOSFET 开关损耗的增幅是衡量 AGD 电路性能的重要指标。AGD电路不仅不会显著增大开关损耗,同时可以通过抑制电气超调来降低开关损耗,提升系统效率。由于各文献中双脉冲测试电路寄生参数和工作点存在差异,为直观对比不同类型 AGD 电路中 SiC MOSFET开关轨迹的优化效果,采用百分比的形式对总开关损耗增幅ΔEsw 进行统计。图 22 给出了开通电流超调量和关断电压超调量抑制均在 40%~60%范围内,不同 AGD 总开关损耗的增幅。显然,即使相较于 CGD 电路优势明显,但不同 AGD 技术在损耗优化方面的表现不尽相同。文献[27]所采用的变电阻型 AGD 展示出最优良的损耗特性,在 40%电流超调抑制、47%电压超调抑制的情况下可以使得 SiC MOSFET 的总开关损耗降低近 60%,而文献[24]所提出的 AGD 电路则会使得开关损耗上升 86%,这为高效率系统设计带来了挑战。SiC MOSFET 开关暂态定位的准确度直接决定了 AGD 的损耗特性,一旦对于开关管开关暂态的捕捉产生偏移,开关损耗就会大大上升。采用低成本的比较器触发进行暂态定位的精度相较于采用实时 ADC 采样低一些。

6 AGD 的设计流程

SiC MOSFET 的开关轨迹优化主要分为三个步骤:①确定时间节点;②选取轨迹路径;③执行轨迹优化。开关轨迹优化的时间节点大多在电力电子变换器主电路设计完成之后,此时电路拓扑、回路寄生参数、功率器件选型、负载电流范围等因素基本落实,SiC MOSFET 初始条件下的开关轨迹也随之确定,AGD 可以更有针对性开展调控。

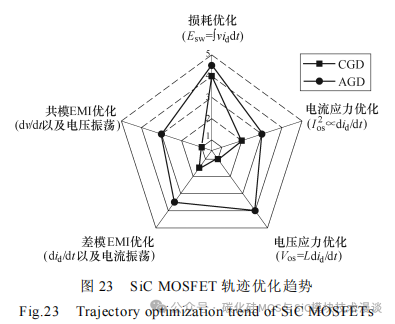

SiC MOSFET 开关轨迹优化路径的选取是以初始轨迹以及变换器应用环境要求为导向的。首先,设计者需要借助 CGD 电路对 SiC MOSFET 进行双脉冲测试,以获得其初始开关轨迹下开关损耗、电气超调、电磁干扰发射强度等基本数据。其次,结合初始轨迹和应用场景确定开关轨迹优化的方向,电气应力、EMI 强度、开关损耗的同步降低是最理想的开关轨迹,但由于降低开关速度势必会影响开关损耗,有时需要设计者确定轨迹优化的重心,例如,应用于精密仪器的电源必须以削弱 EMI 为导向,器件安全区裕度不足时必须以降低电气超调量为导向,而追求高效率的电力电子装置则必须以最小化开关损耗为导向。最后,设计者需要从初始轨迹出发,初步确定 AGD 电路的参数,提升 AGD 参数整定的效率。图 23 给出了 SiC MOSFET 最理想的开关轨迹优化趋势。

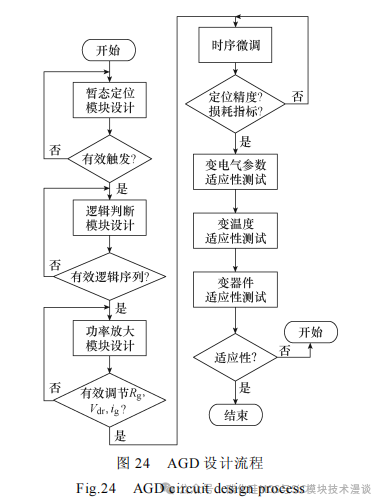

暂态定位、逻辑判断、功率放大三部分共同完成了 AGD 的开关轨迹优化功能。目前,不同文献在三个模块电路的设计上均作出了不同类型的尝试。在对各设计方案进行横向对比后,给出了基于开关轨迹优化的 SiC MOSFET 有源驱动电路的基本设计流程,如图 24 所示。

暂态定位模块的触发、逻辑判断模块的信号处理序列以及功率放大模块的可靠调节是 AGD 电路有效工作的必要前提。其中,环路响应的速度与对SiC MOSFET 开关噪声的抑制能力是设计者选择不同模块设计方案时需要重点关注的问题。

在功率放大模块完成对于 SiC MOSFET 的超调、振荡、EMI 等负面效应的抑制效果后,需要对AGD 操作的时序进行微调:一方面,闭环调节使得SiC MOSFET 的开关速度产生变化,暂态定位点会产生一定的漂移,需要进行相应的补偿;另一方面,随着开关速度的降低,SiC MOSFET 的开关损耗会上升,调节作用时间能够实现开关损耗与开关速度的折中[24, 33]。常用的时序微调方法有调节暂态定位触发阈值[22-24]以及在逻辑处理模块中加入延时两种[24, 26, 30-31]。

能否适应 SiC MOSFET 的实际运行是衡量AGD 电路质量的重要标准,不同类型的参数适应性测试是必不可少的。变电气参数适应性测试主要有三类:①变母线电压测试[24-25],以验证 SiC MOSFET在不同电压应力条件下 AGD 电路的有效性;②变负载电流测试[22, 24-25, 31-32],以验证不同工作负载下AGD 电路的有效性;③变无源参数测试[22-23, 25-28],即在不同驱动电阻、寄生参数等条件下验证 AGD电路的有效性。变温度参数适应性测试[31]主要有两个目的:一方面,验证 AGD 中附加模拟电路在长时间工作条件下是否会产生显著温漂影响正常工作;另一方面,验证 AGD 能否继续适应 SiC MOSFET发热所带来的轨迹漂移。变器件适应性测试[30, 33]则是验证 AGD 电路对于 SiC 器件的普适性,不同型号的 SiC MOSFET 的开关特性有所不同,优秀的AGD 电路可以在不大幅修改设计参数情况下适应不同器件。

以上步骤基本保证 AGD 的可靠性,成本的校核应渗透在子模块的方案选择中,同样需要考虑。

7 AGD 的发展趋势

宽禁带半导体的有源栅极驱动的相关研究目前仍处于起步阶段。与应用于 IGBT 的 AGD 电路[35-36]相类似,基于开关轨迹优化的 SiC MOSFET 有源驱动电路未来发展趋势与技术难题主要有以下几点:

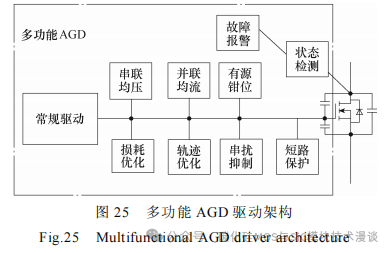

1)功能复化: 随着 SiC 器件的逐步推广,对于驱动电路的要求也逐步增多。单纯某一种类型的有源驱动并不能很好地对 SiC MOSFET 开关瞬态进行多角度的改善。将短路保护、串扰抑制等其他功能纳入基于开关轨迹优化的 AGD 电路成为必然要求,多功能AGD 驱动架构如图 25 所示。如何对于大量的附加电路进行分时复用,进而简化设计、降低成本是技术难点。

2)控制升级

控制稳定性方面,SiC MOSFET 跨导与结电容有着很强的非线性特征[37],并且电压源驱动下的SiC MOSFET 的响应特性是复杂的高阶数学方程。同时,阈值切换型 AGD 电路本质上属于一种非线性的闭环控制,无法使用全闭环型 AGD 中伯德图、根轨迹等分析工具来研究控制系统的稳定性。目前,对于 SiC MOSFET 开关暂态的建模工作仍在进行之中。

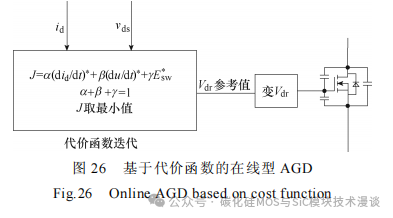

控制精度方面,SiC MOSFET 的开关轨迹随着工作电压、负载电流的变化而变化[38],这对于 AGD电路开关轨迹优化的效果产生一定的影响:一方面,AGD 的暂态定位点有可能产生一定的偏移,功率放大电路的动作可能产生超前或滞后;另一方面,SiC MOSFET 漏源电压的超调振荡随着负载电流的增大而恶化,在调节参数相对固定的情况下,AGD 电路可能在重载时发生失效,在轻载时则会造成多余的开关损耗。目前,基于开关轨迹优化的 AGD 电路的自适应调节技术还鲜有报道。文献[31]提出了基于代价函数的在线参数选择的 AGD 逻辑处理架构,如图 26 所示。该方法可以大幅提升 AGD 的控制精度,通过设置权重因子α、β、γ 实现对于 did/dt、dv/dt、Esw 等多个指标的折中控制,但是控制器运算速度、迭代算法收敛性以及硬件成本成为需要进一步解决的问题。

响应带宽方面,随着高性能模拟、数字器件技术的进步,更高的响应速度得以应用于 SiC MOSFET的 ns 级控制。高频数字信号交互所带来的信号完整问题[39]、运算放大器增益带宽积与压摆率的限制[40]以及附加器件布局方式有待深入研究。

3)硬件集成与成本约束

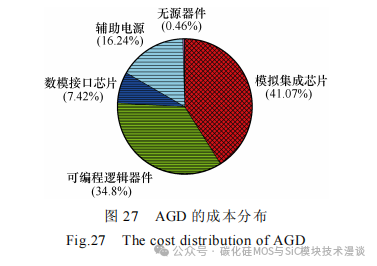

AGD 电路最终的市场化必须缩小体积、降低成本,并以单片的形式推荐给用户。图 27 给出了文献[31]中 AGD 电路的成本分布。图中,模拟集成电路与可编程逻辑器件是制约 AGD 市场化的主要因素。在电路集成方面,数字电路的集成化易于实现,而如比较器、DAC、Buffer 等模拟电路的集成则复杂得多,对于 SiC MOSFET 开关暂态的电磁干扰也更为敏感。另外,辅助电源的个数也需要加以控制。进一步简化附加有源电路是未来 AGD 的发展趋势。

8 结论

SiC MOSFET 高速开关轨迹中的超调、振荡、EMI 问题成为制约其进一步推广的因素。本文综述了目前基于 SiC MOSFET 开关轨迹优化的 SiC MOSFET 有源驱动电路相关技术。

1)阐述了 SiC MOSFET 轨迹优化的含义,分析了 AGD 电路的工作原理,总结了不同栅极驱动参数对于 SiC MOSFET 开关特性的影响,着重剖析阈值触发型 AGD 电路的工作模式。

2)分别从暂态定位、逻辑判断、功率放大三个子电路的设计方案角度出发,对现有文献进行综述,并对比了不同技术之间的性能差异,得出四种主流AGD 架构的等效电路模型。

3)给出了 AGD 电路基本的设计流程建议。

4)讨论了 AGD 电路技术未来的发展方向。随着宽禁带器件驱动技术的不断发展,基于SiC MOSFET 开关轨迹优化的有源栅极驱动技术具有巨大的研究价值与广阔的应用空间。

参考文献

[1] 梁 美 , 郑琼林 , 可 翀 , 等 . SiC MOSFET 、 Si

CoolMOS 和 IGBT 的特性对比及其在 DAB 变换器

中的应用[J]. 电工技术学报, 2015, 30(12): 41-50.

Liang Mei, Zheng Qionglin, Ke Chong, et al.

Performance comparison of SiC MOSFET, Si

CoolMOS and IGBT for DAB converter[J]. Transa

ctions of China Electrotechnical Society, 2015,

30(12): 41-50.

[2] Schrock J, Pushpakaran B, Bilbao A, et al. Failure

analysis of 1200V/150A SiC MOSFET under

repetitive pulsed overcurrent conditions[J]. IEEE

Transactions on Power Electronics, 2016, 31(3):

1816-1821.

[3] Li Hong, Jiang Yanfeng, Qiu Zhidong, et al. A

predictive algorithm for crosstalk peaks of SiC

MOSFET by considering the nonlinearity of gate

drain capacitance[J]. IEEE Transactions on Industrial

Electronics, 2021, 36(3): 2823-2834.

[4] Roy S, Basu K. Analytical estimation of turn on

switching loss of SiC mosfet and schottky diode pair

from datasheet parameters[J]. IEEE Transactions on

Power Electronics, 2019, 34(9): 9118-9130.

[5] Roy S, Basu K. Analytical model to study hard turn

off switching dynamics of SiC MOSFET and schottky

diode pair[J]. IEEE Transactions on Power Elec

tronics, 2021, 36(1): 861-875.

[6] Zhang Zheyu, Wang Fred, Tolbert L, et al. Evaluation

of switching performance of SiC devices in PWM

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?