RCC_Init主要用于对STM32芯片的时钟进行初始化,以下以STM32F1系列为例。

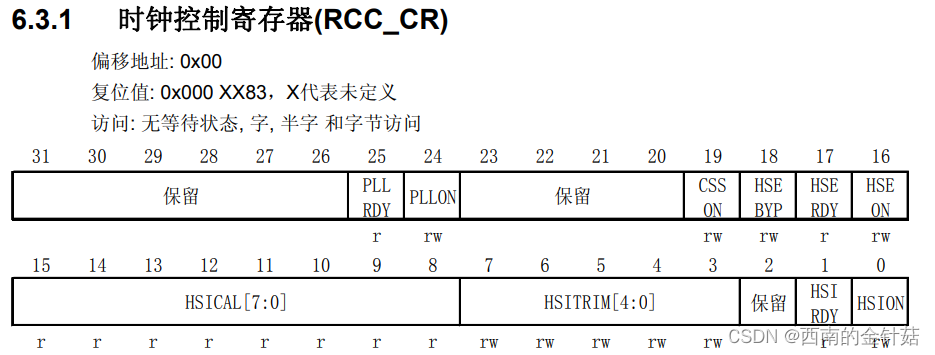

在STM32F10xxx参考手册中,我们可以找到:

| 位31:26 | 保留,始终读为0。 |

| 位25 | PLLRDY:PLL时钟就绪标志 (PLL clock ready flag) PLL锁定后由硬件置’1’。 0:PLL未锁定; 1:PLL锁定。 |

| 位24 | PLLON:PLL使能 (PLL enable) 由软件置’1’或清零。 当进入待机和停止模式时,该位由硬件清零。当PLL时钟被用作或被选择将要作为系统时钟 时,该位不能被清零。 0:PLL关闭; 1:PLL使能。 |

| 位23:20 | 保留,始终读为0。 |

| 位19 | CSSON:时钟安全系统使能 (Clock security system enable) 由软件置’1’或清零以使能时钟监测器。 0:时钟监测器关闭; 1:如果外部4-16MHz振荡器就绪,时钟监测器开启。 |

| 位18 | HSEBYP:外部高速时钟旁路 (External high-speed clock bypass) 在调试模式下由软件置’1’或清零来旁路外部晶体振荡器。 只有在外部4-16MHz振荡器关闭的情 况下,才能写入该位。 0:外部4-16MHz振荡器没有旁路; 1:外部4-16MHz外部晶体振荡器被旁路。 |

| 位17 | HSERDY:外部高速时钟就绪标志 (External high-speed clock ready flag) 由硬件置’1’来指示外部4-16MHz振荡器已经稳定。 在HSEON位清零后,该位需要6个外部4- 25MHz振荡器周期清零。 0:外部4-16MHz振荡器没有就绪; 1:外部4-16MHz振荡器就绪。 |

| 位16 | HSEON:外部高速时钟使能 (External high-speed clock enable) 由软件置’1’或清零。 当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器。当外部4-16MHz振荡 器被用作或被选择将要作为系统时钟时,该位不能被清零。 0:HSE振荡器关闭; 1:HSE振荡器开启。 |

| 位15:8 | HSICAL[7:0]:内部高速时钟校准 (Internal high-speed clock calibration) 在系统启动时,这些位被自动初始化 |

| 位7:3 | HSITRIM[4:0]:内部高速时钟调整 (Internal high-speed clock trimming) 由软件写入来调整内部高速时钟,它们被叠加在HSICAL[5:0]数值上。 这些位在HSICAL[7:0]的基础上,让用户可以输入一个调整数值,根据电压和温度的变化调整 内部HSI RC振荡器的频率。 默认数值为16,可以把HSI调整到8MHz±1%;每步HSICAL的变化调整约40kHz。 |

| 位2 | 保留,始终读为0。 |

| 位1 | HSIRDY:内部高速时钟就绪标志 (Internal high-speed clock ready flag) 由硬件置’1’来指示内部8MHz振荡器已经稳定。在HSION位清零后,该位需要6个内部8MHz振 荡器周期清零。 0:内部8MHz振荡器没有就绪; 1:内部8MHz振荡器就绪。 |

| 位0 | HSION:内部高速时钟使能 (Internal high-speed clock enable) 由软件置’1’或清零。 当从待机和停止模式返回或用作系统时钟的外部4-16MHz振荡器发生故障时,该位由硬件置’1’ 来启动内部8MHz的RC振荡器。当内部8MHz振荡器被直接或间接地用作或被选择将要作为系 统时钟时,该位不能被清零。 0:内部8MHz振荡器关闭; 1:内部8MHz振荡器开启。 |

| 位31:27 | 保留,始终读为0。 |

| 位26:24 | MCO: 微控制器时钟输出 (Microcontroller clock output) 由软件置’1’或清零。 0xx:没有时钟输出; 100:系统时钟(SYSCLK)输出; 101:内部RC振荡器时钟(HSI)输出; 110:外部振荡器时钟(HSE)输出; 111:PLL时钟2分频后输出。 注意:- 该时钟输出在启动和切换MCO时钟源时可能会被截断。 - 在系统时钟作为输出至MCO引脚时,请保证输出时钟频率不超过50MHz (I/O口最高频率)。 |

| 位22 | USBPRE:USB预分频 (USB prescaler) 由软件置’1’或清’0’来产生48MHz的USB时钟。在RCC_APB1ENR寄存器中使能USB时钟之 前,必须保证该位已经有效。如果USB时钟被使能,该位不能被清零。 0:PLL时钟1.5倍分频作为USB时钟 1:PLL时钟直接作为USB时钟 |

| 位21:18 | PLLMUL:PLL倍频系数 (PLL multiplication factor) 由软件设置来确定PLL倍频系数。只有在PLL关闭的情况下才可被写入。 注意:PLL的输出频率不能超过72MHz 0000:PLL 2倍频输出 1000:PLL 10倍频输出 0001:PLL 3倍频输出 1001:PLL 11倍频输出 0010:PLL 4倍频输出 1010:PLL 12倍频输出 0011:PLL 5倍频输出 1011:PLL 13倍频输出 0100:PLL 6倍频输出 1100:PLL 14倍频输出 0101:PLL 7倍频输出 1101:PLL 15倍频输出 0110:PLL 8倍频输出 1110:PLL 16倍频输出 0111:PLL 9倍频输出 1111:PLL 16倍频输出 |

| 位17 | PLLXTPRE:HSE分频器作为PLL输入 (HSE divider for PLL entry) 由软件置’1’或清’0’来分频HSE后作为PLL输入时钟。只能在关闭PLL时才能写入此位。 0:HSE不分频 1:HSE 2分频 |

| 位16 | PLLSRC:PLL输入时钟源 (PLL entry clock source) 由软件置’1’或清’0’来选择PLL输入时钟源。只能在关闭PLL时才能写入此位。 0:HSI振荡器时钟经2分频后作为PLL输入时钟 1:HSE时钟作为PLL输入时钟。 |

| 位15:14 | ADCPRE[1:0]:ADC预分频 (ADC prescaler) 由软件置’1’或清’0’来确定ADC时钟频率 00:PCLK2 2分频后作为ADC时钟 01:PCLK2 4分频后作为ADC时钟 10:PCLK2 6分频后作为ADC时钟 11:PCLK2 8分频后作为ADC时钟 |

| 位13:11 | PPRE2[2:0]:高速APB预分频(APB2) (APB high-speed prescaler (APB2)) 由软件置’1’或清’0’来控制高速APB2时钟(PCLK2)的预分频系数。 0xx:HCLK不分频 100:HCLK 2分频 101:HCLK 4分频 110:HCLK 8分频 111:HCLK 16分频 |

| 位10:8 | PPRE1[2:0]:低速APB预分频(APB1) (APB low-speed prescaler (APB1)) 由软件置’1’或清’0’来控制低速APB1时钟(PCLK1)的预分频系数。 警告:软件必须保证APB1时钟频率不超过36MHz。 0xx:HCLK不分频 100:HCLK 2分频 101:HCLK 4分频 110:HCLK 8分频 111:HCLK 16分频 |

| 位7:4 | HPRE[3:0]: AHB预分频 (AHB Prescaler) 由软件置’1’或清’0’来控制AHB时钟的预分频系数。 0xxx:SYSCLK不分频 1000:SYSCLK 2分频 1100:SYSCLK 64分频 1001:SYSCLK 4分频 1101:SYSCLK 128分频 1010:SYSCLK 8分频 1110:SYSCLK 256分频 1011:SYSCLK 16分频 1111:SYSCLK 512分频 注意:当AHB时钟的预分频系数大于1时,必须开启预取缓冲器。详见闪存读取(第2.3.3节)。 |

| 位3:2 | SWS[1:0]:系统时钟切换状态 (System clock switch status) 由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟。 00:HSI作为系统时钟; 01:HSE作为系统时钟; 10:PLL输出作为系统时钟; 11:不可用。 |

| 位1:0 | SW[1:0]:系统时钟切换 (System clock switch) 由软件置’1’或清’0’来选择系统时钟源。 在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择 HSI作为系统时钟(如果时钟安全系统已经启动) 00:HSI作为系统时钟; 01:HSE作为系统时钟; 10:PLL输出作为系统时钟; 11:不可用 |

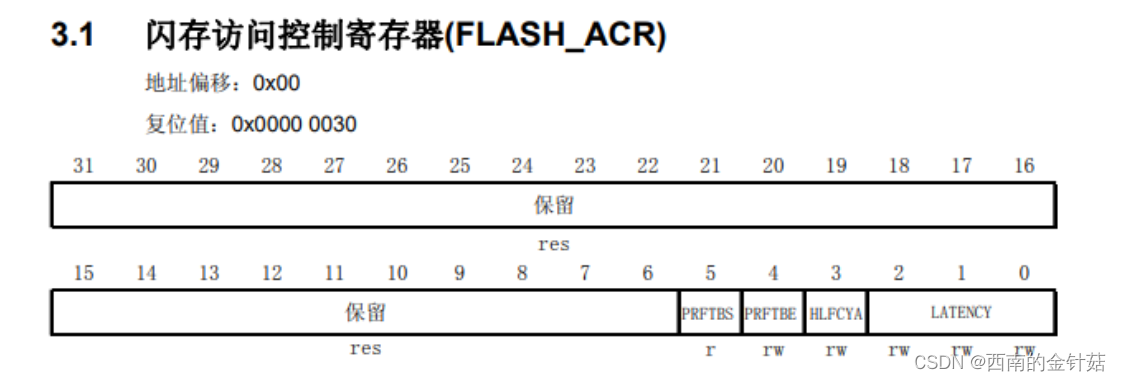

同时,在ST公司Flashprogramming manual中,我们可以找到:

| 位31~6 | 保留。必须保持为清除状态‘0’ |

| 位5 | PRFTBS:预取缓冲区 该位指示预取缓冲区的状态 0:预取缓冲区关闭; 1:预取缓冲区开启。 |

| 位4 | PRFTBE:预取缓冲区使能 0:关闭预取缓冲区; 1:开启预取缓冲区。 |

| 位3 | HLFCYA:闪存半周期访问使能 0:禁止半周期访问; 1:启用半周期访问。 |

| 位2~0 | LATENCY:时延 这些位表示SYSCLK(系统时钟)周期与闪存访问时间的比例 000:零等待状态,当0<SYSCLK≤24MHz 001:一个等待状态,当24MHz<SYSCLK≤48MHz 010:两个等待状态,当48MHz<SYSCLK≤72MHz |

对照上述几个寄存器,我们可以配出代码:

按上述配置,我们可以得到一个由外部高速时钟HSE输入的8MHz频率,经锁相环9倍频后得到72MHz频率,并以此为系统时钟的时钟配置。若要更改配置,可以参照上述数据手册进行自行更改。

本文详细解释了STM32芯片RCC_Init中的时钟配置,包括HSE、HSI、PLL的使用,以及预分频、锁相环等技术在确定系统时钟频率中的作用。

本文详细解释了STM32芯片RCC_Init中的时钟配置,包括HSE、HSI、PLL的使用,以及预分频、锁相环等技术在确定系统时钟频率中的作用。

317

317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?