8.1 实验目的

(1)通过总线将微程序控制器与运算器、存储器等联机,组成一台模型计算机

(2)用微程序控制器控制模型机数据通路,运行由四条机器指令组成的简单程序

(3)掌握微指今与机器指令的关系,建立整机概念

8.2 实验要求

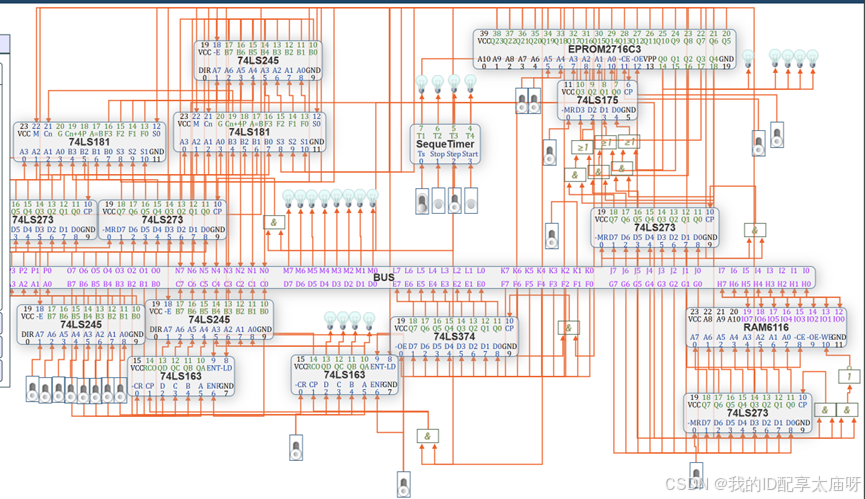

(1)做好实验预习,复习微指令和机器指令的概念,读懂实验电路图,熟悉实验元器件的功能特性和使用方法。

(2)对于实验任务中的问题,在实验前预先给出答案,以便与实验结果相比较。

(3)在实验过程中单步运行微程序,注意理解微程序与程序的联系和区别。

(4)写出实验报告。

8.3 实验电路

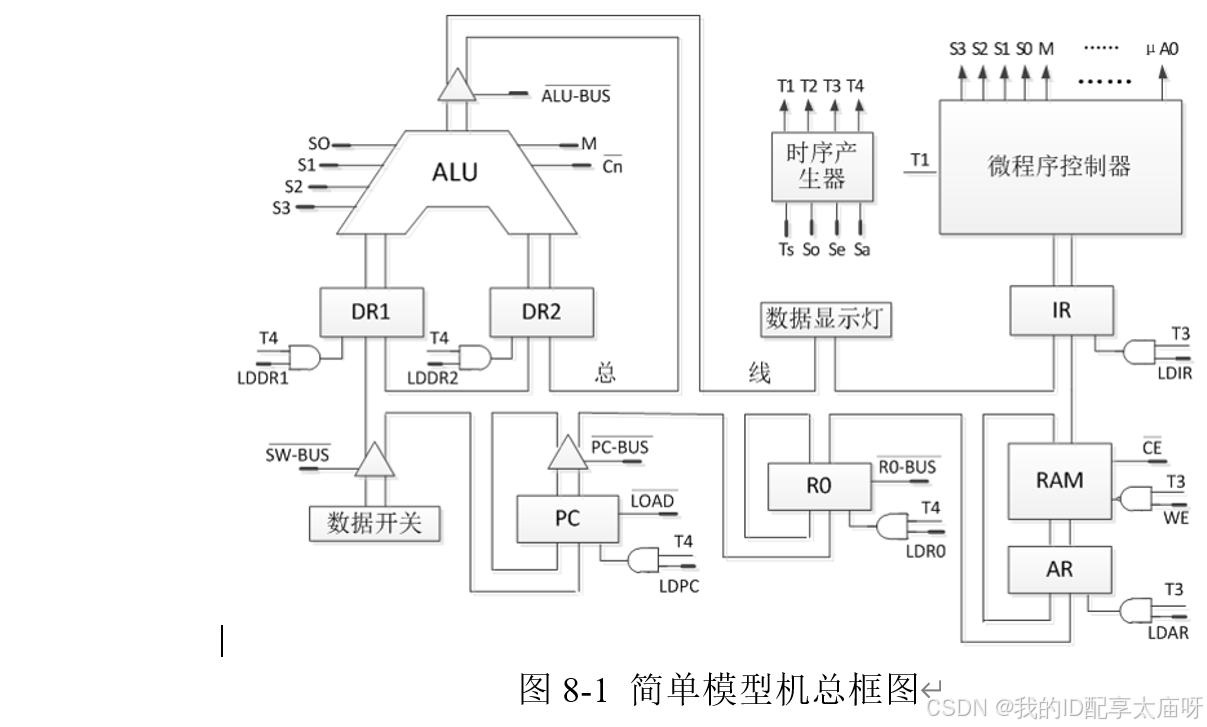

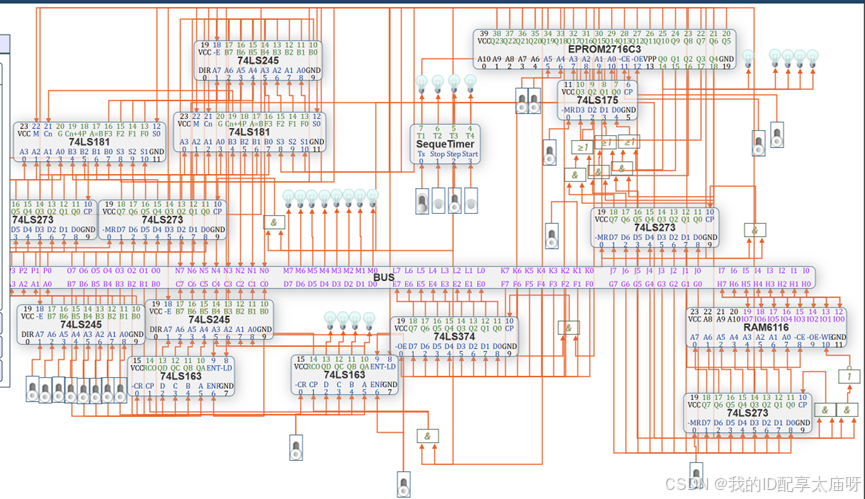

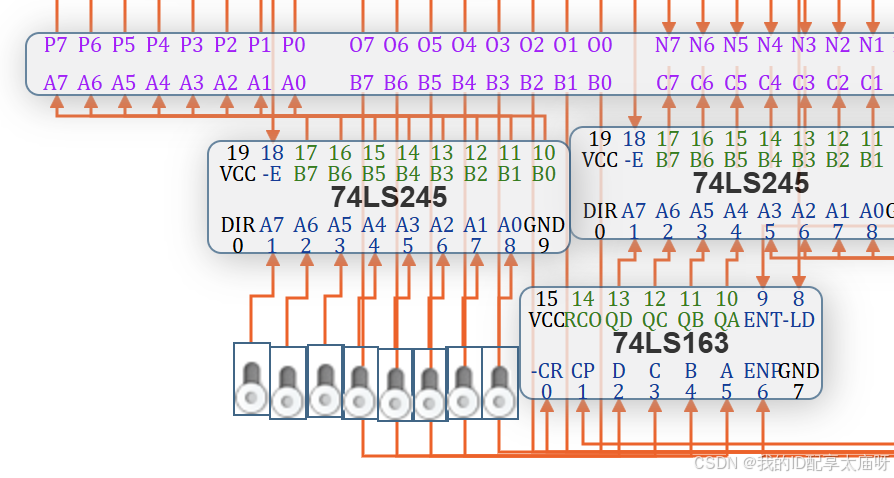

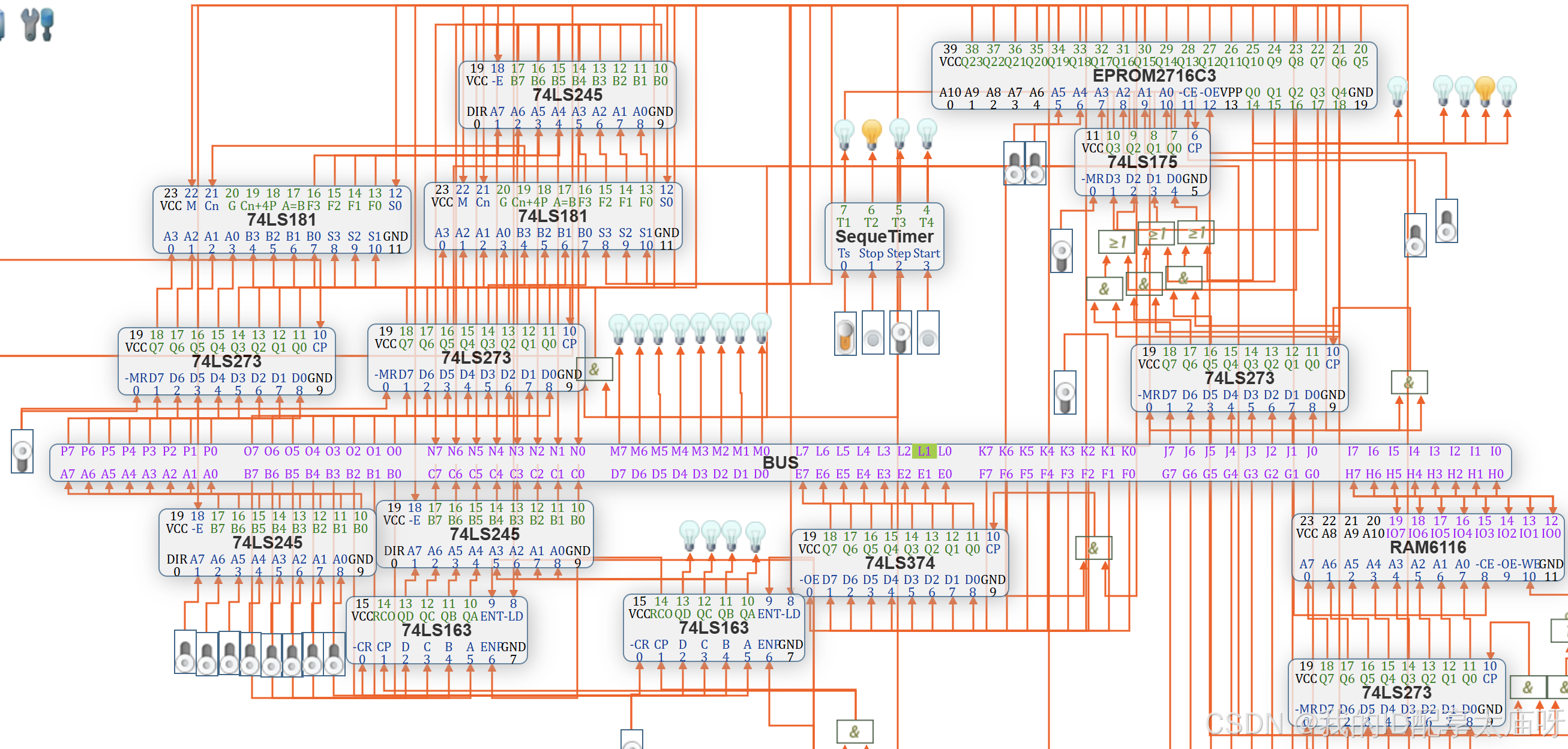

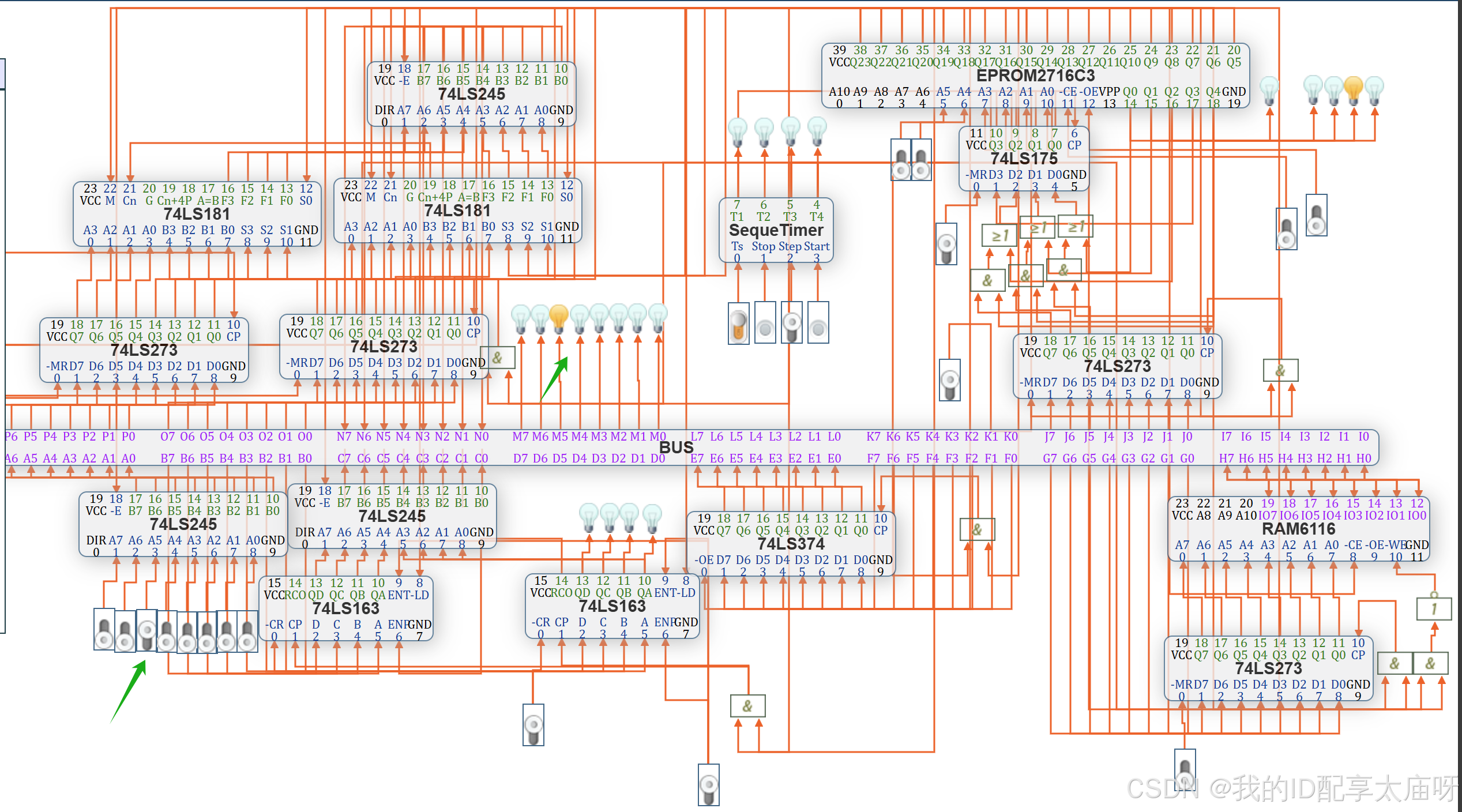

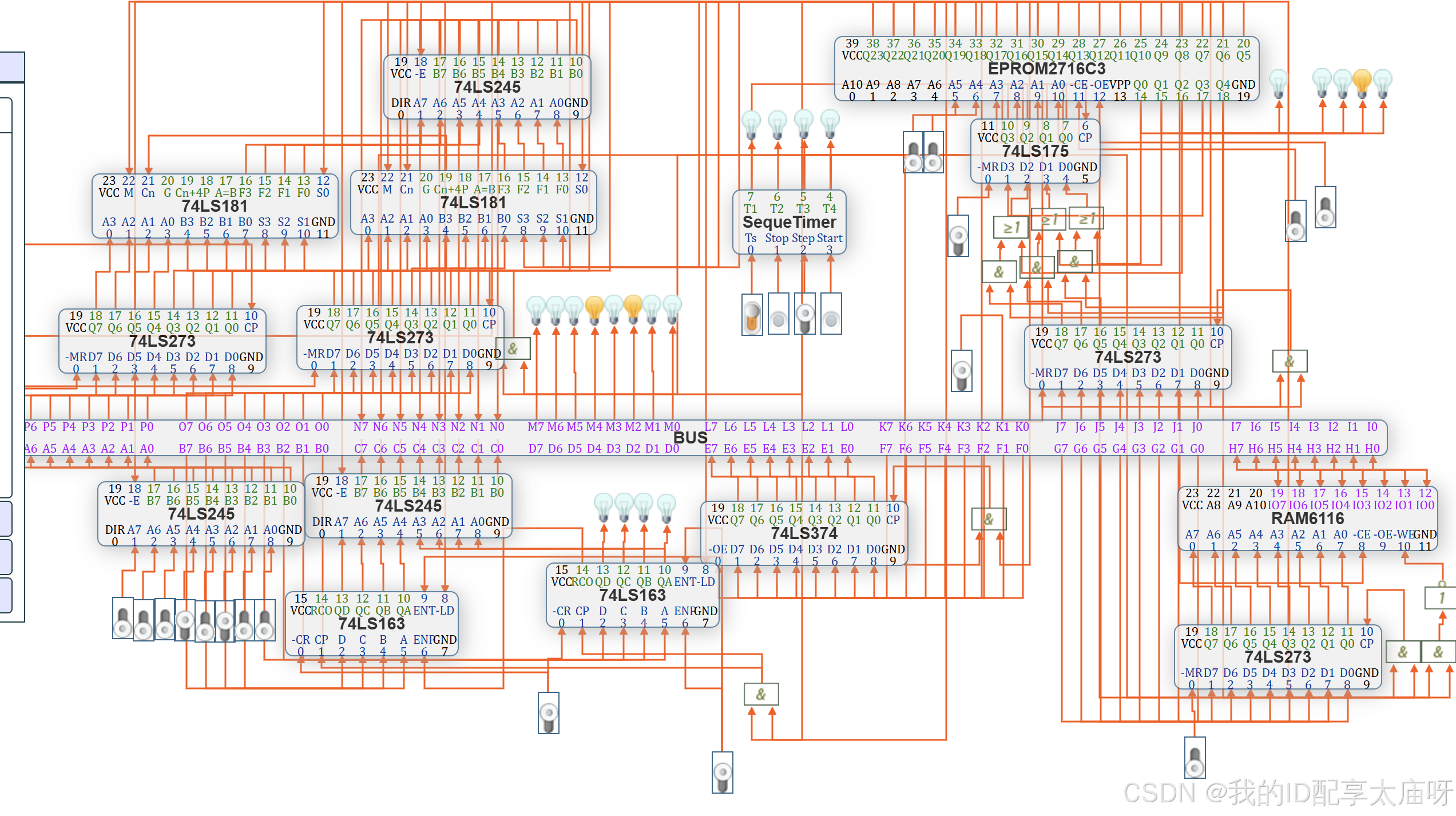

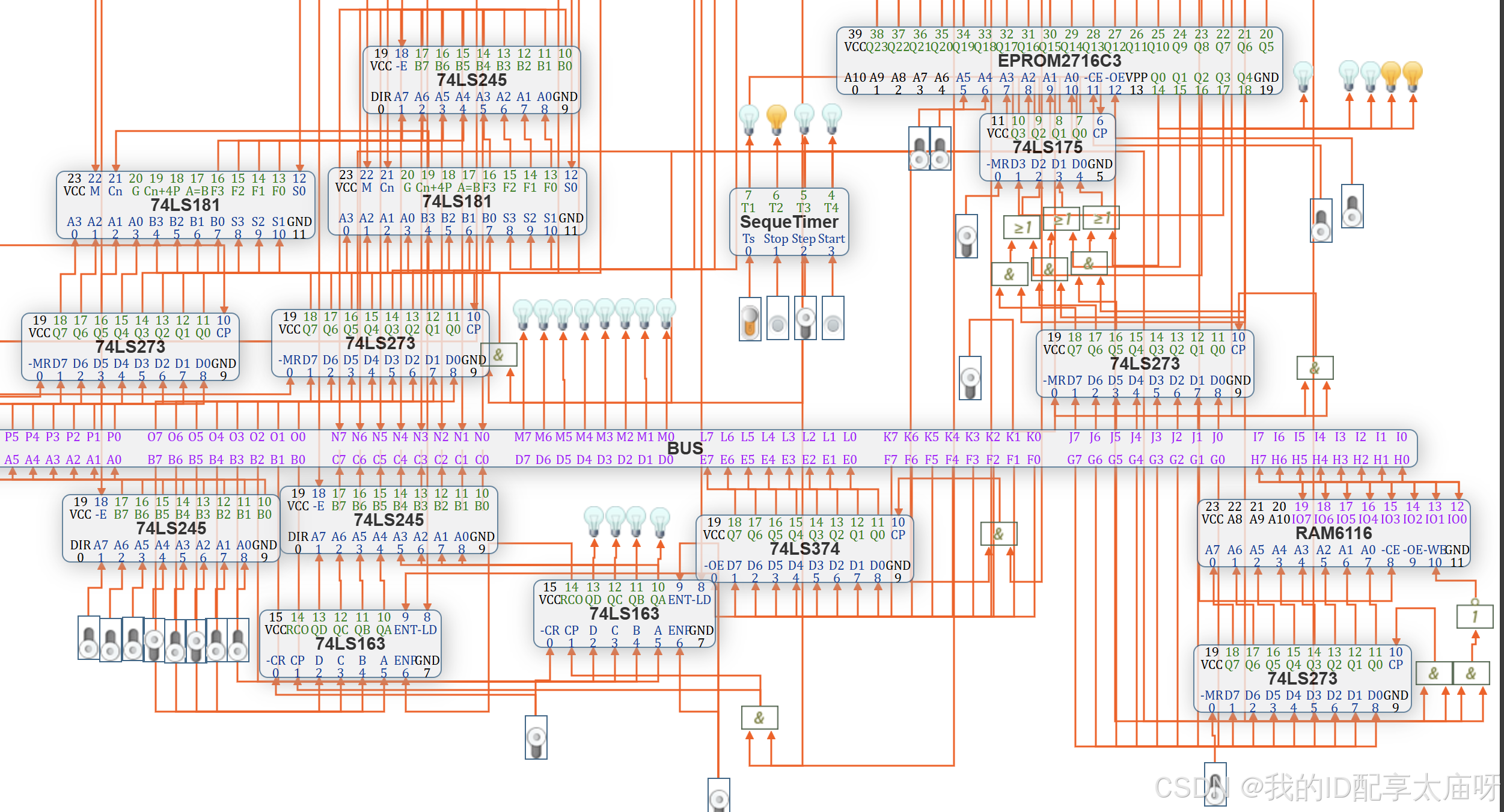

本实验综合了前面几章中实验的电路,将运算器模块、存储器模块和控制器模块通过总线连接在一起,组成了一个简单的模型机,其电路如图8-1所示。

8.4 实验原理

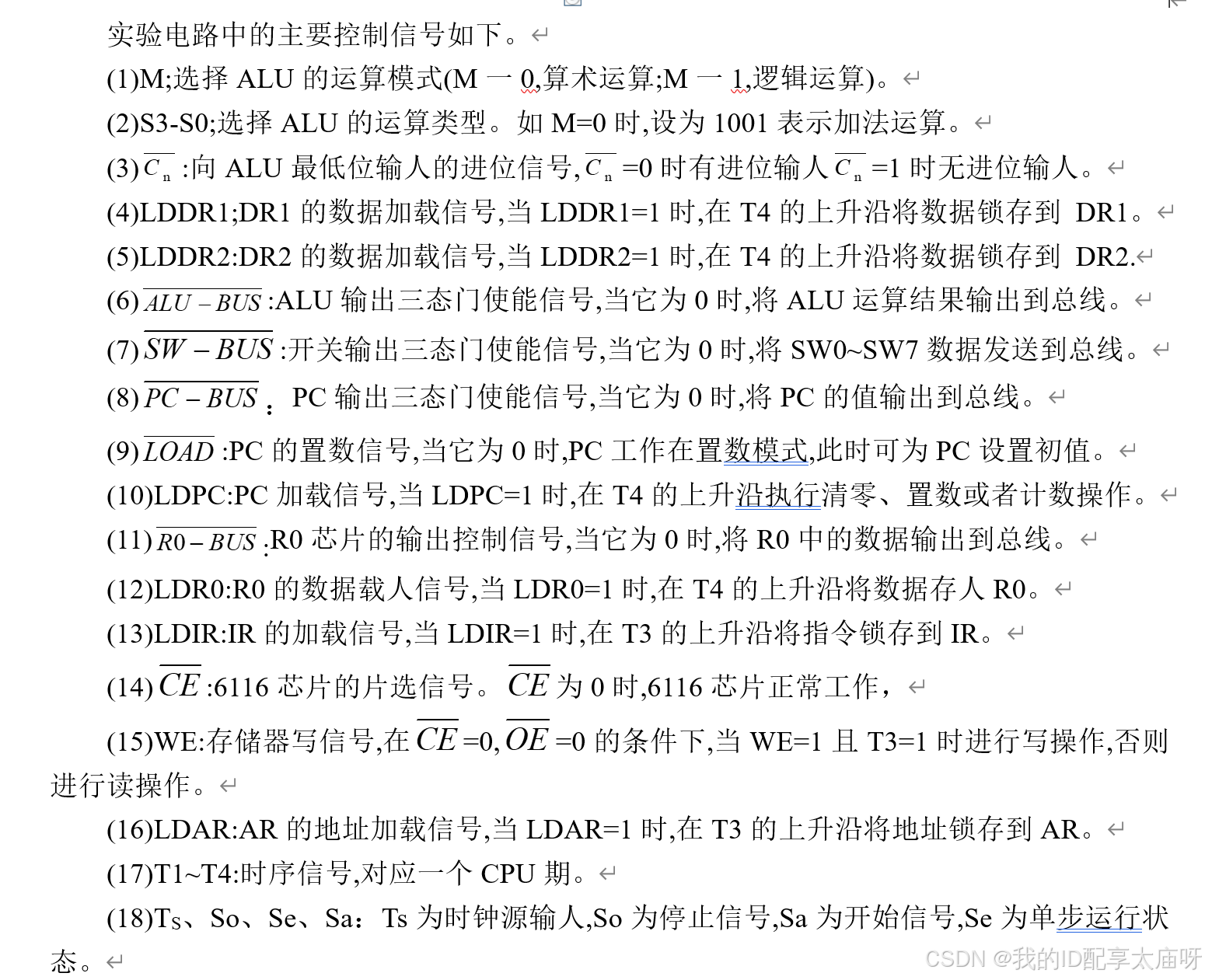

在累加器实验中,实现了通过手动设置微指令完成相应微操作;在程序计数器实验中,实现了自动依次取出机器指令存人指令寄存器IR;在控制器实验中,实现了自动按照IR中的指令逐条取出对应的微指令。

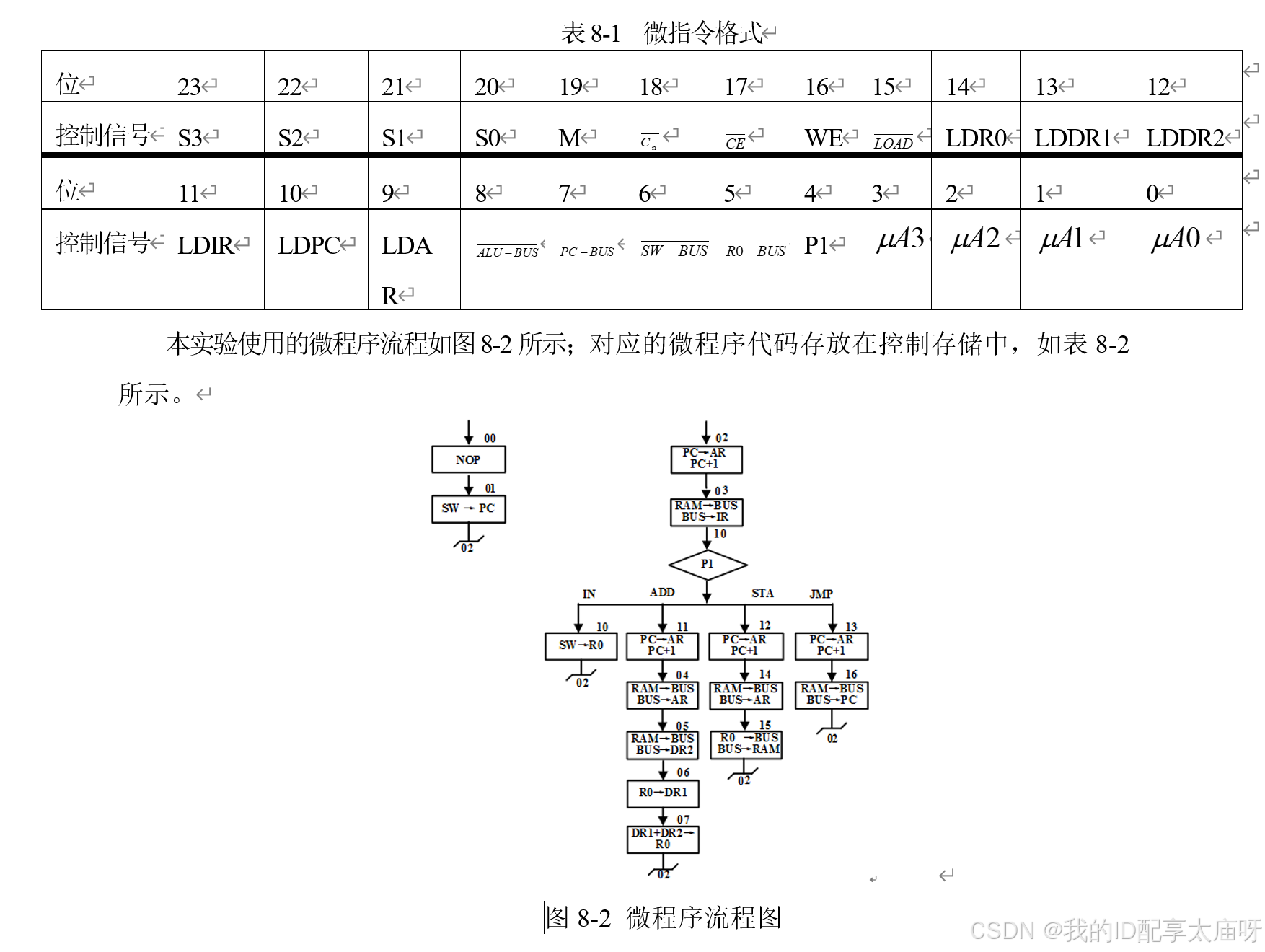

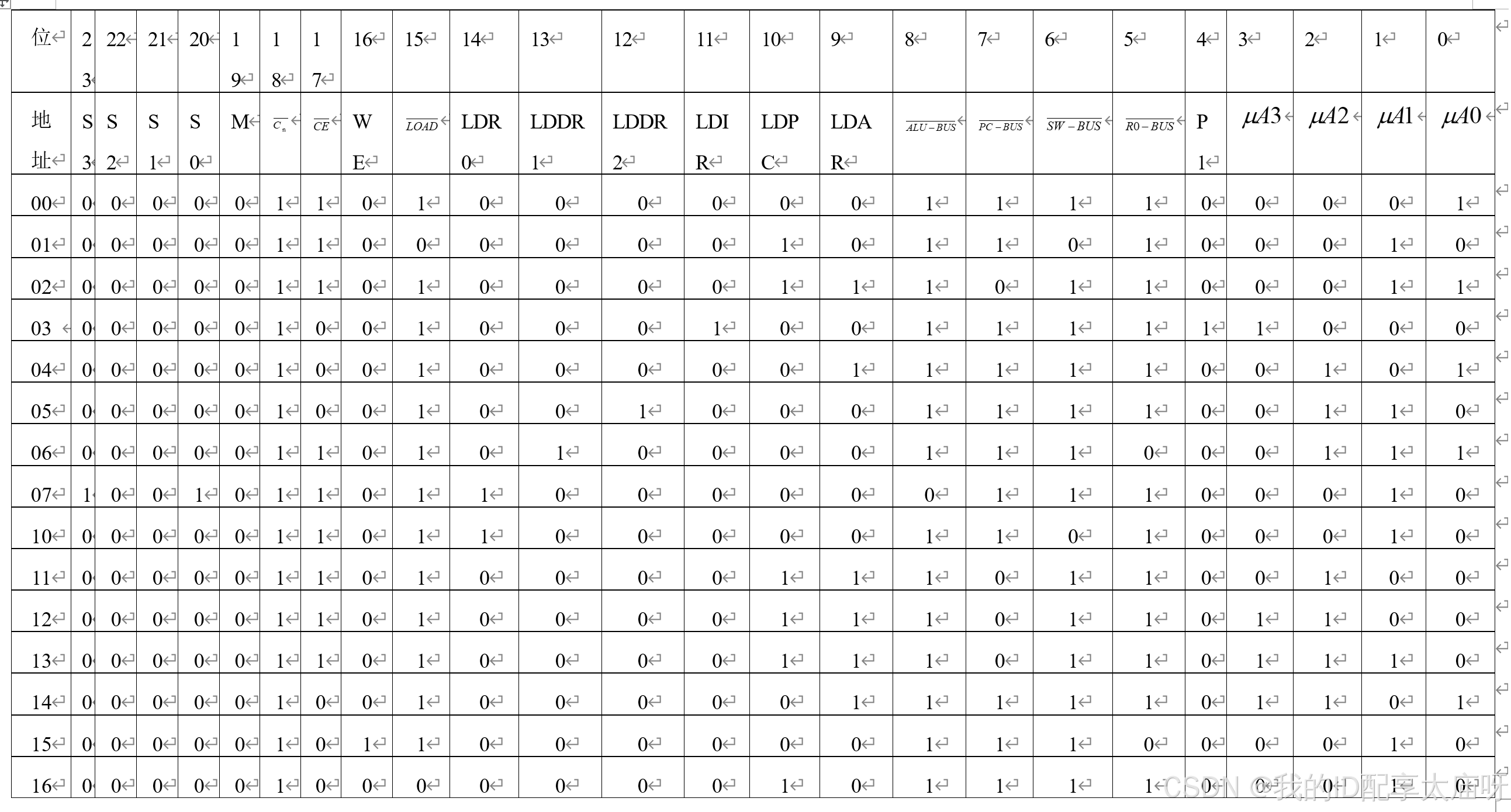

在本实验中,程序存储在RAM中,微程序存储在控制存储器中,要实现自动从RAM里逐条取出指令放人IR,并按照IR中的指令自动从控制存储器读出相应的微程序执行。本实验用到的微指令长度为24bit,微指令格式如表8-1所示。

表 8-3机器指令格式

| 助记符 | 机器码(A位内存地址8bit) | 长度/bit | 功能 |

| IN | 000XXXXX | 8 | SW→R0 |

| ADD | 001XXXXX A | 16 | R0+(A)→R0 |

| STA | 010XXXXX A | 16 | R0→(A) |

| JMP | 011XXXXX A | 16 | A→PC(程序跳转到A地址执行) |

表8-4 RAM中预存的程序和数据

| 地址(八进制) | 内容 | 含义 |

| 00 | 0000 0000 | IN |

| 01 | 0010 0000 | ADD |

| 02 | 0000 1000 | 10(八进制) |

| 03 | 0100 0000 | STA |

| 04 | 0000 1001 | 11(八进制) |

| 05 | 0110 0000 | JMP |

| 06 | 0000 0000 | 00 |

| 07 | ||

| 10 | 0000 1011 | |

| 11 | 求和结果 |

8.5 实验内容与步骤

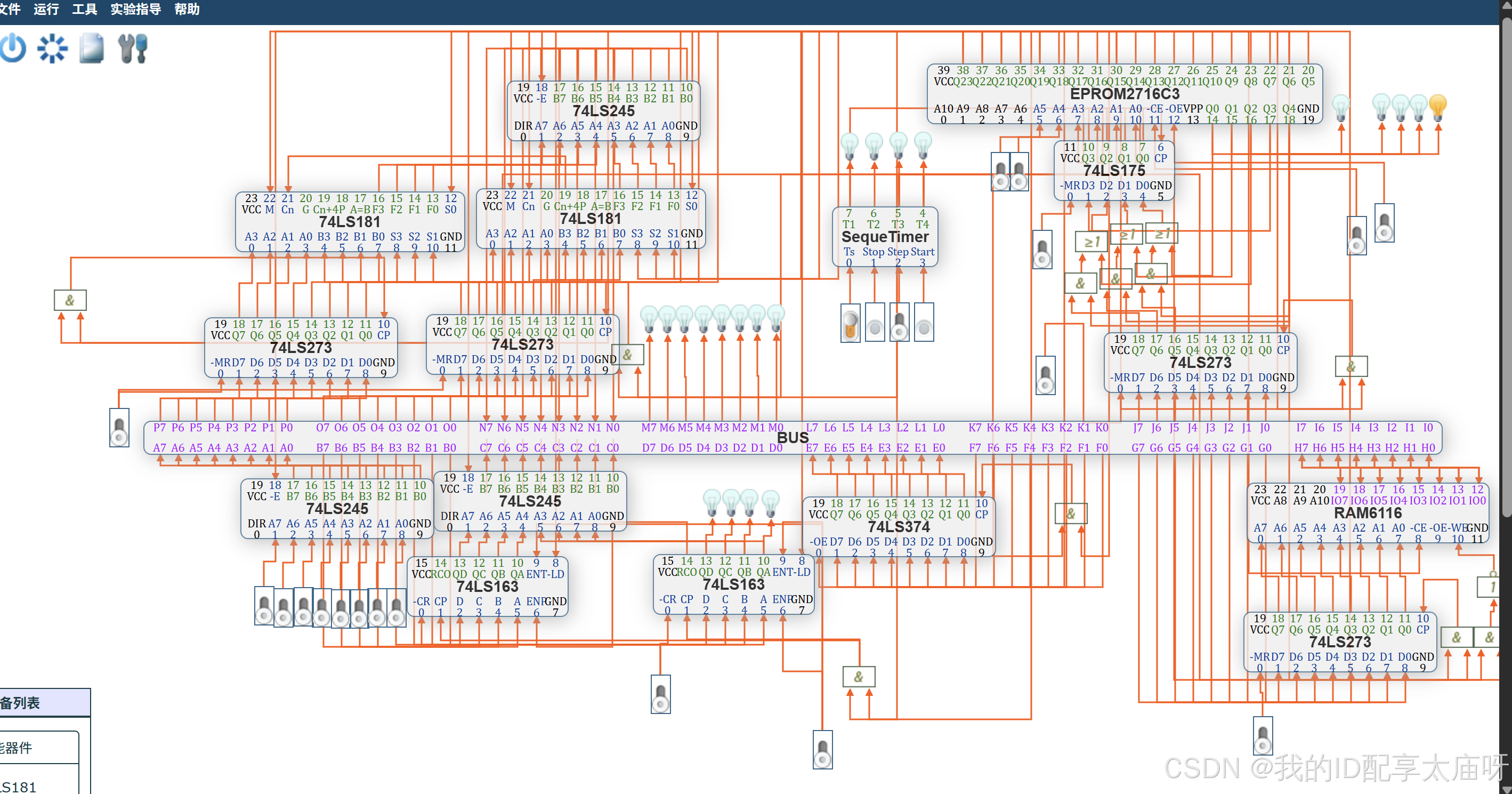

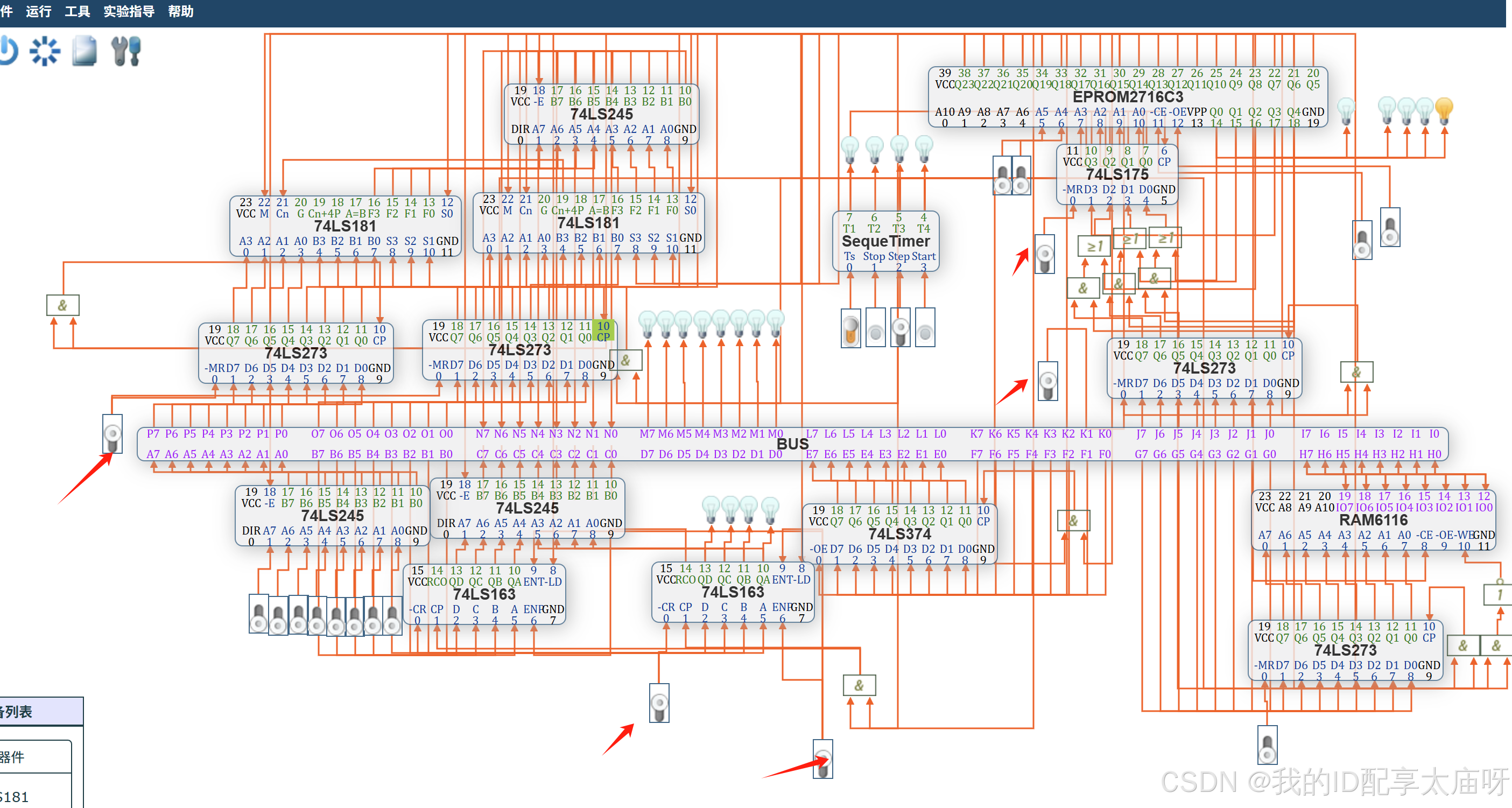

(1)运行虚拟实验系统,导人实验电路如图所示。

(2)打开电源开关。

(3)进行电路预设置。将DR1、DR2和AR的MR置1,将计数器的CR、ENT、ENP置1,时序产生器的step置1(可在开电源之前设置)。微地址寄存器74LS175和指令寄存器IR的MR置1。此时微地址寄存器和IR已初始化为零,模型机将从控制存储器的零地址开始运行。

(4)在数据开关(SW0~SW7)上设置好程序的起始地址(00000000)

(5)单击1次时序产生器的“start”按钮,思考并回答问题:此时执行的是微程序流程图中的第几条微指令?作用是什么?

第1条也就是00地址的微指令,该微指令是nop,也就是空操作指令,该指令用于控制时间周期。

(6)再单步执行2条微指令,思考并回答问题:这两条微指令的作用是什么?

第一个是SW→PC,将输入的地址存到程序计数器PC中,第二条指令是PC→AR,同时PC+1,PC是程序计数器,存放下一条指令的主存地址。AR是地址寄存器,与主存的地址总线直接连接,在从主存取数据前,存放要数据的地址。这条指令的意思是:PC值送AR,准备从主存取指令;当前PC值+1,使PC存放下一条指令的主存地址。

(7)通过数据开关(SW0~SW7)设置操作数1的值为00010100。思考并回答问题:此设置是否可以提前?如果可以,最早应该在以上第几步之后?

(8)单击“start”按钮,执行微指令SW→R0,将操作数1保存到累加器R0中。

(9)继续单步执行之后的微指令,直到第一轮循环结束。在此过程中注意观察总线上数据显示灯的显示,并说明每个显示出来的数字的意义,将表8-5补充完整

IN SW→R0 数据开关上的值00010100送入R0寄存器中

ADD R0+(A)→R0 R0中的00010100与内存地址1000中的数据00001011 相加,结果为00011111,将结果送入R0寄存器中

STA R0→(A) 将R0寄存器中的00011111值送入内存地址1001

JMP A→PC 将内存地址1000中的00011111值送入PC中

表8-5 总线数据表

| 序号 | 且线上数据 (二进制) | 微指令编号 (八进制) | 意义(地址用二进制表示) |

| 1 | 00000001 | 02 | 当前PC的值,即内存地址01 |

| 2 | 00000010 | 02 | 递增1后的PC值 |

| 3 | 00100000 | 03 | 内存地址01中的ADD指令操作码 |

| 4 | 00000010 | 11 | 当前PC的值,即内存地址10 |

| 5 | 00000011 | 11 | 递增1后的PC值 |

| 6 | 00001000 | 04 | 内存地址10中的数据,此数据也是一个地址 |

| 7 | 00001011 | 04 | 内存地址1000中的数据 |

| 8 | 00010100 | 05 | R0中的数据 |

| 9 | 00011111 | 06 | A与R0相加后的结果 |

| 10 | 00000011 | 02 | 当前PC的值,即内存地址11 |

| 11 | 00000100 | 02 | 递增1后的PC值 |

| 12 | 01000000 | 03 | 内存11中的数据 |

| 13 | 00000100 | 12 | 当前PC的值,即内存地址100 |

| 14 | 00000101 | 12 | 递增1后的PC值 |

| 15 | 00001001 | 14 | 内存地址100中的数据,此数据也是一个地址 |

| 16 | 00000000 | 14 | 内存地址1001中的数据 |

| 17 | 00011111 | 14 | R0中的数据 |

| 18 | 00000101 | 02 | 当前PC的值,即内存地址101 |

| 19 | 00000110 | 02 | 递增1后的PC值 |

| 20 | 01100000 | 03 | 内存地址101中的JMP指令操作码 |

| 21 | 00000110 | 13 | 当前PC的值,即内存地址110。 |

| 22 | 00000111 | 13 | 递增1后的PC值 |

| 23 | 00000000 | 15 | 内存地址110中的数据 |

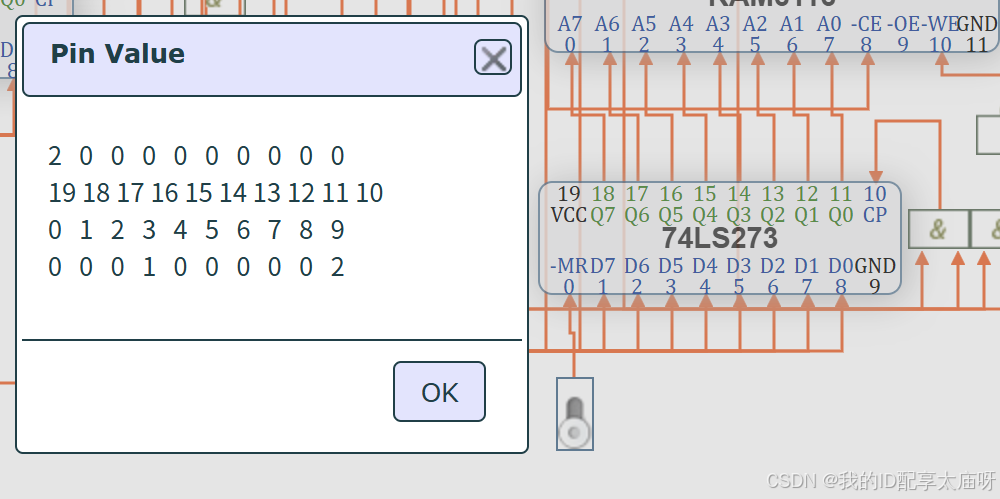

(10)利用菜单“工具/存储芯片读写”选项,查看运算结果是否已填入指定内存单元。

837

837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?