You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result, after receiving the carry-out from the first adder. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored), but the internal modules need to in order to function correctly. (In other words, the add16 module performs 16-bit a + b + cin, while your module performs 32-bit a + b).

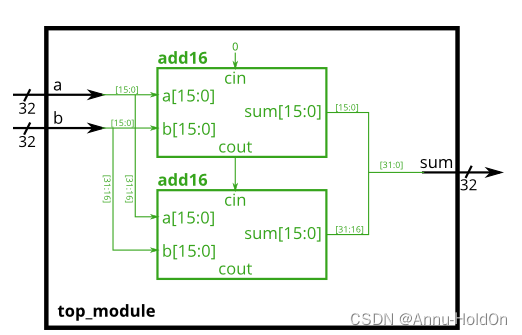

Connect the modules together as shown in the diagram below. The provided module add16 has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

您将得到一个执行16位加法的模块add16。实例化其中两个以创建一个32位加法器。在接收到来自第一加法器的进位之后,一个加法器16模块计算加法结果的低16位,而第二加法器16模块则计算结果的高16位。32位加法器不需要处理进位输入(假定为0)或进位输出(忽略),但内部模块需要处理才能正常工作。(换句话说,add16模块执行16位a+b+cin,而您的模块执行32位a+b)。

如下图所示,将模块连接在一起。提供的模块add16具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

这个也很简单,就是在例化module的时候,在接口里面注意每个信号的为快就可以了。

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire add1_cout_add2_cin;

add16 add16_1(

.a(a[15:0]),

.b(b[15:0]),

.cin(0),

.cout(add1_cout_add2_cin),

.sum(sum[15:0])

);

add16 add16_2(

.a(a[31:16]),

.b(b[31:16]),

.cin(add1_cout_add2_cin),

.cout(),

.sum(sum[31:16])

);

endmodule

870

870

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?