SL2.1A 是一颗高集成度,高性能,低功耗的 USB2.0 集线器主控芯片;该芯片 采用 STT 技术,单电源供电方式,芯片供电电压为 5v, 内部集成 5V 转 3.3V,只需 在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

芯片可以使用外部晶体,也可以使用内置晶体。如果使用内置晶体,需要 将芯片的 XI 输入接地。!建议您使用外部晶振,使用外部晶振更加稳定*。

完美支持 USB2.0 高速(480MHz),USB2.0 全速(12MHz),和低速模式(1.5MHz)

集成 12M 晶体振荡器

集成 12MHz-to-480MHz PPL(Phase Lock Loop)

采用Single Transaction Translator (STT)技术,是*TT系列中最具成本和效率方案

支持自供电到总线供电的自动枚举切换

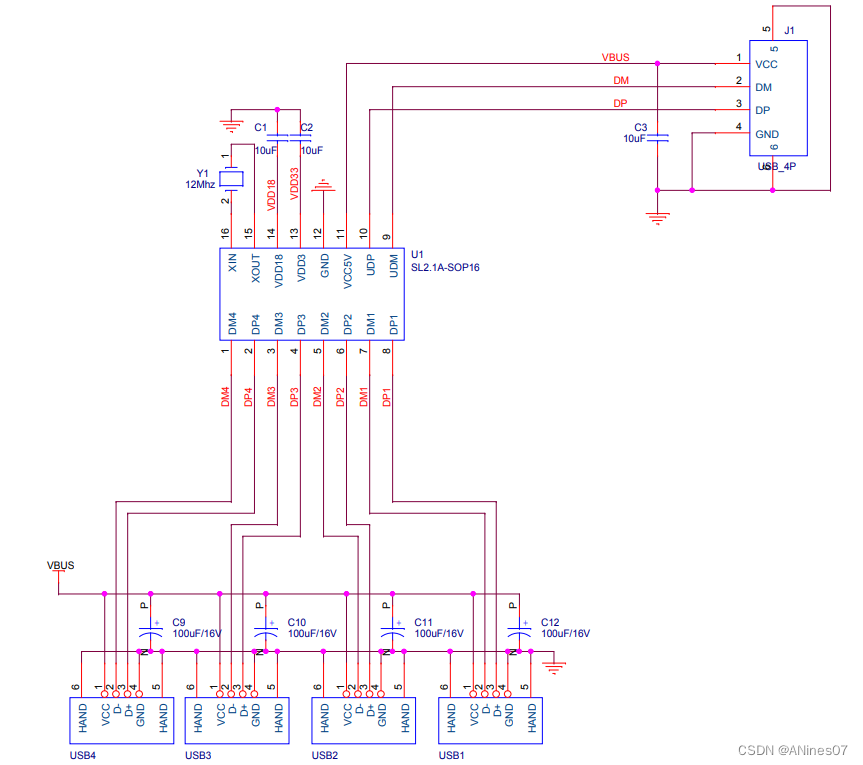

应用电路参考图

SL2.1A是一款高集成度、低功耗的USB2.0集线器主控芯片,采用STT技术,支持5V供电并内置5V转3.3V电路。芯片内置12M晶体振荡器和12MHz-to-480MHzPLL,可选外部晶振以提升稳定性。它支持USB2.0的高速、全速和低速模式,并能自动切换自供电到总线供电。

SL2.1A是一款高集成度、低功耗的USB2.0集线器主控芯片,采用STT技术,支持5V供电并内置5V转3.3V电路。芯片内置12M晶体振荡器和12MHz-to-480MHzPLL,可选外部晶振以提升稳定性。它支持USB2.0的高速、全速和低速模式,并能自动切换自供电到总线供电。

3010

3010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?