作者:AirCity 2020.1.26

Aircity007@sina.com 本文所有权归作者Aircity所有

本文内容比较零散,但每个知识点都很有用,会持续更新。

为什么需要信号完整性?

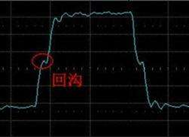

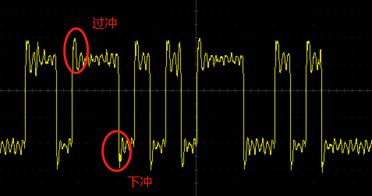

简单讲,两个需求:一是满足时序要求,走线长短要匹配。二是保证波形质量,无回沟、过冲、下冲、振铃,并保证高低电平正确。

电信号在PCB走线上的传输速度是多少?

一个简单的记忆方法是,电信号1ns在PCB板走线上能传输6inch。反过来算是1inch需要传输1/6ns.

什么信号需要考虑信号完整性?

高速信号需要考虑信号完整性问题,低速信号不需要。

高速信号的定义是信号的上升时间小于传输延迟5倍的信号(或者传输延迟大于20%上升时间)。举个例子:100MHz方波,周期10ns,上升时间1ns。20%是0.2ns,对应的PCB走线长度是0.2nsx6inch/ns=1.2inch(相当于30.48mm)。当这个上升沿是1ns的方波在长度超过1.2inch的走线上传输时,就会遇到信号完整性问题。这个例子中,1.2inch并不是很长的走线,在PCB上很有可能遇到,所以100MHz很有可能会遇到信号完整性问题,更高速的信号,更有可能会遇到信号完整性问题。

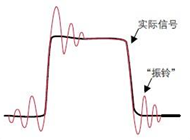

再强调一遍,信号传输延迟大于20%信号上升时间,将会遇到信号完整性问题!这是一个经验法则,下图仿真结果能佐证这个法则,当传输延迟TD大于20%上升时间RT后,信号明显出现了振铃。

经验法则的延伸:

在上面的举例中,1ns的上升时间,如果传输线长度大于1.2inch,就会遇到信号完整性问题,用公式标识一下:

信号上升时间是Tr(ns),电信号传输速度是6inch/ns,那么不会遇到信号完整性问题的传输线长度Lmax最大是:

Lmax=Tr x 1/5 x 6=1.2Tr

何保证信号完整性?

有几个要点:阻抗要匹配,阻抗要连续,走线长度要匹配。

什么是阻抗连续?

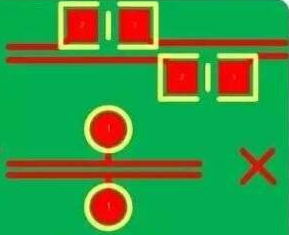

“高速”信号在PCB的走线上传输,这根走线就是传输线,传输线有自己的特性阻抗(什么是特征阻抗参见文章《什么是特征阻抗》),一般是50Ω,特征阻抗值得计算,离不开参考平面(地平面或电源平面),如果参考平面是完整的,那么这根传输线的特征阻抗是连续的。如果这个平面是不完整的,如下图,传输线经过了这个不完整的“沟壑”,在这个“沟壑”处,传输线的阻抗会瞬间变大,这就是阻抗不连续。阻抗不连续的地方,信号能量会被反射,信号质量会变差。

除了地平面不完整导致的阻抗不连续,PCB走线粗细变化,分叉,也会导致阻抗不连续如下图:

信号反射是什么,怎么计算?

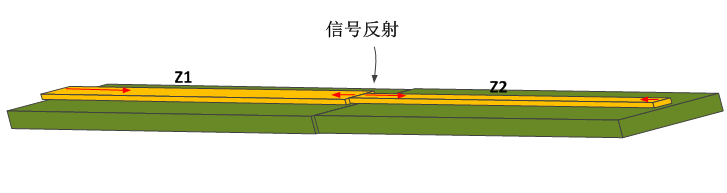

传输线才会遇到信号反射,不是传输线,没有信号反射问题。如下是一根传输线,走线宽度突然发生了变化,产生了阻抗不连续。第一段特征阻抗是Z1,第二段特征阻抗是Z2.

信号的反射系数是:

ρ=(Z2-Z1)/(Z2+Z1)

举个例子,假设幅度是1V的信号在50Ω传输线上传输,这根传输线遇到了一个参考平面不连续的点,阻抗突然变成了100Ω,这个阻抗突变的点,反射系数是:(100-50)/(100+50)=1/3,因此将有1/3V的信号被反射回去。

反射系数这么定义,但这个公式是怎么推到出来的?可以这样理解,在阻抗不连续的分界面两侧,电信号的总能量(功率)是一样的,如果不一样,能量将转化为电场和磁场传播出去,而且是无限大,这不可能。为了维持“能量守恒”这个定律,并且两边阻抗都已经不一样了,必定有一部分能量被反射(反射可能是正的也可能是负的)。

如何利用这个反射系数计算界面处电压?

举例1:

1V信号沿50Ω传输线传播,传输线末端开路,阻抗是无穷大。此时的反射系数是1,因此将有1V的信号反射回去。此时我们在传输线末端,能的两到1V+1V=2V的电压。注意,阻抗不连续点的入射点电压=入射信号x(1+ρ);

举例2:

1V信号沿50Ω传输线传播,传输线末端对GND短路,阻抗0。此时的反射系数是-1,因此将有-1V的信号反射回去。此时我们在传输线末端,能的两到1V+(-1V)=0V的电压。

举例3:

1V信号沿50Ω传输线传播,传输线末端阻抗也是50Ω,阻抗连续。此时的反射系数是0,因此没有信号反射。此时我们在传输线末端,能的两到1V的电压。这种情况我们称之为“阻抗匹配”。

结一下规律:

在阻抗不连续点的右侧(上图Z2区域),如果阻抗变小,反射系数是负的,负信号降沿着Z1返回,入射电压降低一部分后,沿着Z2传播;

在阻抗不连续点的右侧(上图Z2区域),如果阻抗变大,反射系数是正的,正信号降沿着Z1返回,入射电压增大一部分后,沿着Z2传播;

什么是阻抗匹配?

这个匹配是指信号源与传输线的阻抗是一样的,或者传输线阻抗与负载阻抗是一样的,很多人搞信号完整性设计,知道方法却不知道深层次的原因。下图利用“反射系数”和真实电路模型来介绍串联和并联匹配的原理。

串联匹配的原理:

芯片的输出管脚是信号源,对于CMOS工艺,其内阻通常是5-20Ω左右,老的晶体管工艺,阻抗比较高,大概100Ω。

如下是一个信号传输模型,信号源是1V方波,R0是信号源内阻,传输线特征阻抗是50Ω。

这根传输线的的长度是6inch,传输延迟是1ns,信号源的波形是1V方波。信号到达A点,根据分压原理,A点电压是1Vx50/(50+10)=0.84V,也就是说由,是这个0.84V的电压进入传输线传播电压。

有些人会有疑问,为什么这个地方会用分压原理,不用反射系数来计算。注意,信号源到50Ω传输线的走线长度非常非常短,可以认为反射是瞬间完成,或者干脆认为没有反射。这个时候可以用直接用分压原理计算电压。当然也可以用反原理来计算,但最终结果都是一样的。关于分压原理与反射系数的关系讨论,请见这个文章《信号完整性的反射问题》

0.84V电压到达传输线末端,由于末端是开路,阻抗无穷大,将反射0.84V电压,此时在B点能测到1.68V电压。

再经过1ns,反射回的1.84V电压到达A点,A点的反射系数是(10-50)/(10+50)=-0.67,这是将有-0.67x0.84V=-0.56V电压反射回传输线。

如此往复,在不同的时间点,B点将测量到多个电压,如下图:

上图是B点的波形,我们看到阻抗的不匹配会导致信号的过冲,下冲,振铃。

如果测量A点,波形将更加复杂。即使符合信号完整性的电路,A点的波形也很复杂,所以测试信号完整性,一定是在负载端测量波形。

如果在源端输出的地方,增加40Ω电阻,这个40Ω电阻与源内阻共同组成了50Ω源内阻。根据分压原理,1V的方波到达C点,电压是0.5V,这个电压沿着传输线传播到B点,然后有0.5V的电压反射回来,这是在B点测得的电压正好是1V。反射回的0.5V电压,到达C点,C点的反射系数是0,因此不再有信号反射回传输线。此时我们认为信号得到了匹配。

并联匹配原理:

下图是并联匹配的电路模型,并联匹配的关键点时B点的反射系数为0,因此信号源出来什么信号,到达B点就是什么信号。

还有一种上拉到电源的并联匹配方法,原理是一样的。这种方法在DDR电路中很常见,并且DDR3开始,这种匹配电阻已经集成到了芯片内部,虽然说功耗高,但为了高速信号的质量也必须这么做。

什么PCB的走线阻抗误差要求±10%

假设阻抗突变增加10%,反射系数ρ=(1.1-1.0)/(1.1+1.0)=4.76%;

假设阻抗突变减小10%,反射系数ρ=(0.9-1.0)/(0.9+1.0)=5.26%;

通常情况下,我们要求信号幅度噪声控制在5%左右,因此PCB的走线阻抗误差要在±10%以内。

短桩线(Stub)对信号完整性的影响

假设短桩线在传输线的中间,阻抗与传输线一致,根据仿真结果,得出一个经验法则:如果短桩线长度小于信号上升时间的1/5,其影响可以忽略不计。例如信号上升时间是1ns,最大允许的短桩线长度是1ns x 1/5 x 6inch/ns =1.2inch;总结成公式就是:Lstub_max=1.2Tr

所以说对于上升时间是1ns的信号,小于1.2inch的传输线,不会带来信号完整性问题,即使有1.2inch的分叉,也不会带来什么影响。

很多芯片都是BGA封装,走线势必有分叉,并且芯片封装上的引线也是分叉,但这些分叉都很短,不会引起信号完整性问题。当然如果芯片运行频率非常高,对分叉长度的要求也会更高。

阻抗不连续对信号完整性的影响

假设在Z2处,阻抗发生了突变,变成了75Ω,那么A处的反射系数=0.2,B处的反射系数=-0.2;如果Z2处的长度很短,那么A和B两个地方的反射因为刚好相反,所以可以迅速抵消,以至于对信号完整性的影响可以忽略不计。特别注意,只有突变幅度不大的地方,才可以这么近似认为“迅速抵消”,如果阻抗变化非常大,超过1倍以上,这个“近似”就不适用了。

根据仿真得到的经验法则:

如果阻抗突变处的长度小于信号上升沿时间的1/5,就不会对信号完整性有影响。总结成公式就是Limp_max=1.2Tr

阻抗不连续对信号完整性的影响就是过冲,下冲,振铃。

什么是走线长度匹配?

长度匹配的主要目的是满足协议要求的建立时间,保持时间!这些协议包括DDR规范,SPI总线协议,MIPI总线协议等。长度匹配是非常简单的基本原则,每次走线必须检查。

经验法则(非常实用)

- 英寸与毫米转换:1inch=25.4mm

- 信号在PCB走线上传输速度约6inch/ns

- 传输延迟大于信号上升沿时间的20%,就称为高速信号,要考虑信号完整性问题。例如:上升时间是1ns,长度超过1.2inch(0.2ns延迟)的走线就要考虑信号完整性问题。

- 传输线中间的短桩线长度不得超过1.2xTr,否则会出现信号完整性问题。例如:信号上升时间是1ns,短桩线长度不得超过1.2inch。

- 走线中间的阻抗突变区域,长度不得超过1.2xTr,否则会出现信号完整性问题。例如:信号上升时间是1ns,阻抗突变长度不得超过1.2inch。

- 负载端的容性负载会导致上升沿变缓,τ10-90延迟时间约等于2.2xRC。例如:50Ω传输线,负载电容3pf,延迟增加330ps。

- 传输线中间的容性突变如果小于0.004Tr,则不会产生信号完整性问题。例如:信号上升时间是1ns,容性突变小于4pf,不会产生信号完整性问题。

- 传输线中间的容性负载,对上升沿的延迟累加(50%门限的延迟)等于0.5xRC。例如:50Ω传输线,容性负载突变2pf,对信号的延迟累加为50ps。

参考资料:

《信号完整性分析》Eric Bogatin著

老美的文章写的深入浅出,非常牛,看看之后,你基本上就不需要看网络上的各种文章了。

1623

1623

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?