2021.4.1

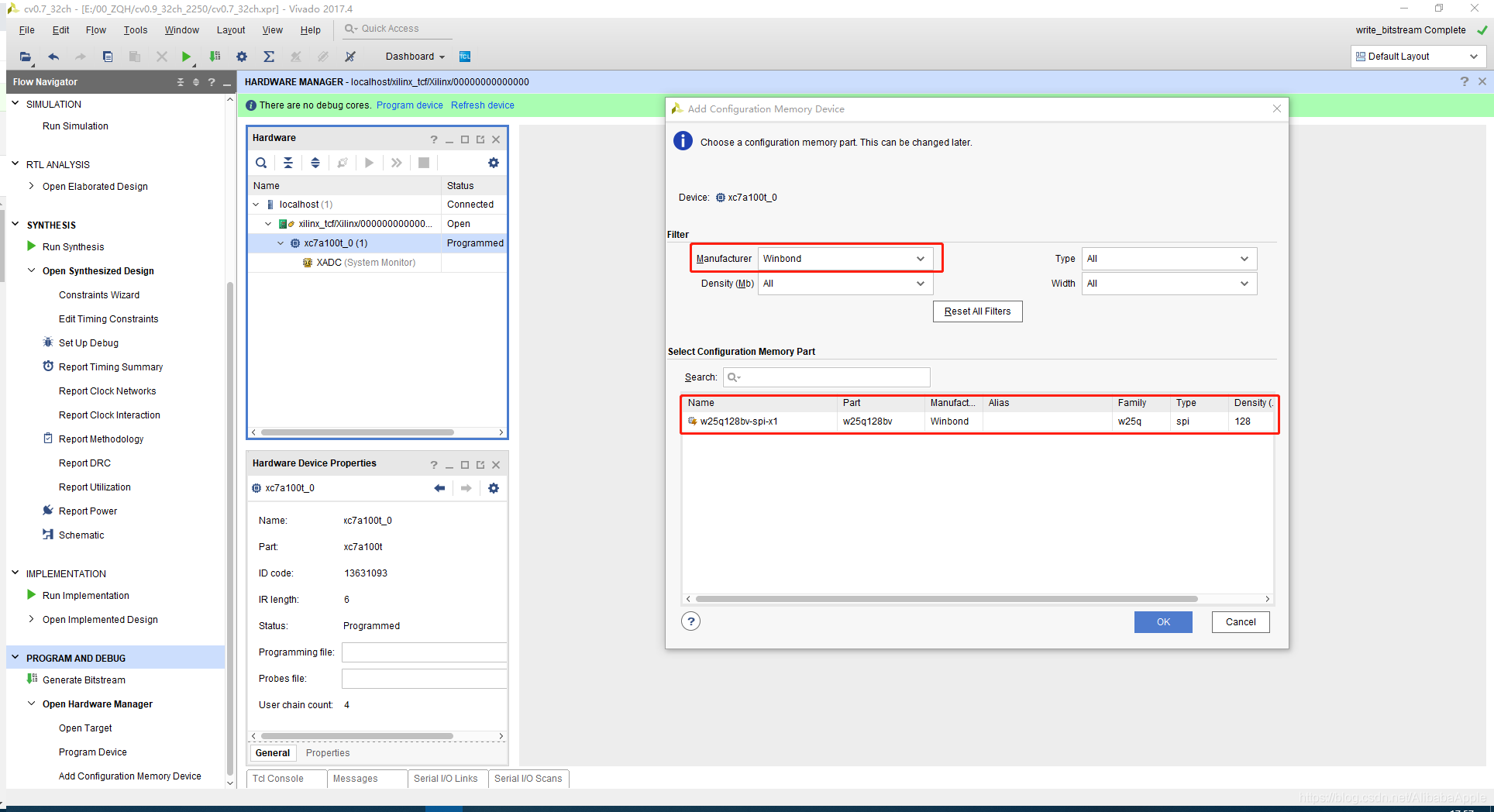

烧写MCS文件,选择winbond

代码报错

综合vivado报错时,(如果确认不是逻辑问题)注意是不是代码大小写问题,这时候,你需要做的是,将报错代码

手打,手打,手打,

重要的事情写三遍。

dbg调试

在代码中添加好以下这些信号后,需要综合或者实现后(如下所示),才能看到这些dbg信号。

使用Vivado17.4来抓取波形的时候,会遇到一些问题,比如,我想要观察的信号,在网表中找不到,那该怎么办呢?

在代码中添加几句常用语句可以解决这个问题。

1.一般在模块之前加上这句:(* KEEP_HIERARCHY="YES"*)。

例如:

(* KEEP_HIERARCHY="YES"*)module ads1018(

output reg ads_clk ,

output reg ads_din ,

output reg ads_cs ,

output reg [11:0] ain_0 ,

output reg [11:0] ain_1 ,

output reg [11:0] ain_2 ,

output reg [11:0] tempr ,

input clk_40 ,

input rst_n ,

input ads_dout

);

2.可以加这句:(* KEEP="TRUE"*) 。

例如:

(* KEEP="TRUE"*) reg ads_clk ;

(* KEEP="TRUE"*) reg ads_din ;

(* KEEP="TRUE"*) reg ads_cs ;

(* KEEP="TRUE"*) reg [11:0] ain_0 ;

(* KEEP="TRUE"*) reg [11:0] ain_1 ;

(* KEEP="TRUE"*) reg [11:0] ain_2 ;

(* KEEP="TRUE"*) reg [11:0] tempr ;

3.还是不行的话加这句:(* DONT_TOUCH="TRUE"*) 。

例如:

(* DONT_TOUCH="TRUE"*) wire clk_40;

(* KEEP="TRUE"*) wire rst_n;

(* KEEP="TRUE"*) wire ads_dout ;

这几句的详细区别可以参考以下一些图片:

在调试的时候,为了防止一些需要观察的信号被优化掉,可以暂时在vivado中的设置中,修改一些设置。等调试完了之后,再将其改回原来的值。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?