VerilogHDL程序设计与仿真作业3:

——实现74HC4511的功能

一、实验目的

- 实现74HC4511的功能

二、

1、设计思路

- 功能表

- 功能表(续)

2、实现代码

//文件名称:_74HC4511.v

//fuchaoxinHUST11152020

module _74HC4511(D,LE,BL_,LT_,L);

input LE,BL_,LT_;

input [3:0] D;

output reg [6:0] L;

/*说明:

输入端:LE BL_ LT_决定了74HC4511的工作状态,[3:0]D只有前十个数能够得到相应的输出,其余全部是无效输出。

输出端:[6:0]L从高位到低位分别代表了a-g,决定灯的亮与灭,高电平有效。

*/

always @(*) begin

if (LE==0&&BL_==1&<_==1) begin

case(D[3:0])

4'b0000: L[6:0]=7'b1111110;//0-9 a为高位 g为低位

4'b0001: L[6:0]=7'b0110000;

4'b0010: L[6:0]=7'b1101101;

4'b0011: L[6:0]=7'b1111001;

4'b0100: L[6:0]=7'b0110011;

4'b0101: L[6:0]=7'b1011011;

4'b0110: L[6:0]=7'b0011111;

4'b0111: L[6:0]=7'b1110000;

4'b1000: L[6:0]=7'b1111111;

4'b1001: L[6:0]=7'b1111011;

default L[6:0]=7'b0000000;

endcase

end

else if (LT_==0) L[6:0]=7'b1111111;//灯测试

else if (BL_==0&<_==1) L[6:0]=7'b0000000;//灯熄灭

else L<=L;// LE=BL_=LT_=1时 锁存

//也可以使用else和casex语句

end

endmodule

3、测试代码

//文件名称:Test_74HC4511.v

//fuchaoxinHUST11152020

`timescale 10ns/1ns

module Test_74HC4511;

reg LE,BL_,LT_;

reg [3:0] D;

wire [6:0] L;

_74HC4511 U0(D,LE,BL_,LT_,L);//实例化元件

initial

$monitor($time,":\t D=%b, LE=%b, BL_%b, LT_%b, L%b \n", D, LE, BL_, LT_, L);

//监视器的显示内容

initial begin

//正常显示

LE=0; BL_=1; LT_=1; D[3:0]=4'b0000;

#5

LE=0; BL_=1; LT_=1; D[3:0]=4'b0101;

#5

LE=0; BL_=1; LT_=1; D[3:0]=4'b1111;//熄灭

#5

//灯测试

LE=1; BL_=1; LT_=0; D[3:0]=4'b0101;

#5

//灯熄灭

LE=1; BL_=0; LT_=1; D[3:0]=4'b0101;

#5

// LE=BL_=LT_=1时 锁存

LE=1; BL_=1; LT_=1; D[3:0]=4'b0101;

#5

$stop;//停止模拟仿真

end

endmodule

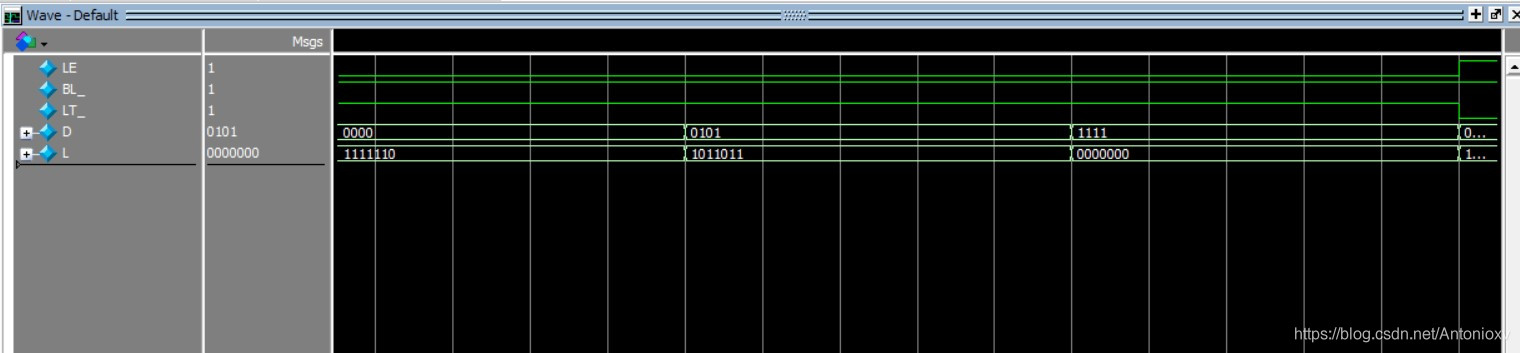

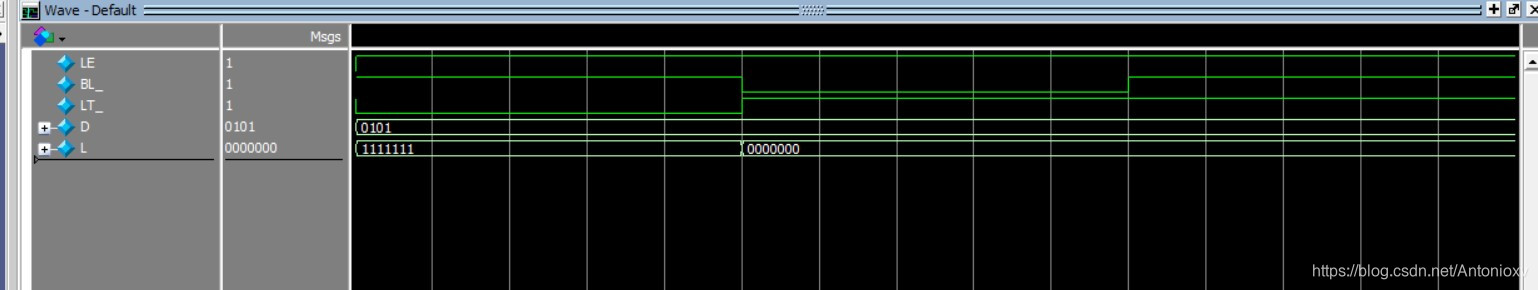

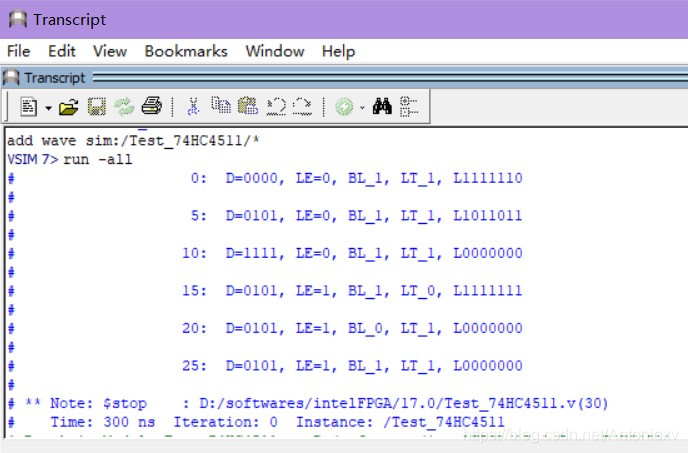

4、仿真

-

波形

-

监控器

4670

4670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?