文章目录

概述

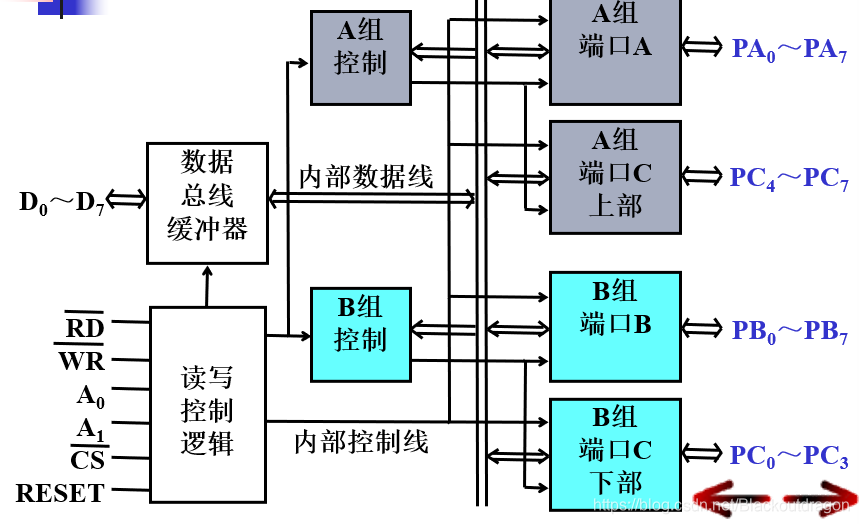

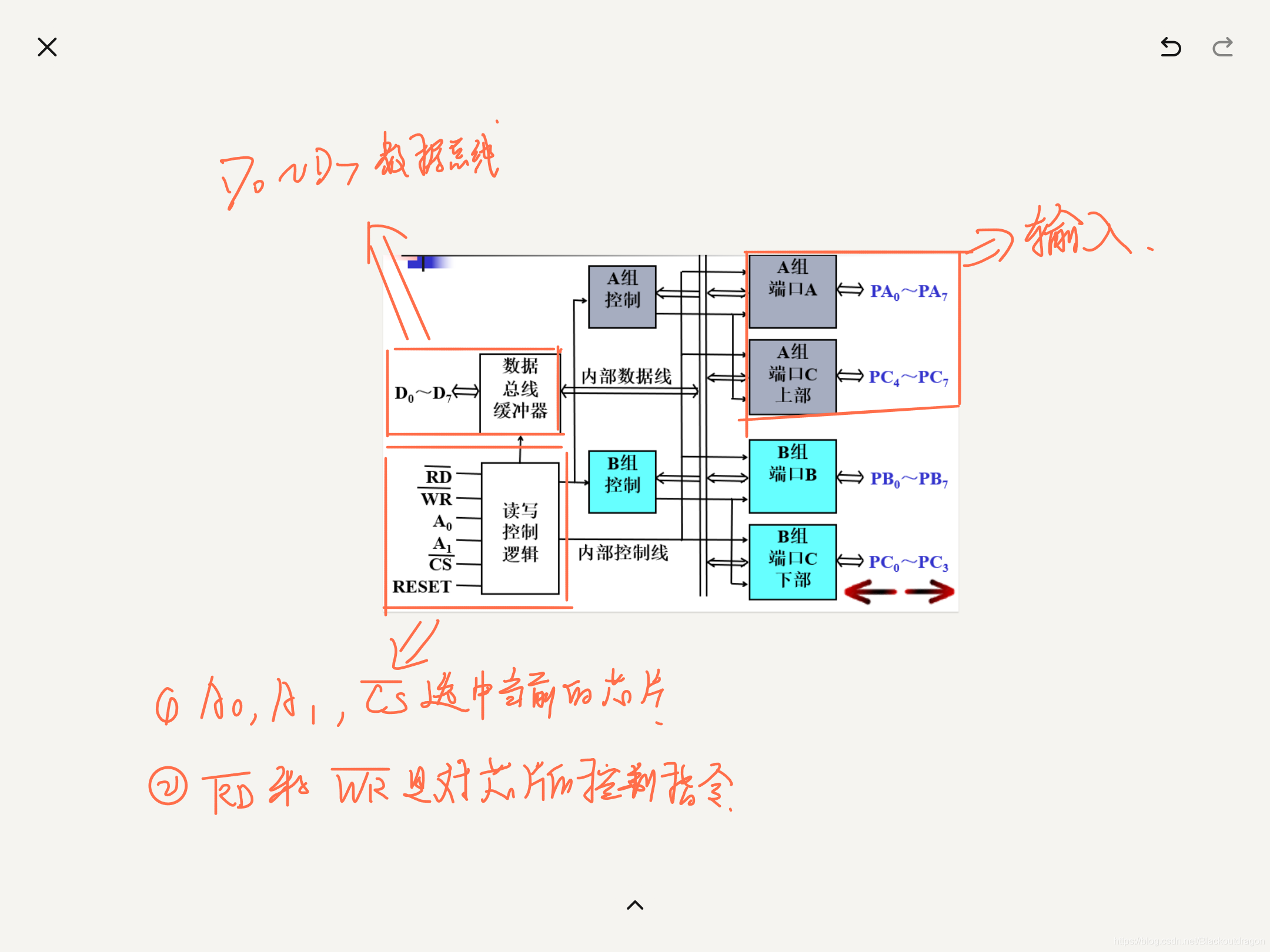

- 具有多种功能的可编程并行接口电路芯片

- 最基本的接口电路:三态缓冲器和锁存器

- 与CPU间、与外设间的接口电路:状态寄存器和控制寄存器

- 还有端口的译码和控制电路、中断控制电路.

- 分3个端口,共24个外设引脚

- 共三种输入输出工作方式

内部结构图和具体引脚功能

端口A

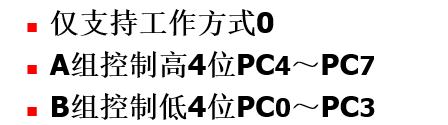

端口B

端口C

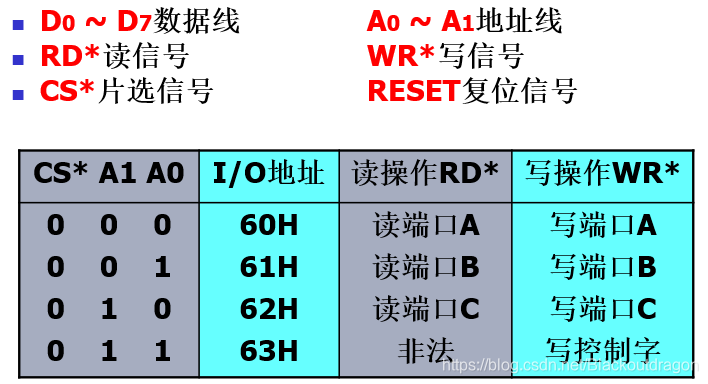

与处理器的接口

工作方式0

- 概述:基本输入输出方式

- 适用于无条件传送和查询方式的接口电路

写在时序前面的话

-

关于时序的理解我是有很多的问题的,首先就是对一个芯片组来说,如果对数据写入和写出,必须同时选中当前的芯片也就是地址码和片选信号,然后就是输入控制信号,才能进行读和写.

-

针对读入外部数据而言,数据一定要在能够读入之前就要准备好,不然就不能顺利读入/。

-

针对写出CPU内部的数据而言,数据一定要能够在写出之前就已经准备好

-

基本得顺序就是

- 先选中对应的内存单元,才能够对其进行控制读和写。

- 读也好,写也罢,都是要先将被操作的数据在被操作之前准备好。

- 而变化之后时间点,实在操作时间中间发生的。

-

时序是人为规定,为了让整个程序合理运行设定的,并不是相互触发引起的。最后写入或者读出的那一部分时候别的事件引起和变化,并不是有自身决定的

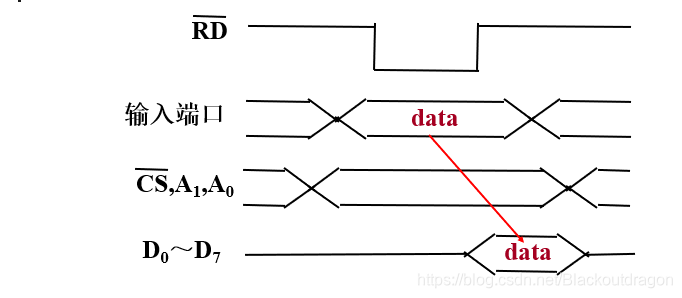

输入时序

输入无锁存,这里就有问题了,那这里哪来的数据缓冲作用

只有选中了对应的信号,并且对应的输入符合对应有效电平要求才能对数据进行输入

- 对地址进行译码,选中芯片,cs和A0,A1

- 输入端口也就是PA0,按照周期读入数据,并且一定要在控制信号来之前准备好,控制信号走之后消失

- RD控制信号,读入外部的数据,遇到第一个低电平,将data中的数据写入到缓存器中,其实这个时候输入端口的数据就可以消失了。

- 在遇到一个高电平,就会将缓存器中的数据写到数据总线上,也就是D0到D7

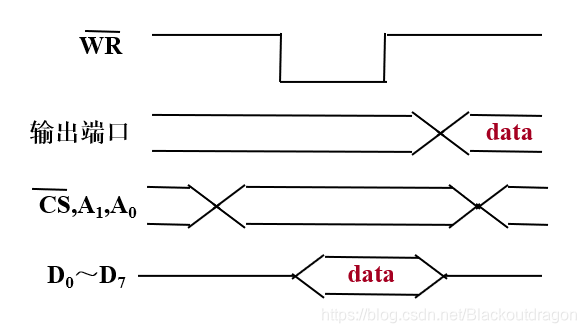

输出时序

- 对地址进行译码,选中芯片,cs和A0,A1

- 在接通写出端之前,数据应该是已经准备好的,也就是data,**但这里并没有准备好??**而且比写的信号来的之后,但这无伤大雅,已经接通了,直接写出到输出端口??

- 这里难以理解的就是为什么数据写出到输出端口会出现的延迟,是有什么控制,这个时序应该是由外部事件决定的,不是有自身决定的

工作方式1

- 概述:选通输入输出方式

- 适用于查询和中断方式的接口电路

我的问题,就是这还是用的那个芯片吗?咋没看见cs,A0和A1等等

- 适用于查询和中断方式的接口电路

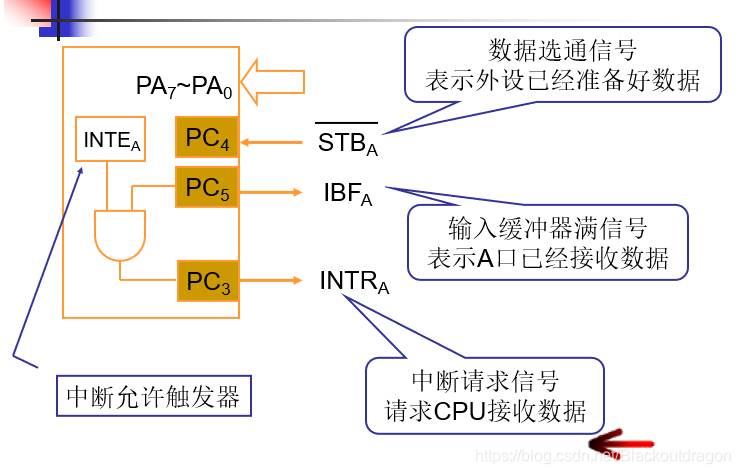

输入

结构功能图

数据选通信号,表示外设已经准备好数据。strobe,阀门

数据选通信号,表示外设已经准备好数据。strobe,阀门

- 选通信号,低电平有效,当其有效时,将输入设备送来的数据锁存在输入锁存器中

输入缓冲器满信号,表示A口已经接收到数据,input buffer full 输入缓冲区满。

输入缓冲器满信号,表示A口已经接收到数据,input buffer full 输入缓冲区满。

- 输出的联络信号,当其有效时,数据已经锁存在输入锁存器中。高电平有效

中断请求信号,请求CPU接收数据

中断请求信号,请求CPU接收数据

- 用于向CPU提出中断请求,要求CPU读取外部数据

中断允许触发器,允许中断发生。

中断允许触发器,允许中断发生。- 方式一需要借用端口C用作联络信号他,同时具有中断请求和屏蔽功能

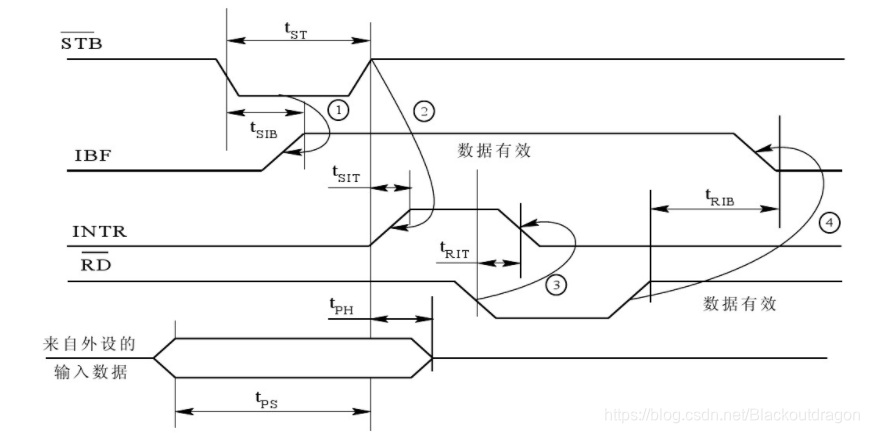

输入时序

- 当外设数据送到8255A的某个端口的数据线上时,发出STB低电平,输入端口的数据已经存入输入锁存器中。

- 输入缓冲区的数据已经满了,然后IBF变高,表示输入缓冲区已经满了,告诉外设停止输入数据。同时这是给CPU用来查询数据的状态位,在IBF变高的这段时间,都表示数据有效。

- 选通输入信号结束之后,向CPU发送中断请求信号,INTR变高,箭头2。

- 中断请求服务发出读的信号,读信号的下降沿,将中断信号消除,对应的是箭头三

- 当输入读入完毕时,将IBF数据区清空,对应箭头4,也就是箭头4

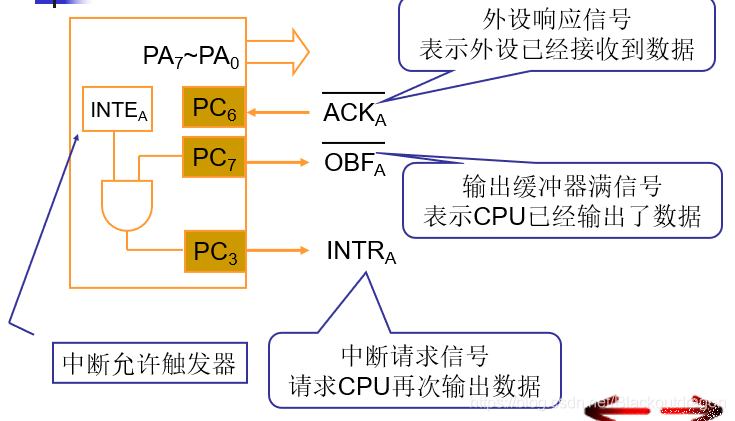

输出

结构功能图

-

外设响应信号,表示外设已经接收到数据,ack信号有效之后,会使OBF变成无效的高电平。acknowledge。

外设响应信号,表示外设已经接收到数据,ack信号有效之后,会使OBF变成无效的高电平。acknowledge。 -

输出缓冲器满信号,表示CPU已经输出了数据。output buffer full

输出缓冲器满信号,表示CPU已经输出了数据。output buffer full -

中断请求信号,请求CPU再次输出数据。

中断请求信号,请求CPU再次输出数据。 -

中断允许触发器

中断允许触发器

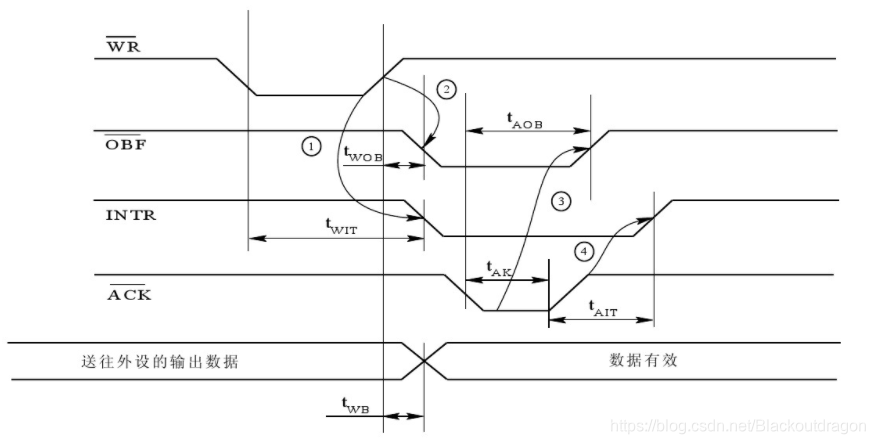

输出时序

- 输出指令写信号下降沿出现后使它变为无效的低电平,简而言之就是关闭中断,对应的是箭头1

- 输出指令写信号的上升沿出现后,将输出缓冲区OBF变为低电平,说明数据已经输出到输出缓冲区

- 当应答信号ACK变为有效低电平的时候,说明外设已经接收到了信号,OBF就可以清空了,没有必要显示为空了,产生了OBF的上升沿,对应就是箭头3

- 接收信号ack的上升沿出现时,说明信号已经完全接受了,所以就会打开中断,接受外部的中断响应。对应的就是箭头4

工作方式2

- 概述:双向选通传送方式

- 适用于双向传送数据的外设

- 书用于查询和中断方式的接口电路

- 注意:

- 方式二只适用于A端口,一个八位的双向端口和一个五位的控制端口

- 输入和输出都可以被锁存,

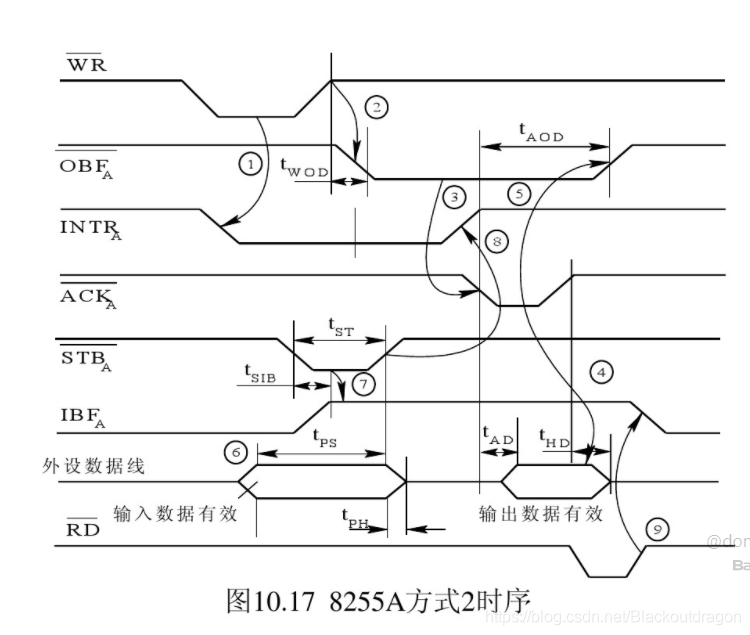

时序图

工作时序相当于方式一的选通输入时和选通输出时的时序的组合

- 读数据时,WR的下降沿使得中断信号intr关闭,屏蔽外界中断,对应的是箭头1

- 读数据的上升沿2,将数据送入到OBF中,OBF处于下降沿,表示数据已经保存到输出缓存区,即输出缓存区已经满了。OBF的下降沿使得ACK的成功接收数据,处于下降沿,处于有效位,对应箭头3

- ack的上升沿,会打开intr的中断,使得中断有效。可以继续接受外部的数据。

- 写数据时,stb低电平有效,送来的数据已经保存在锁存器中,其下降沿使得IBF,输入数据缓冲区产生上升沿,对应的是箭头7

- stb上升沿,打开中断,使得intr高电平有效,同之cpu调用中断处理程序,中断处理程序发出读指令RD,低电平有效,读出IBF中的数据,使得IBF从高电平变为低电平,数据清空,对应箭头9

关于时序的分析与总结

- 地址在读数据以前就一定要稳定,并且前后都要有一定的保险时间,对应的就是CS,A1,A0

- D0~D7表示的是总线上获取的数据,紧紧跟在RD后,RD是在下降沿写入,在上升输出到总线上

- 主要分清两种情况,一种是有外界事件引起的,一种是由当前的状态变化引起的。

本文详细介绍了8255A并行接口芯片的功能,包括其内部结构、端口A、B、C的引脚功能以及与处理器的接口方式。重点阐述了三种工作方式的工作原理和时序图,分别是基本输入输出方式、选通输入输出方式和双向选通传送方式。在时序分析中,强调了数据准备、选通信号、中断请求和应答信号等关键步骤,对于理解8255A如何与CPU及外设交互提供了清晰的指导。

本文详细介绍了8255A并行接口芯片的功能,包括其内部结构、端口A、B、C的引脚功能以及与处理器的接口方式。重点阐述了三种工作方式的工作原理和时序图,分别是基本输入输出方式、选通输入输出方式和双向选通传送方式。在时序分析中,强调了数据准备、选通信号、中断请求和应答信号等关键步骤,对于理解8255A如何与CPU及外设交互提供了清晰的指导。

3430

3430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?